Fターム[2G132AK07]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586)

Fターム[2G132AK07]の下位に属するFターム

排他的論理和を用いるもの (69)

比較判定回路を用いるもの (193)

プルアップ、プルダウンのためのもの (10)

回路分割、分離のためのもの (53)

初期化、同期のためのもの (22)

試験動作制御のためのCPU、論理演算回路 (455)

試験モードへの切替回路 (419)

試験用の入出力回路 (678)

自己診断(BIST等) (359)

Fターム[2G132AK07]に分類される特許

1 - 20 / 1,328

半導体集積回路

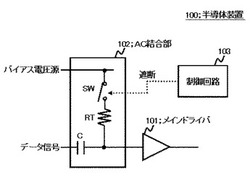

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

ウェハ検査装置及び検査方法

【課題】検査時のプロービングによる不良の疑いのあるチップの流出を確実に防止することのできるウェハ検査装置及び検査方法を提供する。

【解決手段】各チップにプローブを接触させて通電テストを制御するテスト制御手段5と、テスト制御手段5の結果からチップの良否を判定するテスト判定手段6と、各チップのアドレス情報と各チップに対するテスト判定手段6のテスト判定情報及びプローブによるコンタクト情報とを対応させて記憶する記憶手段7と、プローブがチップに接触する毎にチップのアドレス情報に対応するコンタクト情報を更新するコンタクト制御手段8と、コンタクト情報が予め設定した限界条件を超えたときはチップを不良と判定するコンタクト判定手段9とを備える。

(もっと読む)

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

電子部品、測定方法および監視装置

【課題】接合部の損傷を事前に検知する。

【解決手段】電子部品は、第1部材と、第2部材と、接合部と、測定部とを備える。第1電極は、第1部材上に形成される。第2電極は、第1部材上の、第1電極が形成された領域の周囲の領域に形成される。第3電極は、第2部材に形成される。第2電極が第2部材に形成され、第3電極が第2部材の第2電極が形成された領域の周囲の領域に形成されてもよい。接合部は、第1電極と第2電極と第3電極と接合する。測定部は、第1電極および第2電極のうち少なくとも一方を含む接続経路の電気特性を測定する。

(もっと読む)

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

半導体メモリ装置及びそのためのテスト回路

【課題】本発明は、テスト速度を向上させることができる半導体メモリ装置及びそのためのテスト回路に関するものである。

【解決手段】本発明に係る半導体メモリ装置は、複数のメモリセルを含むメモリセルアレイ;データ入出力パッドに接続され、テストモード信号に応じて前記データ入出力パッドに印加されたデータの伝達経路を制御するスイッチング部;ノーマルモード時、前記スイッチング部から伝達されるデータを駆動して、前記メモリセルアレイに書き込むライトドライバ;及び、テストモード時、前記スイッチング部から伝達されるデータを前記メモリセルに伝達するコントローラを含む。

(もっと読む)

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

半導体集積回路の検査方法および半導体集積回路

【課題】半導体集積回路のクロックに一定周波数のクロックのみを供給しつつ半導体集積回路の内部クロックを動的に変化させて半導体集積回路のランダム・ロジックを検査する。

【解決手段】複数の組み合わせ回路と当該複数の組み合わせ回路のスキャンテストを行うためのスキャンチェーンを構成する複数のスキャンフリップフロップとを有する半導体集積回路、の検査方法を、クロック生成装置から前記半導体集積回路に一定周波数の第1クロックを入力する入力工程と、前記半導体集積回路の内蔵する分周器が前記第1クロックを分周して第2クロックを生成する分周工程と、前記複数のスキャンフリップフロップに入力するクロックを、前記第1クロックと前記第2クロックとの間で動的に切り替えつつ前記半導体集積回路を検査する検査工程と、により構成する。

(もっと読む)

半導体装置

【課題】 多様な方式でスキャンテスト経路を形成することができる半導体装置を提供する。

【解決手段】第1チップおよび第2チップを電気的に連結する第1貫通ビアおよび第2貫通ビアと、前記第1チップに配置され、テストデータを受信するとともに前記第1貫通ビアと接続される第1回路部と、前記第1チップに配置され、前記第2貫通ビアおよび前記第1回路部と接続される第2回路部と、前記第2チップに配置され、前記第1貫通ビアと接続される第3回路部と、を含み、前記第1回路部は第1制御信号に応答して前記第1貫通ビアおよび前記第2回路部のうちいずれか一つに前記第1回路の出力信号を出力する。

(もっと読む)

半導体チップ、半導体装置、及びその測定方法

【課題】多数の信号用TSVを有する半導体チップを積層した半導体装置では、個々の信号用TSVを導通試験するのに、膨大な工数がかかっていた。

【解決手段】信号用TSVを直接導通試験するのではなく、信号用TSVに隣接した位置にダミーバンプを配列すると共に、複数の半導体チップ間のダミーバンプを一筆書きで描けるような導通経路で、各半導体チップのダミーバンプを接続する。

導通経路の導通試験により、積層された2つの半導体チップの接合面における接合不良を測定、検出できる。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

ROMテスト時間の短縮方法

【課題】 従来の技術においては、ROM3個分のテスト時間を2個分のテスト時間までしか短縮できないという問題、或いは、加算或いは減算をおこなうため、データビット数の変動の虞があると共に、信頼性が低下する虞があった。

【解決手段】 複数個のROMに書き込まれたデータをテストする場合のROMテスト時間の短縮方法に於いて、複数個のROMの二つずつのROMの出力データのビット毎の比較を行う比較手段を備え、該比較手段の出力を複数個のROMに対応してそれぞれ記憶させ、該複数の記憶手段の出力データに対して、演算の順序が異なる少なくとも二つの異なる内容の演算を行い、該演算結果を期待値と比較することでROMデータを検査する。

(もっと読む)

アナログデジタル変換回路、撮像装置、アナログデジタル変換回路の検査方法

【課題】 カウンタが複数のメモリに共通してカウント信号を供給する列ADCにおいて、カウンタからメモリへカウント信号を伝送する信号経路の不良によって生じる、メモリに供給されるカウント信号の遅延を好適に検出することを目的とする。

【解決手段】 カウント信号の信号値が変化したタイミングに応じて、カウント信号をメモリに保持させるラッチ信号をメモリに供給するテストラッチ信号供給部を有するアナログデジタル変換回路である。

(もっと読む)

集積回路および集積回路の制御方法

【課題】タイミングエラーの種類を判別することができる集積回路を提供する。

【解決手段】エラー測定部は、同期動作回路に入力されているデータ信号が第1の期間内に変化した場合には同期動作回路における第1のタイミングエラーを検出する。また、エラー測定部は、第1の期間の前または後に所定の長さのエラー警告期間を加えた第2の期間内に前記データ信号が変化した場合には同期動作回路における第2のタイミングエラーを検出する。エラー補償制御部は、第1および第2のタイミングエラーがともに検出された場合には第1および第2のタイミングエラーの検出結果の履歴に基づいてタイミングの前後のいずれにおいて前記データ信号が変化したかを判断する。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

高周波モジュールおよび高周波モジュールの検査方法

【課題】高周波回路チップ上の回路と、モジュールを構成する配線基板上の回路についてその相対位置を検出することによって、容易に実装状態が測定できる高周波モジュールおよび高周波モジュールの測定方法を提供する。

【解決手段】入出力端子6を備えた高周波回路チップ1と、高周波回路チップ1の入出力端子6を、バンプ5を介してフリップチップ接続する接続用パッド7を含む配線部を備えた配線基板2とを備えた高周波モジュールであって、入出力端子の2端子間に接続された、スパイラルインダクタ3sと、スパイラルインダクタ3sに対向する位置に配設され、接地電位に接続された検出用導体4dとを備え、接続用パッド間のインダクタンスを測定することによって、スパイラルインダクタ3sと検出用導体4dとの距離の変化に起因する入出力端子6と接続用パッド7間の距離の変化を測定可能に構成される。

(もっと読む)

クロック周波数検出装置

【課題】電子装置において、動作クロックの周波数の異常を、動作クロックを選択的に通過させるフィルタ回路を用いることなく、高精度に検出できるようにする。

【解決手段】PLL回路10にて生成された動作クロックを受けて動作する制御装置2において、動作クロックの周波数の異常判定を行う際には、動作モード切換部32が、半導体メモリ12への書込用電圧を生成するF/V変換回路20のF/V変換特性を、動作クロックの周波数変動に対し出力電圧が略一定となる第1特性から、動作クロックの周波数に対応して出力電圧が変化する第2特性に切り換え、電圧検出部34が、その出力電圧を検出し、周波数異常判定部36が、その検出された電圧値に基づき動作クロックの周波数異常を判定する。

(もっと読む)

1 - 20 / 1,328

[ Back to top ]