Fターム[3K007GA00]の内容

電場発光光源(EL) (25,498) | 回路 (1,376)

Fターム[3K007GA00]の下位に属するFターム

Fターム[3K007GA00]に分類される特許

101 - 120 / 861

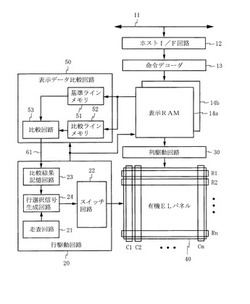

電流駆動型表示装置およびその駆動方法

【課題】デューティー駆動を行う電流駆動型表示装置を長寿命化する。

【解決手段】表示データ比較回路50は、表示RAM14に記憶された表示データの中から、走査回路21で次に選択される行と同じ内容の行を検出する。行駆動回路20は、走査回路21で選択中の行と同じ内容の行が表示データ比較回路50で検出された場合には、選択中の行の行配線に加えて、検出された行の行配線を選択状態に制御する。これにより、有機EL素子に電流が流れる頻度が増加するが、有機EL素子に流れる電流の量が減少するので、高い輝度で発光するほど劣化しやすい有機EL素子の劣化を遅らせることができる。

(もっと読む)

有機強誘電体メモリ

【課題】小型化及び高集積化を図ることができる有機強誘電体メモリを提供する。

【解決手段】有機強誘電体メモリは、複数の画素領域121を有する基板110と、基板110のそれぞれの画素領域121に設けられた画素電極122と、画素電極122が他方の電極144に電気的に接続された第2の薄膜トランジスタ140と、第1の薄膜トランジスタ130を介してデータ線と電気的に接続された第1の電極152、第1の電極152に対向する第2の電極156、第1及び第2の電極152,156の間に設けられた有機強誘電体層154を含む有機強誘電体キャパシタ150と、を含む。有機強誘電体キャパシタ150は、基板110のそれぞれの画素領域121に設けられている。

(もっと読む)

表示装置

【課題】画素回路で正確な回路動作が実行されるようにする。

【解決手段】

画素アレイの同一の側方に配置された2以上の垂直スキャナ部(ライトスキャナ14とドライブスキャナ15)については、各垂直スキャナ部のバッファ部(或いはバッファ部25,35とレベル変換部24,34)がまとめて画素アレイ部20に近い位置に配置されることで、各垂直スキャナ部の走査パルス出力端から上記画素アレイに至るまでの走査線配線長が略同等となるようにする。又は、1つの走査線に対応する垂直スキャナ回路構成部位毎に、垂直方向に並ぶように配置することで、配線長の差を無くす。配線長の差を減少又は解消することで、各垂直スキャナ部からの走査パルスの遅延時間差を、回路動作に影響ない程度に減少したり、或いは解消する。

(もっと読む)

電子装置、電気光学装置および電子機器

【課題】 電気光学素子が駆動される期間を充分に確保する。

【解決手段】 走査線13および基準信号線17との組とデータ線15との交差には単位回路Uが配置される。単位回路Uは、駆動電流Sdrに応じて駆動される電気光学素子35と、入力端Tの電位Vaに応じた時間長にわたって駆動電流Sdrを出力するインバータ34と、入力端Tに接続された第1電極E1と基準信号線17に接続された第2電極E2とを有する容量素子とを含む。複数の走査線13の各々は第1期間ごとに順次に選択され、この選択された走査線13に対応する単位回路Uの入力端Tにデータ電位Vdataが供給される。各基準信号線17には、当該基準信号線17に対応した走査線13が選択される第1期間にて低電位を維持するとともに基準信号線17ごとに相違する第2期間にて経時的に電位が変化する基準信号W[i]が供給される。

(もっと読む)

電子装置、その駆動方法、電気光学装置および電子機器

【課題】 各単位回路の構成を複雑化することなく駆動トランジスタのゲートの初期化を実現する。

【解決手段】 各単位回路Uは、ゲート電位Vgに応じて導通状態が変化する駆動トランジスタTdrと、この導通状態に応じた階調となる電気光学素子11とを含む。初期化期間P1においては、電位供給線17に第1電位Vssが供給されたうえで、この電位供給線17と駆動トランジスタTdrのゲートとが電気的に接続される。これによりゲート電位Vgは第1電位Vssに初期化される。初期化期間P1の経過後の書込期間P2においてはデータ線14と駆動トランジスタTdrのソースおよびゲートとが電気的に接続される。さらに、書込期間P2の経過後の駆動期間P3においては、第1電位Vssとは異なる第2電位Vddが電位供給線17に供給されたうえで、この電位供給線17と駆動トランジスタTdrのソースとが電気的に接続される。

(もっと読む)

膜パターンの形成方法、デバイス、電気光学装置、及び電子機器

【課題】 幅の異なる幾つかの領域を有するパターン形成領域に機能液を配置する場合等において、形成される膜パターン間での膜厚さを無くした該膜パターンの形成方法を提供する。

【解決手段】 基板48上に設けられたバンク34によって区画されるパターン形成領域55,56に、機能液を配置して膜パターンを形成する方法であって、基板48上に、その断面形状が基板側に向けて漸次拡径する逆テーパ状のバンク34を形成するバンク形成工程と、形成したバンクに対して撥液化処理を施す撥液化処理工程と、撥液化処理後、バンク34に区画されたパターン形成領域55,56に機能液を配置する機能液配置工程と、配置した機能液を乾燥させる工程と、を含むことを特徴とする。

(もっと読む)

エレクトロルミネッセンス表示装置

【課題】有機EL表示装置において、外部接続端子を表示装置の側辺に設ける場合の配線を短くする。

【解決手段】表示装置10の左辺に設けられた外部接続端子36は、垂直走査系配線用の端子(V系端子)38、水平走査系配線用の端子(H系端子)40、カソード電源用の端子(CV端子)42、駆動電源用の端子(PVDD端子)44を含む。このうち、H系端子40と、CV端子42と、PVDD端子44の配列を、表示装置の上側から順にH系端子40、CV端子42、PVDD端子44の順とする。また、垂直走査駆動回路24は表示領域14の右辺に隣接して、水平走査駆動回路22は上辺に隣接して、カソード電源用接点34は左辺に隣接して、駆動電流配線27は下辺に隣接して配置される。

(もっと読む)

駆動装置および表示装置ならびに駆動装置および表示装置の駆動方法

【課題】 バスラインの数を減らし製造歩留まりを高くすることが可能な駆動回路および表示装置ならびにそれらの駆動方法を提供すること。

【解決手段】 制御電極と第2電極間の電圧に従った電流を通電する第1のトランジスタと、前記第1のトランジスタの制御電極に電圧を印加する第2のトランジスタと、前記表示素子の一方の電極に電流を通電する第3のトランジスタと、走査信号が出力される第1の電極線と、前記表示素子に電流を通電するための第2の電極線とを有し、前記第2および前記第3のトランジスタの制御電極は前記第1の電極線に接続され、前記第1および前記第2のトランジスタの第1電極は第2の電極線に接続され、前記第3のトランジスタの第1電極は前記表示素子の一方の電極に、第2電極は隣接する前記単位回路の第1の電極線に接続されていることを特徴とする駆動回路。

(もっと読む)

電気光学装置およびその製造方法、電子機器

【課題】 製造プロセスが比較的簡単で製造コストが安価な横電界方式の液晶表示装置等の電気光学装置を提供する。

【解決手段】 本発明の電気光学装置は、一対の基板のうちの一方の基板に、非線形素子(TFD素子43)と、共通電極42(第1電極)と、非線形素子と電気的に接続された画素電極48(第2電極)とが備えられ、第1電極と前記第2電極との間に生じる電界によって電気光学物質層が駆動され、非線形素子が、下部電極44と、下部電極44の上面を覆う上面絶縁膜45と、下部電極44の延在方向に対して両側にあたる2つの側面のうちの片側の側面を覆い、かつ上面絶縁膜45の膜厚よりも小さい膜厚を有する側面絶縁膜46と、少なくとも側面絶縁膜46を介して下部電極と対向する上部電極19とを有している。

(もっと読む)

エレクトロルミネッセンス表示装置

【課題】有機EL表示装置において、外部接続端子を表示装置の側辺に設ける場合の配線を短くする。

【解決手段】表示装置10の左辺に設けられた外部接続端子の一つである駆動電源用の端子(PVDD端子)44を、表示領域14の水平方向に延びる中心線50より下に配置する。画素を駆動するための電流は、表示領域14の下方より延びる配線で供給されるため、PVDD端子44を中心線50より下に配置することで、この配線と外部を接続するPVDD端子44の間の長さを短くできる。

(もっと読む)

表示装置及びその製造方法

【課題】 デバイスとしての性能及び信頼性を向上することができ、しかも、製造歩留まりの良好な表示装置及びその製造方法を提供することを目的とする。

【解決手段】 各画素に配置された第1電極と、各画素の第1電極上に配置された光活性層と、光活性層上に配置された複数の画素に共通の第2電極と、を備えた表示素子40と、第2電極とコンタクトする第1接続端子120と、表示素子40を駆動するのに必要な信号を生成する外部機器とのコンタクトを可能とする第2接続端子130と、を備え、第1接続端子120と第2接続端子130とは、互いに異なる構造を有することを特徴とする。

(もっと読む)

発光表示パネルの駆動装置および駆動方法

【課題】低消費電力化を実現させることができる発光表示パネルの駆動装置および駆動方法を提供すること。

【解決手段】一つの走査に対応する映像データと次の走査に対応する映像データの配列が同一であるか否かを表示データ検知手段4bにより検知し、配列が同一ではないと判定した場合には、ANDゲート6,7を開き、走査ごとにデータドライバ2が動作して、表示パネルに対して走査ごとに異なる表示データを出力する。前記表示データ検知手段4bが、走査ライン毎の映像データの配列が同一であると判定した場合にはANDゲート6,7のゲートを閉じ、データドライバ2におけるラッチ回路2bは、直前の映像データを保持し、表示パネルに対して走査ごとに同一の表示データを出力する。

(もっと読む)

発光装置、その駆動方法および電子機器

【課題】動画ボケおよびフリッカの双方を抑制する。

【解決手段】各画素回路60は、発光素子63をデータ信号Xに応じた輝度に発光させる

。画像処理装置10は、原画像V1から中間画像E1を生成する。データ線駆動回路36は

、奇数行目の各画素回路60に対して原画像V1に応じたデータ信号Xを供給し、偶数行

目の各画素回路60に対して中間画像E1に応じたデータ信号Xjを供給する。発光制御回

路38は、ひとつのフレーム期間Pfの第1期間Pf1において奇数行目の各画素回路60

の発光素子63を発光させ、当該フレーム期間Pfの第2期間Pf2において偶数行目の各

画素回路60の発光素子63を発光させる。

(もっと読む)

発光装置、その駆動方法および駆動回路、ならびに電子機器

【課題】 各発光素子の輝度を高精度に制御する。

【解決手段】 複数の発光素子12の各々は発光電圧Vbの印加によって発光する。電流供給部33は、各発光素子12に対して定電流I0を供給する。特定回路35は、定電流I0が供給されているときの各発光素子12の陽極の電圧Vaに応じた測定電圧を特定する。選択回路313およびバッファ314は、特定回路35が特定した測定電圧に応じた発光電圧Vbを出力する。タイミング制御回路311およびスイッチ315は、バッファ314から出力された発光電圧Vbを、発光素子12に指定された階調に応じた時間密度で当該発光素子12に印加する。

(もっと読む)

有機EL表示装置

【課題】 製造プロセスの複雑化や部材費の高騰を回避でき、高精細で視差の少ないアクティブ駆動型の有機EL表示装置を提供する

【解決手段】 複数の有機EL素子BU,GU,RUをサブピクセルの領域に積層する。積層した有機EL素子に接続される全てのアクティブ素子(薄膜トランジスタTFT)を、絶縁基板SUBとこの絶縁基板に最も近い有機EL素子BUの層との間に形成する。これにより、製造プロセスでの高熱処理で2層目より上の有機EL素子GU,RUがダメージを受けるのを回避でき、有機EL表示装置の長寿命化を図ることができる。また、有機EL素子の間の層間を狭いので、視差を著しく小さくすることができる。

(もっと読む)

表示装置および駆動回路

【課題】 CMOS型構造のシフトレジスタを使用せずにシンプルな構成で且つ低コストで形成可能な駆動回路を有する表示装置を提供する。

【解決手段】 表示装置1は、行電極に走査パルスを印加する一方、走査パルスに同期したデータパルスを列電極を介して表示セルCL,…に供給する駆動回路11,20を有する。駆動回路11,20は、行電極を指定する制御符号を生成しこれをKビット符号に変換する変換回路21と、Kビット符号から順番に関係なく選択されたrビットの組み合わせがそれぞれ割り当てられている行電極に接続されたパルス生成回路221 〜22N ,23とを含む。パルス生成回路221 〜22N ,23は、rビットの組み合わせの各々の解読結果に応じて行電極に走査パルスを印加する。

(もっと読む)

表示装置

【課題】限定的な条件を設定することなく、簡易な構成で電気光学素子の経時的な輝度劣化を補償して表示寿命を延ばすことができる表示装置を提供する。

【解決手段】本表示装置は、互いに直交する複数の走査電極およびデータ電極の交差点近傍にマトリクス状に配置された複数の有機EL素子を含む表示パネル100と、これらの素子に選択的に電流を流す走査電極駆動回路200およびデータ電極駆動回路300と、上記電流を供給する定電圧電源400とを備え、上記走査電極およびデータ電極は所定の配線によりそれぞれ対応する上記駆動回路に接続されている。この配線抵抗を適宜に調節して、並列に接続される有機EL素子の総抵抗値Relallと配線の総抵抗値Rrallとの抵抗比率であるβ’の範囲を0.1≦β≦10とすることにより、簡易な構成で電気光学素子である有機EL素子の表示寿命を延ばすことができる。

(もっと読む)

表示装置、アレイ基板、及び表示装置の駆動方法

【課題】各画素に映像信号として電圧信号を供給すると共に表示する階調を映像信号の大きさで制御する表示装置において、画素毎に階調再現性にばらつきが生じるのを抑制する。

【解決手段】スイッチSWaを開いている選択期間において、ソースが電源端子ND1に接続された駆動トランジスタDRのドレインとゲートとを接続することによりトランジスタDRのゲート−ソース間電圧をその閾値電圧に設定する第1動作と、トランジスタDRのドレインとゲートとの接続を断った状態で、トランジスタDRのゲート電位を変位させることによりゲート−ソース間電圧を閾値電位よりも深い電圧に設定する第2動作と、トランジスタDRのドレインとゲートとを接続することによりゲート−ソース間電圧を変化させる第3動作と、トランジスタDRのドレインとゲートとの接続を断った状態で、トランジスタDRのゲート電位を映像信号に対応した大きさの電圧だけ変位させる第4動作とをこの順に行う。

(もっと読む)

画素回路および表示装置、並びに画素回路の駆動方法

【課題】高輝度時の輝度ばらつきを防止でき、低輝度時の信号書き込み応答性を損わず、画質劣化を防止でき、高品位な画像を表示できる画素回路、表示装置、並びに画素回路の駆動方法を提供する。

【解決手段】画素回路101は電圧信号を電流信号に変換する電圧電流変換回路と、高輝度の電流を参照しこれの複製電流を発生させる電流複製回路を含み、電圧電流変換回路はしきい値Vthと電流の補正をかけるためのキャパシタC111,初期化用のリセットスイッチとしてのTFT112を含み、電流参照用回路はpチャネルTFT111〜113を含んで形成されたカレントミラー回路120を含み、参照された電流の電荷をキャパシタC111に伝達するためのスイッチとしてのTFT115,116を有し、高輝度時の任意の参照電流の複製を行い、電圧電流変換回路に伝達するように構成した。

(もっと読む)

表示装置及びアレイ基板

【課題】ダイオード接続スイッチのオフリーク電流に起因したコントラスト比の低下や輝度ムラを抑制すると共に、表示領域内での素子のレイアウトを容易にする。

【解決手段】本発明の表示装置は、表示色が互いに異なり、各々が、制御端子と電源端子ND1に接続された第1端子とそれらの間の電圧に対応した大きさの電流を出力する第2端子とを含んだ駆動制御素子DRと、第2端子と制御端子との間に接続されたダイオード接続スイッチSWcと、画素電極とこれと向き合った対向電極とそれらの間に介在した活性層とを含んだ表示素子OLEDと、第2端子と画素電極との間に接続された出力制御素子SWaとを備えた画素PX1及びPX2並びに画素PX3を具備し、画素PX1及びPX2のスイッチSWaは1つ又は直列に接続された複数のトランジスタを含み、画素PX3のスイッチSWaは直列に接続された複数のトランジスタを含み、画素PX3は画素PX1及びPX2と比較してスイッチSWaが含むトランジスタの数がより多い。

(もっと読む)

101 - 120 / 861

[ Back to top ]