Fターム[4M104BB04]の内容

Fターム[4M104BB04]の下位に属するFターム

Fターム[4M104BB04]に分類される特許

401 - 420 / 3,070

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

導電性電極パターン及びこれを備える太陽電池

【課題】本発明は、太陽電池の電極として用いられる導電性電極パターンを提供する。

【解決手段】基板100上に上下に配設された下部金属膜及び上部金属膜を含み、該下部金属膜及び該上部金属膜のうちのいずれか一つは銀(Ag)を含み、該下部金属膜及び該上部金属膜のうち他の1つは、該下部金属膜及び該上部金属膜のうちのいずれか一つと異なる遷移金属を含む。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

成膜装置及び成膜方法

【課題】基板表面に形成された高アスペクト比の微細構造内の側面及び底面に、金属層を形成する際のカバレッジに優れた成膜装置及び成膜方法の提供。

【解決手段】微細構造が形成された基板表面4に、スパッタリングによって金属層を形成する成膜装置1であって、基板4と金属層の母材をなすターゲット5とを対向させて、両方を収納する内部空間を有するチャンバー2と、チャンバー2内を減圧する排気手段と、チャンバー2内にスパッタガスを導入するガス導入手段と、ターゲット5のスパッタ面5a前方に磁場を発生させる第一磁場発生手段6と、ターゲット5に負の直流電圧を印加する直流電源7と、ターゲット5から基板4へ向かう方向に磁場Bを発生させる第二磁場発生手段10と、が少なくとも備えられたことを特徴とする成膜装置1。

(もっと読む)

貫通孔を形成しためっき層付シリコン基板

【解決課題】 複数の微細な貫通孔が存在するシリコン基板において、半導体プロセスに依らない簡素な技術により平坦部のみならず貫通孔内部にも密着性が良好な金属膜を成膜して、高密度実装用途に好適なシリコン基板を提供する。

【解決手段】 めっき前処理によりシリコン基板の平坦部と貫通孔内部の清浄シリコン表面を現出させ、ニッケル置換めっき・無電解銅めっき(S4)を順に行うことにより、シリコン基板の全ての貫通孔の内壁全面ならびに主面の全面もしくは一部の面を直接被覆し、密着性に優れ良好な導電性を示す膜を有するめっき層付シリコン基板を作製することができる。

(もっと読む)

スパッタリング方法

【課題】 1μm以上の開口径を有する高アスペクト比のTSVホールHがパターニング形成された処理対象物に対して、被覆性よく成膜できるスパッタリング方法を提供する。

【解決手段】 真空チャンバ1内に処理対象物と、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場を発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、処理対象物に高周波バイアス電力を投入してターゲットからのスパッタ粒子やプラズマ中で電子で電離したイオンを引き込むようにしたものにおいて、前記バイアス電力を、200〜600Wの範囲とする。

(もっと読む)

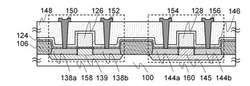

面エピ形状とソース/ドレインの部分的に覆われるシリサイド周辺とに関するフィンフェット

【課題】低い寄生抵抗(例えば、Rpara)および/または高い駆動電流の改善された特性を有するフィンフェットを提供する。

【解決手段】フィンフェット100およびフィンフェットの製造方法が提供される。フィンフェットは、半導体基板106上に、2つまたは複数のフィン102,104と、前記フィンの側面に設けられるエピタキシャル層108,110と、前記エピタキシャル層の表面上を覆うように設けられる金属−半導体化合物112,114とを備える。フィンは、前記半導体基板の表面上に対して実質的に垂直な側面を有する。前記エピタキシャル層は、前記フィンの側面に対して斜角を有して延設される表面を有する。フィンフェットは、前記金属−半導体化合物上に設けられるコンタクト116を含み得る。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板

【課題】静電気による薄膜トランジスタの閾値電圧変動や絶縁破壊短絡を抑制できる薄膜トランジスタ回路基板の製造方法及び薄膜トランジスタ回路基板を提供する。

【解決手段】薄膜トランジスタと、静電気誘導素子と、を基板上に有する薄膜トランジスタ回路基板の製造方法であって、基板に設けられた半導体層の上に、薄膜トランジスタの半導体層のパターンを形成する第1のフォトリソ工程と、静電気誘導素子の半導体層のパターンを形成する第2のフォトリソ工程と、基板に設けられた半導体層をエッチングする工程と、を実施することにより薄膜トランジスタの半導体層及び静電気誘導素子の半導体層を形成し、第1のフォトリソ工程におけるフォトレジストの硬化温度は、第2のフォトリソ工程におけるフォトレジストの硬化温度よりも高いことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

支持体付きメタルマスク装置及びそれを用いた装置の製造方法

【課題】1枚の基板に1枚のメタルマスクを用いる場合のメタルマスクの膨張量を基板の膨張量に近づけて蒸着パターンの位置ズレを防止する。

【解決手段】支持体付きメタルマスク装置100は、半導体基板102の複数のスクライブライン106を物理的に1枚のプレートで覆い、半導体基板と異なる線膨張係数を有し、複数のチップにそれぞれ対応する複数の所定のパターン112を複数の貫通孔として有し、複数の貫通孔を通じて半導体基板に金属を蒸着させる単一のメタルマスク110と、メタルマスクの線膨張係数と半導体基板の線膨張係数との間の線膨張係数、又は半導体基板と同一の線膨張係数を有し、複数のスクライブラインの少なくとも一部のスクライブラインに対応する格子部116を有する支持体114と、一部のスクライブライン内の少なくとも一部の領域において、メタルマスクと支持体とを接続する接合体とを備える。

(もっと読む)

オフセット構造の薄膜トランジスタ

【課題】オフセット構造の薄膜トランジスタを提供する。

【解決手段】ゲート電極と、それぞれゲート電極と一部重畳する第1活性領域及び第2活性領域を備える活性層と、ゲート電極と活性層との間のゲート絶縁膜と、第1活性領域とそれぞれ電気的に連結された第1ソース/ドレイン電極及び第2ソース/ドレイン電極、第2活性領域とそれぞれ電気的に連結された第3ソース/ドレイン電極及び第4ソース/ドレイン電極を備えるソース/ドレイン電極層と、を備えるが、第1ソース/ドレイン電極ないし第4ソース/ドレイン電極のいずれか二つは、ゲート電極と一部重畳し、他の二つは、ゲート電極とオフセットされており、ソース/ドレイン電極の配置は、ソース/ドレイン電極層の中心に対称である薄膜トランジスタである。

(もっと読む)

ドナー元素拡散機能を有する電極形成用ペースト組成物、太陽電池セル、及び太陽電池セルの製造方法

【課題】半導体基板上に不要なn型拡散層を形成させることなく、特定の部分にn型拡散層を形成することが可能で、選択的なn型拡散層形成のためのプロセスを新たに設けることなく、電極を形成する際の熱処理時に、n型拡散層を形成することが可能な電極形成用ペースト組成物、および、該電極形成用ペースト組成物を用いて形成されたn型拡散層及び電極を有する太陽電池を提供する。

【解決手段】n型拡散層形成機能を付与した電極形成用ペースト組成物を、金属粒子と、ドナー元素を含むガラス粒子と、樹脂と、溶剤と、を含んで構成する。また、該電極形成用ペースト組成物を用いて形成した選択的なドナー元素拡散領域131A及び電極133を有する太陽電池セルである。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

p型拡散層形成組成物、並びに、太陽電池セルおよびその製造方法

【課題】結晶シリコン基板を用いた太陽電池セルの製造工程において、シリコン基板中の内部応力、基板の反りの発生を抑制しつつp型拡散層および裏面電極を形成することが可能なp型拡散層形成組成物、および、これを用いて形成された太陽電池セルの提供を提供する。

【解決手段】p型拡散層形成組成物を、金属粒子と、アクセプタ元素を含むガラス粒子と、樹脂と、溶剤と、を含んで構成する。また、半導体基板上に該p型拡散層形成組成物を塗布した後、熱処理することで形成されたp型拡散層および電極を備える太陽電池セルである。

(もっと読む)

電子部品の製造方法及び電解めっき装置

【課題】シード膜の溶解を抑制し、電解めっき後のめっき膜の未析や欠陥の発生を低減する方法を提供する。

【解決手段】実施形態の電子部品の製造方法は、シード膜形成工程S110とめっき工程S114とを備えたことを特徴とする。かかるシード膜形成工程S110では、基体上にシード膜を形成する。そして、かかるめっき工程S114では、窒素ガスでバブリングされているめっき液が供給されためっき槽中の前記めっき液に前記シード膜を浸漬させ、前記シード膜をカソードとして電解めっきを行なう。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】有機TFTは、ゲート電極2および有機半導体層6と、それらの間に位置すると共に有機半導体層6に隣接するゲート絶縁層3とを備えている。このゲート絶縁層3は、スチレンおよびその誘導体のうちの少なくとも一方である第1単量体(α−メチルスチレンなど)と、炭素間二重結合および架橋性反応基を有する第2単量体(メタクリル酸グリシジルなど)とが共重合および架橋された材料を含んでいる。

(もっと読む)

有機FET

【課題】有機FETにおいて、電極から活性層へのキャリア注入効率を向上させること。

【解決手段】有機半導体層3とソース電極5および有機半導体層3とドレイン電極6との間に、電極表面との密着性が良好な界面層4を挿入することで、キャリア注入効率が向上する。

(もっと読む)

半導体素子及び該半導体素子を備える半導体素子構造

【課題】本発明は、かかる事情に鑑み、トランジスタの遮断状態を自然に実現し、半導体領域に金属領域との界面近傍の空乏層の形成を抑制しつつ、ショットキー障壁を実質的に下げることができるようにソース領域のフェルミ準位を選択することにより、駆動電流を増加させる半導体素子及び該半導体素子を備える半導体素子構造を提供することを課題とする。

【解決手段】ソース領域6及びドレイン領域7は、フェルミ準位が異なる第1金属領域10及び第2金属領域11を有し、第1金属領域10は、半導体領域5の価電子帯の頂上のエネルギーレベル以上で且つ半導体領域5の真性フェルミ準位以下のフェルミ準位を有する金属であり、第2金属領域11は、第1金属領域10のフェルミ準位以上で且つ伝導帯の底のエネルギーレベル以下のフェルミ準位を有する金属であることを特徴とする。

(もっと読む)

401 - 420 / 3,070

[ Back to top ]