Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

101 - 120 / 284

半導体装置及びその製造方法

【課題】半導体装置において、微細パターンへのCuの埋め込みを良好にし、且つCuの層間絶縁膜中への拡散を抑制する。

【解決手段】半導体装置は、半導体基板上の層間絶縁膜101に形成されたトレンチ102と、トレンチ102の底部及び側壁を覆うように形成され、白金族元素、高融点金属及び窒素を含有する導電体からなる第1のバリアメタル膜103と、トレンチ102において、第1のバリアメタル膜103上に形成された金属膜105とを備える。

(もっと読む)

薄膜トランジスタアクティブ基板、薄膜トランジスタアクティブ基板の製造方法および電気泳動ディスプレイ

【課題】活性層を保護するとともに、ドレイン電極と画素電極との電気的導通がとれるように保護層を設けた有機トランジスタアクティブ基板を提供する。

【解決手段】薄膜トランジスタアクティブ基板は、基板107上に、ゲート電極101、ゲート絶縁膜108、ソース電極102、ドレイン電極103、活性層109が形成されてなる薄膜トランジスタ上に、保護層としての層間絶縁膜110および画素電極104が形成されてなる。トランジスタ部と上部電極(画素電極104)は層間絶縁膜110に設けられたスルーホール111を介して電気的に導通されてなる。層間絶縁膜110は、樹脂と無機または有機フィラーとを含有し、これらの樹脂と無機または有機フィラーは、EG(エチレングリコール)に、あるいはEGとアルコール溶剤とを組み合わせてなる溶剤に、溶解または分散が可能な樹脂またはフィラーである。

(もっと読む)

導電性酸窒化物および導電性酸窒化物膜の作製方法

【課題】透明導電性酸化物からなる電極は半導体装置の作成工程中に加わる加熱処理により結晶化し易い。結晶化により表面凹凸が大きくなった電極を用いた薄膜素子は、短絡が起こり易く、素子の信頼性が低下してしまう。加熱処理しても結晶化が進まない透光性を有する導電性酸窒化物およびその作成方法を提供することを課題とする。

【解決手段】水素原子を不純物添加したインジウム、ガリウム、及び亜鉛を含む酸窒化物が350℃で加熱しても結晶化しない透光性を有する導電膜であることを見いだし、課題の解決に至った。

(もっと読む)

電子デバイス及びその製造方法

【課題】塗布プロセス(印刷やIJ)により製造が可能であって、電磁波照射による異常放電がなく、生産効率及び生産安定性が高く、かつキャリア移動度及びon/off比が向上した電子デバイス及びその製造方法を提供することにある。

【解決手段】基板上に、電極を有し、少なくとも1部に熱変換材料または熱変換材料を含むエリアと、前記熱変換材料または熱変換材料を含むエリアに隣接もしくは近接して電磁波吸収能を持つ物質または電磁波吸収能を持つ物質を含むエリアを配置し、電磁波を照射して、該電磁波吸収能を持つ物質が発生する熱により、熱変換材料を機能材料に変換する電子デバイスの製造方法において、前記電極の辺が形成する角が全て90°より大きく180°より小さい、または、曲面であることを特徴とする電子デバイスの製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、Al合金膜と透明画素電極を直接コンタクトさせることができるとともに、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液に対する腐食性を改善できるAl合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】Geを0.2〜2.0原子%、および元素群X(Ag、In、Sn、Ni、Co、Cu)より選択される少なくとも1種の元素を含むと共に、希土類元素と高融点金属群(Ti、Ta、V、Nb、Mo、W、Cr、Zr、Hf)からなる元素群Qより選択される少なくとも1種の元素を0.02〜1原子%含み、かつ、粒径が100nmを超える析出物が10−6cm2あたり1個以下であるところに特徴を有するAl合金膜と、該Al合金膜を備えた表示装置。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】金属材料からなるソース電極及びドレイン電極と、酸化物半導体膜とが直接接する薄膜トランジスタ構造とすると、コンタクト抵抗が高くなる恐れがある。コンタクト抵抗が高くなる原因は、ソース電極及びドレイン電極と、酸化物半導体膜との接触面でショットキー接合が形成されることが要因の一つである。

【解決手段】酸化物半導体膜とソース電極及びドレイン電極の間に1nm以上10nm以下のサイズの結晶粒を有し、チャネル形成領域となる酸化物半導体膜よりキャリア濃度が高い酸素欠乏酸化物半導体層を設ける。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】 有機薄膜トランジスタにおいて、ゲート絶縁膜上の電流チャネルにおけるスムーズなキャリアの移動を可能とし、高いキャリア移動度を実現する。

【解決手段】 絶縁性基板10と、絶縁性基板上に形成されたゲート電極11と、ゲート電極11上に形成されたゲート絶縁膜12と、ゲート絶縁膜12上に積層され、ゲート絶縁膜12に接する界面近傍に電流チャネル16を有する有機電子材料膜13と、有機電子材料膜の電流チャネル16に電流を流すためのソース電極15およびドレイン電極14と、を備え、電流チャネル16に流れる電流を制御するゲート電極12が、アモルファス金属よりなることを特徴とする有機薄膜トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】シリコン基板1上に強誘電体キャパシタ37を形成する際、下部電極膜25の上に、アモルファス又は微結晶の酸化導電膜26を形成する。酸化導電膜26を熱処理により結晶化した後、強誘電体膜27の初期層27Aの形成時に酸化導電膜26を還元することにより、結晶粒が小さく且つ配向が整った第2の導電膜26Aを形成する。強誘電体膜27は、MOCVD法により形成し、その初期層27Aは第2の導電膜26Aの結晶配向に倣って成長する。これにより、強誘電体膜27の表面モフォロジが良好になる。

(もっと読む)

金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイス

【課題】 銅等の金属配線の電気抵抗低減および安定化を実現し、銅等の金属配線の信頼性を向上させることが可能な金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイスを提供することである。また、配線構造を形成する過程で配線あるいはデバイス構成材料中に取り込まれた不純物を除去し、配線膜の比抵抗値の上昇を防止し、信頼性を高めることのできる金属配線膜の抽出洗浄方法、抽出洗浄処理された金属配線およびこの金属配線を有するデバイスを提供する。

【解決手段】 半導体ウエハー上にめっき法あるいは気相堆積法により形成された金属配線膜を常圧より高圧の二酸化炭素または不活性の気体ないし流体中に一定時間曝して処理する金属配線膜の抽出洗浄方法、抽出洗浄処理された配線およびこの配線を有するデバイスとした。

(もっと読む)

非晶質基材

【課題】透明電極として、表面平坦性の高い酸化亜鉛基薄膜層が形成された非晶質基材を提供する。

【解決手段】パルスレーザー蒸着法によって、非晶質基材としての溶融石英ガラス基板上に、導電性の酸化亜鉛薄膜を合成する。ターゲットとしてアルミニウムを1%添加した酸化亜鉛焼結体を用いて、高濃度のアルミニウム成分が亜鉛面の表面となる酸化亜鉛の核形成を促すことによって、表面が平坦な亜鉛表面を有する酸化亜鉛薄膜が得られる。この膜はウルツ鉱型の結晶構造を有し、かつ、その表面が亜鉛極性である(0001)面である。

(もっと読む)

アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板の開口率と消費電力とを向上させる。

【解決手段】アクティブマトリクス基板101Aは、透明基板10と、透明基板10上に形成された配線(LG,LD,LP,L1,L2等)と、この配線(LG,LD,LP,L1,L2等)の少なくとも一部を覆う透明半導体層44と、配線(LG,LD,LP,L1,L2等)および透明半導体層44の少なくとも一部を覆う透明な絶縁膜と、を備える。配線(LG,LD,LP,L1,L2等)は、主配線としての第1メタル配線41Mと、これから分岐する副配線としての透明な配線(41,42,43等)と、を含む。主配線としての第1メタル配線41Mは、少なくとも一部が副配線としての配線(41,42,43等)よりも高い導電性を備えた材料を用いて形成される。

(もっと読む)

銅スパッタリングターゲット材及びスパッタリング方法

【課題】成膜条件(成膜中の圧力、成膜に用いるガス種等)を変更しなくても、成膜された銅膜中の引張残留応力を低減できる銅スパッタリングターゲット材及びスパッタリング方法提供する。

【解決手段】本発明に係る銅スパッタリングターゲット材10は、一の結晶方位面と他の結晶方位面とを有し、銅材からなるスパッタ面12を備え、一の結晶方位面は、加速された所定の不活性ガスイオンの照射により他の結晶方位面から弾き出されるスパッタ粒子のエネルギーより大きいエネルギーのスパッタ粒子を放出し、一の結晶方位面と他の結晶方位面との総和に対する一の結晶方位面の占有割合は、15%以上である。

(もっと読む)

半導体素子の製造方法

【課題】半導体基板の損傷を最大限抑制して素子の漏洩電流発生が防止できる半導体素子の製造方法を提供する。

【解決手段】第1のコンタクトホールと、無結晶のポリシリコン膜及びPMD膜26を順次に形成してイオンを注入した後、金属配線を形成することによって、第1のコンタクトホールを用いてコーディングするので、その他のコーディング領域が別に必要でなくチップ面積を縮小することができ、PMDの蒸着前に第1のコンタクトホールを形成するので、半導体基板20の損傷を減らして漏洩電流が減少し、通常のROMコーディングとは反対にOFF特性で反対タイプのイオン注入によりON特性を有するようにし、金属配線の蒸着時に金属配線層の下部にポリシリコン膜が形成されて金属配線の断絶が最小化できる。

(もっと読む)

半導体装置およびその製造方法

【課題】high−k膜を含むFETにおいて、低抵抗金属として高融点金属を用いた場合のイオン注入時のゲートにおけるドーパント突き抜けの問題と、低抵抗金属のグレインサイズの下地依存に起因したPMISトランジスタとNMISトランジスタとのゲート抵抗の差を解決する。

【解決手段】high−k膜4上に形成されるゲート電極を、仕事関数金属膜5とその上部の第一の低抵抗膜6、第二の低抵抗膜7で構成したMISトランジスタにおいて、仕事関数金属膜5上の、タングステンからなる第一の低抵抗膜6のグレインサイズを前記第一の低抵抗膜6上の第二の低抵抗膜7のグレインサイズより小さくする。

(もっと読む)

半導体装置、及び薄膜キャパシタの製造方法

【課題】 下部電極となるTiN膜の表面のラフネスを低減させるために、化学機械研磨、Arによるスパッタリング、Ta膜の堆積等の工程が必要になる。

【解決手段】 半導体基板(10)の上に薄膜キャパシタが配置されている。この薄膜キャパシタは、少なくとも表層部が非晶質または微結晶の金属で形成された下部電極(21a,22a)、該下部電極の上に配置された誘電体膜(23a)、及び該誘電体膜の上に配置された上部電極(24a)を含む。

(もっと読む)

成膜方法

【課題】エポキシ系樹脂等、成膜が困難であった材料上への成膜を可能とするエアロゾルデポジション法を提供すること。

【解決手段】粉末をエアロゾル化し、エアロゾル化した粉末(例えば、Cu粉末)を、硬化前の基板表面(例えば、半硬化状態のエポキシ系樹脂フィルムの表面)に向けて噴射する第1の工程と、前記粉末が固着した前記基板表面を硬化させる第2の工程(例えば、半硬化状態のエポキシ系樹脂フィルムを加熱して熱硬化させる工程)を具備すること。

(もっと読む)

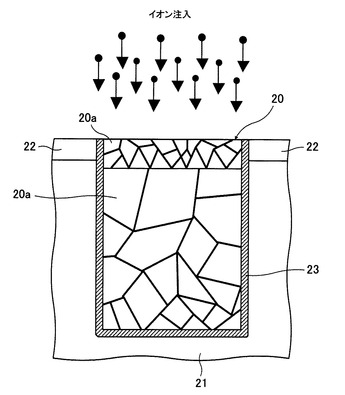

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

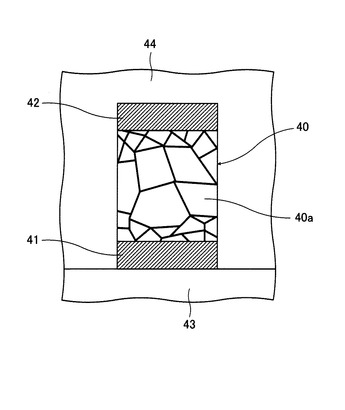

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタ特性を長期安定化して使用することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1上にゲート絶縁膜2を形成する工程と、前記ゲート絶縁膜2上にアモルファスシリコン膜3を形成する工程と、前記アモルファスシリコン膜3に不純物イオン4をイオン注入する工程と、前記アモルファスシリコン膜3を加工することにより、前記ゲート絶縁膜2上にゲート電極3aを形成する工程と、を具備することを特徴とする半導体装置の製造方法。

(もっと読む)

101 - 120 / 284

[ Back to top ]