Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

121 - 140 / 284

表示デバイス

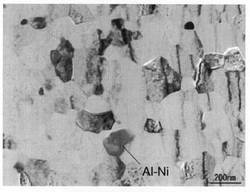

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、アルミニウム合金薄膜と透明画素電極を直接コンタクトさせることができるとともに、低電気抵抗率と耐熱性を両立し、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液やアルカリ性現像液に対する腐食性を改善できるアルミニウム合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】アルミニウム合金薄膜と透明電極との直接コンタクトを可能にするために、Alマトリクス中に、所定の元素を添加するとともに、300℃以下の低温プロセスにおいても透明電極との安定コンタクトを実現し、耐食性を改善するために、アルミニウム中でNi、Ag、Zn、Coとの間に金属間化合物を形成・析出する元素を添加する。これらの金属間化合物のサイズが最大径150nm以下となっているアルミニウム合金薄膜を備えた表示デバイスが提供される。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート酸化膜の信頼性を阻害せずに、ゲート電極の低抵抗化を実現可能な半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、炭化珪素からなり、表面にエピタキシャル結晶成長層2が形成された半導体基板1と、エピタキシャル結晶成長層2上部に選択的に形成されたウェル領域3とを備える。そして、ウェル領域3上部に選択的に形成されたソース領域4と、ソース領域4とエピタキシャル結晶成長層2とに挟まれたウェル領域3の表面を覆うゲート絶縁膜6上に形成されたゲート電極7とを備える。ゲート電極7は、珪素層7aと、炭化珪素層7bとの積層構造からなり、ゲート電極7上部に形成されたシリサイド層7cをさらに備える。

(もっと読む)

ホール形成方法、ホール形成装置及びプログラム

【課題】1回の露光でより多くのホールを形成することが可能なホール形成方法を提供する。

【解決手段】ホール511、512の形成位置となる複数領域の内、一の領域を囲む他の領域のシリコン酸化膜51上に円柱を形成する。具体的には、4以上の複数領域の内、平面視において一の領域を囲む他の領域のシリコン酸化膜51上に円柱を形成する。次いで、シリコン酸化膜51及び円柱上にシリコン窒化膜を形成する。シリコン窒化膜はエッチバックされる。このエッチバックにより円柱を囲むサイドウォール541が形成される。円柱はエッチングされる。最後に、サイドウォール541をマスクにシリコン酸化膜51をエッチングする。これにより一の領域に対応するホール512及び他の領域に対応するホール511が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層を設ける場所に応じて適切な特性を有するシリサイド層を備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、前記ゲート電極上に形成された第1のシリサイド層と、前記ゲート電極下方の前記半導体基板内に形成されたチャネル領域と、前記半導体基板内の前記チャネル領域を挟んだ領域に形成されるソース・ドレイン領域と、前記ソース・ドレイン領域上に形成されて前記第1のシリサイド層よりも結晶粒径の平均値が小さい、または結晶粒内の組成境界数の平均値が多い第2のシリサイド層と、を有する。

(もっと読む)

半導体発光素子及びその製造方法

【課題】発光素子の製造プロセスにおいて、あるいは又、発光素子の動作時、安定した挙動を示す第2電極を有する発光素子を提供する。

【解決手段】発光素子は、n型の導電型を有する第1化合物半導体層11、第1化合物半導体層11上に形成され化合物半導体から成る活性層12、活性層12の上に形成された、p型の導電型を有する第2化合物半導体層13、第1化合物半導体層11に電気的に接続された第1電極15、及び、第2化合物半導体層13上に形成された第2電極14を備えており、第2電極14は、チタン酸化物から成り、4×1021/cm3以上の電子濃度を有し、活性層で発光した光を反射する。

(もっと読む)

電子デバイス用基板及びその製造方法

【課題】配向した窒化タンタル膜が配された電子デバイス用基板及びその製造方法を提供する。

【解決手段】被成膜面1aが(111)配向したシリコンからなる基材1と、Taからなるターゲットと、Ar及びN2からなるプロセスガスとを用いて反応性スパッタリングを行うと、基材1の前記被成膜面1a上に、少なくとも(100)配向した窒化タンタル膜が形成される。前記のことから(100)配向した窒化タンタル膜から構成された電子デバイス用の(111)配向した基板10を提案する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体製造検査装置、および検査装置

【課題】配線幅の変遷に影響されない、表面欠陥を実用可能なレベルよりさらに低いレベルまで低減できる基本的な結晶構造を具備したCu配線を有する半導体装置及びその検査技術を提供する。

【解決手段】半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値27以下の対応(CSL)粒界の割合(頻度)を60%以上とすることにより、表面欠陥を実用可能な現状レベルの1/10以下まで低減できる。または、該半導体装置において、バリア膜及びシード膜を特定すると共に、Cu配線の全ての結晶粒界に占める、粒界Σ値3の対応(CSL)粒界の割合(頻度)を40%以上とすることにより、表面欠陥低減の同様の効果を得ることができる。

(もっと読む)

配線の製造方法

【課題】耐熱性が低い基材上に、ばらつきが少なく、電気抵抗がほぼ均一で、かつ、低抵抗化を実現した配線を製造する方法を提供することを目的とする。

【解決手段】基材上に配置された金属粒子を含む塗布膜に電流を流すことにより前記塗布膜を焼成し、前記金属粒子から形成された配線を得る配線の製造方法が提供される。この製造方法では、前記金属粒子が、金、銀、白金、銅、鉄、パラジウム、スズ、ニッケル、アルミニウム、ジルコニウム、チタンおよびタングステンの金属群から選択された1種の金属、または、前記金属群から選択された2種以上の合金であるのが好ましい。

(もっと読む)

太陽電池電極の製造方法および太陽電池電極

【課題】はんだに対する付着力を向上させたバス電極を、スクリーン印刷を用いて容易に形成可能なバス電極の製造方法を提供することを目的とする。

【解決手段】本発明に係る太陽電池電極の製造方法は、太陽電池のシリコン基板2の主面上に形成され、当該シリコン基板2で発生した電力を取り出すタブ線13とはんだ14により上部が接合されるバス電極12の製造方法であって、(a)シリコン基板2の主面上に、鉛酸化物およびビスマス酸化物を含有するガラスフリットを含む第1の銀ペースト21を印刷する工程を備える。そして、(b)第1の銀ペースト21上に、第1の銀ペースト21のガラスフリットよりも鉛酸化物およびビスマス酸化物の含有割合が低いガラスフリットを含む第2の銀ペースト22を印刷する工程を備える。そして、(c)第1の銀ペースト21および第2の銀ペースト22を焼成する工程とを備える。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】特性劣化を引き起こすゲート電極表面の凹凸が抑えられた、可視光に対して透明な薄膜トランジスタおよびその製造方法を提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、半導体層と、ソース電極と、ドレイン電極と、から少なくとも構成されるボトムゲート型の薄膜トランジスタであって、該トランジスタを構成するすべての部材は、可視光に対して透明であり、該ゲート電極と該ゲート絶縁層との界面において、該界面の垂直方向の凹部と凸部の差は30nm以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

第1および第2の材料のラインの交互配列を有するフローティングゲートの形成方法

【課題】実施容易なフローティングゲートの製造方法を提供する。

【解決手段】少なくとも2つの重合体を備え、かつ、基板3に垂直のラメラ構造を有するダイブロック共重合体層が、基板に形成された第1のゲート絶縁体4に堆積される。そして、ダイブロック共重合体層の重合体のうちの1つは、除去され、並列の溝が共重合体層に形成される。溝は、第1の金属または半導体材料6により充填され、共重合体層の残りは除去される。第2の誘電材料7が堆積され、第2のゲート絶縁体が形成される。そして、フローティングゲートの第2のゲート絶縁体は、それぞれ第1(6)および第2(7)の材料の、並列の第1および第2のラインの交互配列を備えることになり、第2の材料7は、第1の材料のラインを封入することになる。

(もっと読む)

導電膜の形成方法、トランジスタ、および有機エレクトロルミネッセンス素子

【課題】所定の形状に精度よくパターニングすることができる導電膜の形成方法を提供することである。

【解決手段】電気絶縁性を有する被成膜体の表面上に、金属微粒子を含む導電膜用の塗布液を塗布して導電膜用の膜を形成し、被成膜体に塗布された前記導電膜用の膜を第1の温度で加熱し、前記低電気抵抗の導電膜よりも電気抵抗が高い高電気抵抗の導電膜を形成し、前記高電気抵抗の導電膜の一部を除去し、高電気抵抗の導電膜を所定の形状にパターニングし、パターニングされた高電気抵抗の導電膜を第2の温度で加熱して電気抵抗を低下させ、低電気抵抗の導電膜を形成する。

(もっと読む)

制御された結晶構造を用いた、ドーパント及び多層シリコン膜の使用による多結晶シリコン膜及び周囲層の応力の調節

【課題】応力を調整した多層シリコン膜を形成する方法を提供する。

【解決手段】シリコンソースガスを備える第1のプロセスガスを該プロセスチャンバ内に流入させることによって、非晶質シリコン膜406が該基板上に形成される。シリコンソースガスを備える第1のプロセスガス混合物と、H2及び不活性ガスを備える第1の希釈ガス混合物とを第1の温度で堆積チャンバ内に流入させることによって、多結晶シリコン膜408が該非晶質シリコン膜上に形成される。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲルマニウム膜の表面モフォロジを改善し、結晶粒サイズを微小化することを可能とする。

【解決手段】基板上にアモルファスシリコン膜を第1の圧力で成膜する工程と、前記アモルファスシリコン膜の上にポリシリコンゲルマニウム膜を第2の圧力で成膜する工程とを有し、前記第2の圧力に関しては成膜初期圧力は100Pa以上150Pa以下であり、成膜終期圧力は30Pa以上60Pa以下である。

(もっと読む)

薄膜トランジスタ、及び薄膜トランジスタを有する表示装置

【課題】電気特性が優れた薄膜トランジスタ、及びそれを有する表示装置、ならびにそれらを作製する方法を提案する。

【解決手段】ゲート電極上に形成されるゲート絶縁膜と、ゲート絶縁膜上に形成され、ドナーとなる不純物元素を含む微結晶半導体膜と、ドナーとなる不純物元素を含む微結晶半導体膜上に形成される一対のバッファ層と、一対のバッファ層上に形成される一導電型を付与する不純物元素が添加された一対の半導体膜と、一導電型を付与する不純物元素が添加された一対の半導体膜上に形成される配線とを有し、微結晶半導体膜におけるドナーとなる不純物元素の濃度は、ゲート絶縁膜側から前記バッファ層にかけて減少し、バッファ層は、SIMSの検出限界より多くのドナーとなる不純物元素を含まない薄膜トランジスタである。

(もっと読む)

銅配線の製造方法

【課題】極めて微細な孔又は溝内に銅を埋め込むことができる、新たな銅配線の製造方法を提供する。

【解決手段】1価の銅イオンと錯体を形成し、1価の銅イオンとの錯化定数が1×103より高い値を示し、且つ使用環境下において1価の銅イオンと形成する錯体の溶解度が0.5g/L以上の銅錯化剤、若しくは、1価の銅イオンと錯体を形成し、1価の銅イオンとの錯化定数が1×103より高い値を示し、且つ2価の銅イオンとの錯化定数が1×1020以下の値を示す銅錯化剤を1wt%以上と、水を1wt%以上と、銅成分とを含む電解液を強制攪拌しながら、被めっき体における配線接続孔又は配線溝内に銅を電気めっきする工程を備えた銅配線の製造方法によれば、攪拌の程度を調整することにより、微細孔への銅の埋め込み率を調整することができ、微細孔への銅の埋め込み率をより一層高めることができる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】制御ゲートのシリサイド膜の形成時に、シリサイド反応の制御性を高める。

【解決手段】ゲート間絶縁膜6上に形成されたリン(P)が添加された多結晶シリコン膜7と、その上に形成された砒素(As)が添加された多結晶シリコン膜8aと順次堆積し、分断することで制御ゲート電極を形成し、その後制御ゲート電極の上部をシリサイド化する。多結晶シリコン膜8aのグレインサイズは多結晶シリコン膜7のグレインサイズより小さい。このグレインサイズの違いによりシリサイド化がゲート間絶縁膜6まで及ぶことを防止できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

121 - 140 / 284

[ Back to top ]