Fターム[4M104DD17]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744) | 窒化Si (742)

Fターム[4M104DD17]に分類される特許

81 - 100 / 742

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置の製造方法並びにコンタクトホール及び/又はラインの埋め込み方法

【課題】 表面ラフネスの精度をさらに改善でき、コンタクトホールやラインなどの微細化の進展に対応可能なアモルファスシリコン膜を成膜できる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置内部のコンタクトホール5及び/又はラインが形成された層間絶縁膜である下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜4を形成する工程と、を備える。

(もっと読む)

半導体エピタキシャル結晶基板及びその製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エ

ピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、

及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長

炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積

層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】基板表面にシリサイド膜が形成された半導体装置において、ゲート電極パターンの粗密に関わらず、コンタクトの深さの差を緩和する。

【解決手段】半導体装置100は、活性領域(104)に、表面にシリコン酸化膜122aが選択的に形成されたシリサイド膜120aを形成する工程と、その上に、シリコン酸化膜120aとの間でエッチング選択比を有するライナー絶縁膜124を形成する工程と、その上に、ライナー絶縁膜124との間でエッチング選択比を有する絶縁膜(126)を形成する工程と、絶縁膜(126)、ライナー絶縁膜124、およびシリコン酸化膜122aを貫通してシリサイド膜120aに達する第1のコンタクトホール144を形成する工程と、により製造される。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造工程の煩雑化および製造プロセスの長時間化を抑制できると共に、量産性に優れた半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法では、ゲート電極7上に、積層膜19を形成する。そして、層間絶縁膜8形成後、層間絶縁膜8等に対してエッチング処理を施す。これにより、ソース領域3およびp+ベースコンタクト領域5が底面から露出した第1のコンタクトホール12を形成すると同時に、積層膜19が底面から露出した第2のコンタクトホール13を形成する。ここで、当該エッチング処理は、積層膜19のエッチングレートが層間絶縁膜8のエッチングレートよりも遅くなるエッチング条件により、実施する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層4とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜を介してゲート電極7を配置する。さらに、ソース電極5とドレイン電極6との間の電子供給層表面を珪素膜11で被覆する。そして、ゲート電極7に正バイアス印加し、浮遊電極8に電子を蓄積される。

(もっと読む)

成膜方法、成膜装置及び半導体装置の製造方法

【課題】熱CVD法によって、M(BH4)4(Mは、Zr又はHfを意味する)を原料としてM/Zr比が適正範囲内で良質なMBx膜(Mは前記と同じ意味を有し、xは1.8〜2.5の数を意味する)を成膜する。

【解決手段】ガス供給源19から、ガス供給配管15aを介してH2ガスを原料容器21内に供給する。原料容器21内では、導入されたH2ガスとの接触によって、固体原料のZr(BH4)4が気化する。そして、成膜ガスとしてのH2ガスとZr(BH4)4ガスの混合ガスが、ガス供給配管15c,15c1、シャワーヘッド11のガス拡散空間12及びガス吐出孔13を介して処理容器1内に導入され、ウエハW上の絶縁膜の表面を覆うように、ZrBx膜の薄膜が形成される。

(もっと読む)

半導体上からホットメルトエッチングレジストを剥離する改良された方法

【課題】シート抵抗率の増大およびアルミニウム電極の腐蝕を抑制する剥離剤配合物を提供する。

【解決手段】ホットメルトエッチングレジストが、半導体ウェハ上の反射防止コーティングもしくは選択的エミッタに選択的に適用される。無機酸含有エッチング剤を用いて、反射防止コーティングおよび選択的エミッタの露出部分がエッチング除去されて、半導体基体を露出させる。このホットメルトエッチングレジストは次いで、半導体の電気的一体性を悪化させないアルカリ剥離剤を用いて半導体から剥離される。次いで、露出した半導体は金属化されて、電流トラックを形成する。

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

【課題】窒化ガリウム材料デバイスおよびその形成方法を提供する。

【解決手段】該デバイスは、電極規定層24を包含する。電極規定層は典型的にはその内部に形成されたビア26を有し、該ビア内に電極18が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

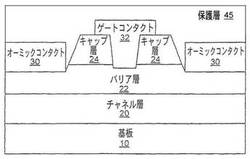

保護層および低損傷陥凹部を備える窒化物ベースのトランジスタならびにその製作方法

【課題】窒化物ベースの半導体チャネル層上に窒化物ベースの半導体バリア層を形成すること、および窒化物ベースの半導体バリア層のゲート領域上に保護層を形成することによって、トランジスタが製作される。

【解決手段】パターニングされたオーム性接触金属領域が、バリア層上に形成され、第1および第2のオーム性接触を形成するためにアニールされる。アニールは、保護層をゲート領域上に載せたままで実施される。バリア層のゲート領域上に、ゲート接点も形成される。ゲート領域内に保護層を有するトランジスタも形成され、バリア層の成長させたままのシート抵抗と実質的に同じシート抵抗をもつバリア層を有するトランジスタも同様である。

(もっと読む)

化合物半導体装置

【課題】窒化物化合物半導体装置において、ゲートリーク電流を抑制する。

【解決手段】化合物半導体装置20は、基板21と、前記基板上方に形成された窒化物半導体よりなるキャリア走行層22を含む半導体積層構造と、前記半導体積層構造上方に形成されたゲート電極26、ソース電極27A、ドレイン電極27Bと、前記半導体積層構造上方であって、ゲート電極とソース電極の間、及び、ゲート電極とドレイン電極との間に形成された絶縁膜28と、前記絶縁膜のうち、ゲート電極とソース電極の間、及びゲート電極とドレイン電極の間に形成された開口と、前記開口に埋め込まれたアルミナ膜29と、を備える。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】窒化物半導体層の表面に形成したオーミック電極のコンタクト抵抗を低減した窒化物半導体装置およびその製造方法を提供すること。

【解決手段】第一の窒化物半導体層3と、第一の窒化物半導体層3の上に形成された第二の窒化物半導体層4と、第二の窒化物半導体層4の表面に形成されるオーミック電極としてのカソード電極6と、を備え、第二の窒化物半導体層4の表面におけるカソード電極6が形成される領域に、凹凸構造を有するコンタクト部4aが形成され、このコンタクト部4aの表面粗さ(RMS)が0.25nm以上5nm以下であり、かつコンタクト部4aの表面の酸素の組成比率が5at.%以下に設定されている。

(もっと読む)

化合物半導体デバイス

【課題】高温にさらされても、Au配線表面に析出物が発生することを抑制できる半導体デバイスの製造方法を提供する。

【解決手段】化合物半導体基板1上の、Auからなる下部配線層3aと上部配線層3bの上部を覆って、Auより薄膜応力が小さく高融点を有する金属であるタンタルあるいはチタンからなる配線被覆層5と5’をスパッタにより形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】サイドウォール間に層間絶縁膜を埋め込むときに埋め込み不良の発生を防止できる半導体装置の製造方法を提供する。

【解決手段】シリコン基板2の表面上に、ゲート酸化膜6、ポリシリコン層(第1ゲート層)9、タングステンシリサイド層(第2ゲート層)10および絶縁層8が形成される。絶縁層8が所定のゲートパターンにエッチングされる。タングステンシリサイド層10が前記所定のゲートパターンにエッチングされる。タングステンシリサイド層10の側壁が後退される。この後、ポリシリコン層9が前記所定のゲートパターンにエッチングされる。ゲート酸化膜6が前記所定のゲートパターンにエッチングされる。

(もっと読む)

81 - 100 / 742

[ Back to top ]