Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

621 - 640 / 644

半導体装置およびその製造方法

【課題】 シリサイド膜を有する半導体装置において配線抵抗を低減し、また配線抵抗のばらつきを低減する。

【解決手段】 コバルトシリサイドあるいはニッケルシリサイドを使う超高速半導体装置において、シリサイド膜形成のためシリコン表面に金属膜を堆積する前に、シリコン表面から自然酸化膜をウェットエッチングプロセスで除去した後、化学酸化膜を形成する。

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電気抵抗化および高信頼性化可能なコンタクトを備え、高速伝送が可能で信頼性の高い半導体装置およびその製造方法を提供する。

【解決手段】 コンタクト20、23を、CVD法を用いて、シリサイド膜19、22、シリコン窒化膜15aおよび第1層間絶縁膜15bの内壁に接する表面に、表面からコンタクト内部方向への距離に応じて窒素含有量が減少する組成勾配を有する窒化タングステン部24を形成し、その内側にタングステンが充填されたタングステン部25を形成する。窒化タングステン部24とタングステン部25との界面の酸化や汚染を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド領域および非シリサイド領域を有する半導体装置において、接合リーク電流を低減する方法を提供する。

【解決手段】第1のトランジスタ10と半導体素子20とを覆うシリコン酸化膜30を形成した後、非シリサイド領域をフォトレジスト4で覆う。この状態でスパッタエッチングを行うことにより、シリサイド領域におけるシリコン酸化膜30のうちサイドウォールスペーサ14を覆う部分の肩部を除去する。その後、異方性ドライエッチングを行うことによりシリサイド領域におけるシリコン酸化膜30のうちサイドウォールスペーサ14の下端部と接する部分以外を除去し、フォトレジスト4を除去した後、ウェットエッチングを行う。その後、非シリサイド領域において残存するシリコン酸化膜30をマスクとして、シリサイド領域に対してシリサイド化を行う。

(もっと読む)

半導体装置の製造方法

【課題】 チップサイズパッケージ型の半導体装置の製造方法において、立体的な構造をもつ半導体基板上に形成する配線層の信頼性の向上を図る。

【解決手段】 半導体基板10の表面に第1の絶縁膜11を介して支持体14を形成する。次に、半導体基板10の一部を当該裏面から選択的にエッチングして開口部10wを形成した後、当該裏面に第2の絶縁膜17を選択的に形成する。次に、開口部10wを含む半導体基板10の裏面の全面に、銀ペーストと溶媒との混合物を、ノズル30aからの噴霧によってスプレー塗布することにより、当該銀ペーストから成る配線層18を形成する。そして、配線層18が形成された半導体基板10をベークし、配線層18を固化する。さらに、配線層18を所定のパターンにパターニングする工程を経る。

(もっと読む)

電子素子の製造方法および電子素子

【課題】 有機半導体層との相性のよい電極を形成した電子素子の製造、及びその製造方法により製造された電子素子を提供する。

【解決手段】 基板上に有機半導体及び/または有機導電体の前駆体の層を形成し、該層を加熱して、有機半導体及び/又は有機導電体の前駆体を有機 半導体及び/または有機導電体とすることにより、パターニングされた電極を形成することを特徴とする電子素子の製造方法、及び該製造方法により製造された電子素子。

(もっと読む)

層構造からなる階段状プロファイルを形成する方法

本発明は層構造(2)からなる階段状プロファイルを形成する方法に関する。第二の構造形成ステップの間に、第一の残りの層構造部分(211)の下側に位置している、第二の層構造部分(22)の領域を、取り除き、第一の残りの層構造部分(211)の第一の突出部(A)を形成し、第三の構造形成ステップの間に、第一の残りの層構造部分(211)の第一の突出部(A)を取り除く。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】本発明は、信頼性の高く、且つしきい値電圧の変化量を高めることが可能な半導体不揮発性記憶素子を有する半導体装置の作製方法を提供する。また、信頼性の高い半導体不揮発性記憶素子を有する半導体装置を、大面積基板を用いて製造する方法を提供する。

【解決手段】本発明は、固溶限界を超えるシリコンを有する固溶体をターゲットとしてスパッタリングを行い、固溶体の主成分である金属元素の導電層と、シリコン粒子とからなる導電膜を成膜した後、金属元素の導電層を除去してシリコン粒子を露出する。また、当該シリコン粒子をフローティングゲート電極とする半導体不揮発性記憶素子を有する半導体装置を作製する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】相対的に高いON電流と、相対的に低いしきい値電圧とを有するMISFETを形成する。

【解決手段】ゲート溝19の内壁に沿って高誘電率膜20を形成し、高誘電率膜20上に相対的に低い温度により酸化する金属膜を積層し、金属膜に不純物をイオン注入した後、相対的に低い温度で金属膜を酸化させて酸化金属膜を形成すると同時に、不純物を高誘電率膜20と酸化金属膜との界面に偏析させる。次いで、酸化金属膜を実質的に全て除去した後、改めて相対的に抵抗の低い金属膜をゲート溝19の内部に埋め込むことにより、金属ゲート24を形成する。

(もっと読む)

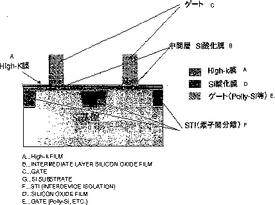

エッチング液及びエッチング方法

本発明は、比誘電率が8以上の膜(High−k膜)とシリコン酸化膜とが表面に形成されたものをエッチング処理するのに好適なエッチング液であって、High−k膜のエッチングレートが2Å/分以上であり、熱酸化膜(THOX)とHigh−k膜のエッチングレートの比が50以下であるものを提供する。前記エッチング液としては、フッ化水素(HF)と種々のエーテル系有機溶媒とを混合したものが好ましく使用される。  (もっと読む)

(もっと読む)

メッキ法による金属パターン形成方法

【課題】 金属集積回路構造を好適に電気鋳造する方法を提供する。

【解決手段】 本発明による方法は、中間絶縁体を貫通するビアまたはラインといった開口部(108)を形成して基板(102)の表面(104)を露出し、中間絶縁体(106)と基板の表面との上にあるベース層(110)を形成し、ベース層の上にあるストライク層(112)を形成し、ストライク層の上にある最上層を形成し、選択的にエッチングすることにより基板の表面の上にある最上層を除去してストライク層(112)の表面を露出し、ストライク層の表面の上にある金属構造(114)を電気鋳造する。電気鋳造された金属構造(114)は、電気メッキまたは無電解堆積プロセスを用いて堆積される。典型的には、この金属はCu、Au、Ir、Ru、Rh、Pd、Os、PtまたはAgである。

(もっと読む)

少なくとも1つの層の構造化方法並びに層から成る構造を備えた電気素子

本発明は、少なくとも1つの構造化された層(10A)を作成するための方法を提供し、その際第1の構造(20A)および第2の構造(20B)を有するマスク構造(20)が基板(5)上に存在している層(10)に生成される。このマスク構造(20)を通して第1の構造(20A)は等方性構造化法を用いてかつ第2の構造(20B)は異方性構造化法を用いて層(10)に移される。本発明の方法により、少なくとも1つの層に唯一のマスク構造を用いて2つの構造(20A,20B)を生成することが可能になる。  (もっと読む)

(もっと読む)

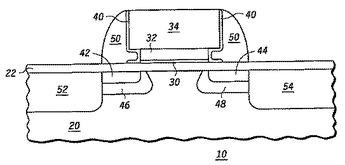

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

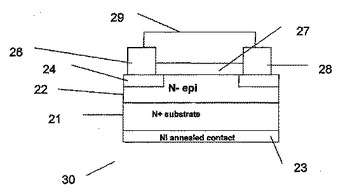

炭化ケイ素上に耐久性接触を有するデバイスおよびその製造方法

ショットキーバリア炭化ケイ素デバイスは、レニウムショットキー金属接触を有している。レニウム接触(27)は250Åよりも厚く、2000Åから4000Åまでの間であり得る。ターミネーション構造は、ショットキー接触の周囲の環状領域をイオンミリングすることによって与えられる。  (もっと読む)

(もっと読む)

シリサイドをソース/ドレインに用いた半導体素子

半導体素子において、非常に深い位置に達するゲルマニウムイオン注入及びゲルマニウムの活性化をニッケルシリサイド形成用のニッケルの堆積の前に行なう。ゲルマニウムを活性化させることにより、イオン注入領域の格子定数が、シリコンであることが好ましい母体基板の格子定数よりも大きくなる。このような変化が加えられた格子によって、ニッケルダイシリサイドの形成を防止することができるという効果が得られる。その結果、ニッケルシリサイドスパイクを防止することができる。  (もっと読む)

(もっと読む)

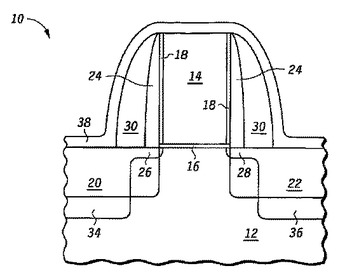

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

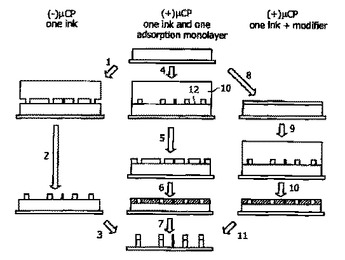

基板上にパターン化層を形成する方法

ソフト・リソグラフィのパターン化工程によって基板(24)上にパターン化された自己組織化単分子層(20)を形成する方法であって、その方法は、a)前記パターン化された自己組織化単分子層(20)の必要なパターンを画定するためのパターン化手段(10)を提供すること、b)前記基板(24)の表面(22)上に自己組織化単分子層(20)を形成すること、c)前記パターン化手段(10)を前記基板(24)の前記表面に適用することであって、前記パターン化手段(10)が前記基板表面の選択された領域に修飾剤を送達するように配置され、前記選択された領域が前記必要なパターン又はそのネガに対応し、前記修飾剤が化学物質を含み、且つ前記選択された領域で、前記自己組織化単分子層(10)の分子と前記基板(24)の前記表面との間の相互作用の強さを変えるように配置されること、並びにd)ステップc)の後、その分子と前記基板の前記表面との間でより低い相互作用の強さを示す前記自己組織化単分子層(20)の領域を選択的に除去又は置換し、それによって前記必要なパターンを有する自己組織化単分子層(20)を形成することを含む。修飾剤は、工程の要求に応じて、自己組織化単分子層の分子と基板の最上面との間の相互作用の強さを弱める又は高めるように選択されてもよい。  (もっと読む)

(もっと読む)

半導体デバイスの製造

基板上に半導体デバイスを製造する方法であり、半導体デバイスは、ウェーハを有する。本発明による方法は、(a)熱伝導性の金属からなる種層をウェーハに付加するステップと、(b)熱伝導性の金属からなる比較的に厚い層を種層上に電気メッキするステップと、(c)基板を除去するステップとを含む。また、それに対応する半導体デバイスが開示される。 (もっと読む)

621 - 640 / 644

[ Back to top ]