Fターム[4M104DD81]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 高エネルギービーム照射 (427)

Fターム[4M104DD81]の下位に属するFターム

界面層、電極層へのITM (52)

Fターム[4M104DD81]に分類される特許

161 - 180 / 375

n型炭化ケイ素基板を少なくとも部分的に除去することによって炭化ケイ素パワーデバイスを作製する方法、およびそのように作製された炭化ケイ素パワーデバイス

炭化ケイ素パワーデバイスが、n型炭化ケイ素基板上でp型炭化ケイ素エピタキシャル層を形成すること、および、そのp型炭化ケイ素エピタキシャル層上で炭化ケイ素パワーデバイス構造を形成することによって作製される。n型炭化ケイ素基板は、p型炭化ケイ素エピタキシャル層を露出するように、少なくとも部分的に除去される。オーミック接触部が、露出されているp型炭化ケイ素エピタキシャル層の少なくとも一部の上で形成される。n型炭化ケイ素基板を少なくとも部分的に除去すること、および、p型炭化ケイ素エピタキシャル層上でオーミック接触部を形成することによって、p型基板を使用することの欠点を低減する、または解消することができる。関連の構造もまた述べられている。  (もっと読む)

(もっと読む)

薄膜半導体装置の製造方法

【課題】良好なシリサイド/シリコン界面の形成、低抵抗のソース・ドレイン領域及びコンタクトの形成、及び急峻な不純物分布の形成を可能とする薄膜半導体素子を製造する方法を提供する。

【解決手段】透明絶縁性基板10上に結晶化半導体膜15を形成し、その上にゲート絶縁膜24及びゲート電極19を形成する。得られた構造の表面に高融点金属膜25を形成した後、前記高融点金属膜25を介してSi又はGeを導入して前記結晶化半導体膜15の表面近傍を非結晶化する。前記ゲート電極19をマスクとして前記結晶化半導体膜15のソース及びドレイン予定領域に不純物を導入した後、熱処理して前記結晶化半導体膜15と前記高融点金属膜25との界面にシリサイド膜を形成する第1の熱処理工程を具備するとともに、前記導入された不純物を活性化し、前記結晶化半導体膜15にソース領域及びドレイン領域を形成する第2の熱処理工程を具備する。

(もっと読む)

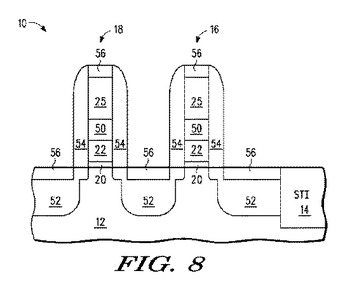

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の完全シリサイド化とソース/ドレイン拡散層の表面シリサイド化とを同時に行うことが可能で、これにより製造工程数を削減して製造コストの低減を図ることが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板1上にpolySiゲート電極7をパターン形成する。次にpolySiゲート電極7脇の半導体基板1の表面層にソース/ドレイン拡散層19を形成する。また、polySiゲート電極7の側壁に絶縁性のサイドウォール21aを形成する。またソース/ドレイン拡散層19の表面に選択的に酸化膜31を形成する。以上の後、酸化膜31で覆われたソース/ドレイン拡散層19上、およびサイドウォール21aが形成されたpolySiゲート電極7を覆う状態で金属膜35を成膜し、熱処理を行うことによってpolySiゲート電極7をフルシリサイド化させると共に、酸化膜31下のソース/ドレイン拡散層19の表面層をシリサイド化してシリサイド層37を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】酸化シリコンより比誘電率の高い酸化物から構成されるゲート絶縁膜上に、金属から構成されるゲート電極を備えたpチャネル型MOSトランジスタおよびnチャネル型MOSトランジスタにおいて、それぞれのしきい値電圧を低減する。

【解決手段】pチャネル型MOSトランジスタQpおよびnチャネル型MOSトランジスタQnのゲート絶縁膜GIが酸化ハフニウムから構成され、pチャネル型MOSトランジスタQpのゲート電極GEPがルテニウムから構成され、nチャネル型MOSトランジスタQnのゲート電極GENがルテニウムを母材としたハフニウムを含む合金から構成されている。

(もっと読む)

PMOSトランジスタ製造方法及びCMOSトランジスタ製造方法

【課題】簡単な工程を通じて優れた動作特性を有するPMOSトランジスタ及びCMOSトランジスタの製造方法を提供する。

【解決手段】 PMOSトランジスタの製造方法において、基板上にゲート酸化膜パターン及び該ゲート酸化膜パターン上に積層されるゲート電極を含むゲート構造物を形成する段階と、前記ゲート構造物に隣接する両側の基板表面下に周期表第3族からなる不純物を注入させて複数の不純物領域を形成する段階と、前記基板の表面及びゲート構造物表面上に不純物拡散防止膜を形成する段階と、前記不純物拡散防止膜上にシリコン窒化膜を形成する段階と、前記不純物領域に含まれる不純物を活性化させながら前記不純物領域間に歪みシリコン領域(strained silicon region)が形成されるように前記基板を熱処理する段階とを有することを特徴とする。

(もっと読む)

半導体装置

【課題】ポリシリコン/メタル積層電極構造のポリシリコン/メタル界面における界面抵抗を低減し、動作速度の低下を防止する。

【解決手段】半導体基板100と、領域N1にチャネル領域102を挟むように形成された拡散層103と、ゲート絶縁膜104と、金属膜105a、105b及びn型ポリシリコン膜105cを含むゲート電極105と、を有するnチャネルMISFETと、領域P1にチャネル領域202を挟むように形成されボロンをドーパントして含む拡散層203と、ゲート絶縁膜204と、金属膜205a〜c及び窒素を含む金属膜205cとの界面部におけるボロン濃度が5E19cm−3以下であるn型ポリシリコン膜205dを含むゲート電極205と、を有するpチャネルMISFETと、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】P型MOSトランジスタにおいて優れたNBTI信頼性が得られ、また、簡易な工程で製造することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】N型MOSトランジスタ4aとP型MOSトランジスタ4bを有する半導体装置において、P型MOSトランジスタ4bのゲート電極6bを、P型ドーパントを含有するポリシリコンを主材料とし、少なくともゲート絶縁膜5との界面近傍にN型ドーパントを含有するように構成する。このような半導体装置は、ゲート絶縁膜5が形成されたNMOSトランジスタ形成領域2a及びP型MOSトランジスタ形成領域2bに、ゲート電極となるポリシリコン層を、N型ドーパントを含有する第1ポリシリコン層とドーパントを実質的に含まない第2ポリシリコン層のスタック構造で形成し、各領域に、それぞれ、N型ドーパント、P型ドーパントをイオン注入する工程を用いて製造できる。

(もっと読む)

パターン化導体、半導体及び誘電体材料のための印刷処理

実施形態は、材料の前駆体を含有するインクから形体を印刷することに関する。該材料には、電気的活性な材料、例えば、半導体、金属、又はそれらの組合せのほか、誘電体を含む。該実施形態は印刷されるライン又はその他の形体の形状、輪郭及び寸法をより正確に制御できる改善された印刷工程条件を提供する。該組成物(複数可)及び/又は方法(複数可)は、インク中の成分の粘度及び質量負荷を増大させてピンニング制御を改善する。典型的な方法は、従って、材料の前駆体と溶媒とを含むインクを該基板上にパターンとして印刷するステップと、該前駆体を前記パターンとして沈殿させてピンニングラインを形成するステップと、該ピンニングラインによって画定されている該材料の前駆体の形体を形成するために、該溶媒を十分に蒸発させるステップと、該材料の前駆体を該パターン化材料に転化するステップとを含む。 (もっと読む)

半導体装置およびその製造方法

【課題】ゲート長によらず、全体がシリサイド化されたゲート電極を有するMOSトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】第1ゲート絶縁膜17上にポリシリコンの第1ゲート電極18を形成し、第2ゲート絶縁膜22上に第1ゲート電極18よりゲート長が大きく且つゲート高さが等しいポリシリコンの第2ゲート電極22を形成する工程と、第2ゲート電極22にシリコン以外のIV属元素またはキャリアを生成しない不活性な元素をイオン注入し、第2ゲート電極22のポリシリコンをアモルファスシリコンに変換する工程と、第1ゲート電極18および第2ゲート電極22上に、シリサイドになる金属膜を形成する工程と、熱処理を施し、第1ゲート電極18および第2ゲート電極22の全体をシリサイド化する工程と、を具備する。

(もっと読む)

絶縁ゲート型半導体装置及びその製造方法

【課題】 絶縁ゲート型半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板1と、半導体基板1上に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜2と、ゲート絶縁膜2上に形成された1原子層乃至2原子層の厚さの多結晶Ge層或いは多結晶Si1-x Gex (x>0.5)層からなるキャップ層3と、キャップ層3上に形成された多結晶シリコンを含むゲート電極4とを有する。

(もっと読む)

ZnCuSe薄膜付き基板およびその製造方法

【課題】基板、特に、有機ポリマー製基板に(Zn1-xCux)Se薄膜を有する薄膜付き基板を提供する。

【解決手段】基板およびこの基板の表面の少なくとも一部に設けられた(Zn1-xCux)Se薄膜(但し、0<x≦0.2)を含むことを特徴とする薄膜付き基板。基板を配設した真空蒸着器内において、ZnSeを加熱し、かつCuSeおよび/またはCu2Seを加熱し、前記基板の表面上に(Zn1-xCux)Se薄膜(但し、0<x≦0.2)を形成することを特徴とする、薄膜付き基板の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、空乏化が抑制され、高速に動作可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成された第1のゲート絶縁膜と、第1のゲート絶縁膜上に形成され、金属元素を含む第1の電極形成膜1007を有する第1のゲート電極とを有する第1のMISFETと、n型活性領域1004の上面に形成された第2のゲート絶縁膜と、第2のゲート絶縁膜上に形成された第2の電極形成膜1010を有する第2のゲート電極とを有する第2のMISFETとを備えている。第2の電極形成膜1010は、第1の電極形成膜1007と同じ金属元素を含み、第1の電極形成膜1007よりも酸素の含有比が高い。

(もっと読む)

配線及び記憶素子の作製方法

【課題】焼成を必要とする液滴吐出法をはじめとする塗布法において、配線や導電膜の作製時における焼成温度を低減することを課題とする。

【解決手段】液滴吐出法等の塗布法を用いて導電性材料よりなるナノ粒子が分散された組成物を吐出し、その後乾燥することで該溶媒を気化させる。そして、活性酸素による前処理を行った後、焼成を行うことで、配線もしくは導電膜を作製する。このように、焼成前に活性酸素による前処理を行うことで、作製時における焼成温度を低減することが可能となる。

(もっと読む)

薄膜トランジスタ製造方法、液晶表示装置製造方法

【要 約】

【課題】ガラス基板から剥離しないゲート電極を形成する。

【解決手段】本発明では、酸素を含有する銅又は銅を主成分とした薄膜である第一の層32をガラス基板11の表面に形成し、第一の層32の表面に、酸素を含有しない銅又は銅を主成分とした薄膜をから成る第二の層33を形成し、第一の層32と第二の層33の二層構造の銅を主成分とする配線膜13を形成しており、銅を主成分とする配線膜13を窒素プラズマで処理した後、その表面に窒化ケイ素薄膜(例えばゲート絶縁膜14)を形成している。窒化ケイ素薄膜を形成する際のシランガスの影響が、ガラス基板11の界面に及ばないので、銅を主成分とする配線膜13から成るゲート電極15や蓄積容量電極12がガラス基板11から剥離しない。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、ゲート電極のトリミングを良好に実施できるように、また、レジストトリミングを行ってもレジスト倒れやレジスト変形が発生しないように、更に、従来のトリミングがプラズマエッチングで実施されていることに起因する問題を解消し、更にまた、ゲート電極のトリミングに関連してサイドウォールの形成時にSTI部が過剰に損傷されないようにしようとする。

【解決手段】金属を含む材料である金属シリサイド或いは金属単体から成るゲート電極をもつ半導体装置を作製する工程に於いて、ゲート電極14Gのエッチング後にゲート部の表面を酸化させ、ゲート部を有機酸を含むガス状物質に曝露すると共に加熱して金属と有機酸との反応生成物を揮発させてゲート電極14Gのトリミングを行う。

(もっと読む)

電極の絶縁方法、及び絶縁電極対を有するナノワイヤベースのデバイス

絶縁された電極を作成し、それらの電極間にナノワイヤを組み込む(600)方法(100)はそれぞれ、半導体層(210)上の半導体材料の横方向エピタキシャル過成長を使用して、同一結晶方位を有する絶縁電極(260、270)を形成する。この方法(100、600)は、半導体層上の絶縁膜(240)内の窓(242)を介した半導体機構要素(250)の選択的エピタキシャル成長(140)を含む。垂直ステム(252)は、窓を介して半導体層と接触し、レッジ(254)は、絶縁膜上の垂直ステムの横方向エピタキシャル過成長である。この方法は更に、半導体機構要素と半導体層から1対の絶縁電極(260、270)を作成(160)することを含む。ナノワイヤベースのデバイス(800)は、1対の絶縁電極と、1対の絶縁電極のそれぞれの表面間を架橋するナノワイヤ(280)とを含む。 (もっと読む)

金属微粒子分散液およびそれを用いた配線断線部の修正方法

【課題】回路基板と導電性の金属薄膜との密着性に優れ、再剥離する虞なく回路基板の配線に発生する断線部を修正する。

【解決手段】回路基板上に形成された配線の断線部を修正する修正用の金属微粒子分散液で、金、銀、白金、パラジウムのうちいずれか一種類以上の金属微粒子を含有するとともに、アルミニウム、ニッケル、銅のうちいずれかのアセチルアセトナート基を配位子とする金属錯体を前記金属微粒子の金属量に対し、3重量%ないし30重量%含有するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性の高いフルシリサイドMOSFETおよびシリサイドMOSFETを従来よりも簡単に同一基板上に形成することができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上にゲート絶縁膜30を形成し、ゲート絶縁膜上に第1のゲート電極40および第2のゲート電極42を形成し、第1のゲート電極および第2のゲート電極上にマスク材料90を堆積し、第2のゲート電極を被覆したまま第1のゲート電極の上面を露出させるようにマスク材料をパターニングし、マスク材料を利用して第1のゲート電極の上部をエッチングし、マスク材料を除去し、第1のゲート電極および第2のゲート電極上に金属膜100を堆積し、第1のゲート電極の全部および第2のゲート電極の上部をシリサイド化することを具備する。

(もっと読む)

半導体装置の製造方法

【課題】溝ゲート構造を有するトランジスタとプレーナゲート構造を有するトランジスタを同一基板上に有する半導体装置であって、ゲート電極構造をポリメタルゲート構造とし、溝ゲートとプレーナゲートとを異なる導電型としたデュアルゲート構造としても、溝ゲートのポリシリコンに十分なドーパントを導入して空乏化を防止し、一方、プレーナゲートも同じ層厚のポリシリコンでも不純物イオンのゲート絶縁膜突抜けが起こらない新たな製造方法を提供する。

【解決手段】溝ゲート用のシリコン層にイオン注入し、その後一旦ポリシリコン化し、再度イオン注入によりポリシリコン層の表面をアモルファス化(層9,10)して、プレーナゲート用の異なる導電型のイオン注入を行う。

(もっと読む)

161 - 180 / 375

[ Back to top ]