Fターム[4M104DD81]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 高エネルギービーム照射 (427)

Fターム[4M104DD81]の下位に属するFターム

界面層、電極層へのITM (52)

Fターム[4M104DD81]に分類される特許

121 - 140 / 375

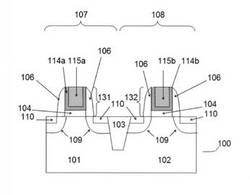

二重仕事関数半導体デバイスの製造方法及びそのデバイス

【課題】金属ゲート電極を有する二重仕事関数半導体デバイスの製造方法を提供する。

【解決手段】該製造方法は、第1領域101及び第2領域102を有する基板100を設けること、第1領域に第1半導体トランジスタ107を作製すること、第2領域に第2半導体トランジスタ108を作製すること、第1サーマルバジェットを第1半導体トランジスタに備わる少なくとも第1ゲート誘電体キャッピング層114aに作用し、第2サーマルバジェットを第2半導体トランジスタに備わる少なくとも第2ゲート誘電体キャッピング層114bに作用すること、を備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】トランジスタのチャネルに応力を与えるストレスライナーとして機能するシリコン窒化膜を形成した場合に、クラックの発生を抑えることができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体基板1に形成されたnチャネル型トランジスタ20を覆い、nチャネル型トランジスタ20のチャネルに対してチャネル長方向の引張応力を作用させるシリコン窒化膜11、12を形成する半導体装置の製造方法であって、nチャネル型トランジスタ20の上に一層目のシリコン窒化膜11を形成する工程と、一層目のシリコン窒化膜11に紫外線を照射する工程と、紫外線照射の後、一層目のシリコン窒化膜11の上に一層目のシリコン窒化膜11よりも薄いシリコン窒化膜12を少なくとも一層以上形成する工程とを備え、引張応力を作用させるシリコン窒化膜を複数段階に分けて形成する。

(もっと読む)

相補型p、及びnMOSFETトランジスタの製造方法、このトランジスタを包含する電子デバイス、及び少なくとも1つのこのデバイスを包含するプロセッサ

ゲート電極(14、28)によって制御されるチャネル(20、34)によって接続される金属ショットキーのソース電極(10、24)、及びドレイン電極(12、26)を有する相補型p、及びnMOSFETトランジスタ(3、4)を製造する方法であって、p、及びnトランジスタの双方のための単一のシリサイドからソース電極、及びドレイン電極を製造することと、相補型nトランジスタ(4)をマスクして、シリサイドと、pトランジスタのチャネル(20)との間の界面(22)における周期表のII族、及びIII族からの第1の不純物(21)を偏析することと、相補型pトランジスタ(3)をマスクして、シリサイドと、nトランジスタのチャネル(34)との間の界面(36)における周期表のV族、及びVI族からの第2の不純物(35)を偏析することと、を有する。 (もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

銅表面上への選択的コバルト堆積

本発明の実施形態は、露出誘電表面を覆う銅表面上にコバルト層を選択的に形成するプロセスを提供する。一実施形態では、前処理プロセスの間に金属銅表面を形成している間は処理チャンバー内の基板の汚染された銅表面を還元剤にさらすステップと、気相堆積プロセスの間に基板上の誘電表面を露出したままにしながら金属銅表面を覆ってまたは上にコバルトキャッピング層を選択的に形成するために基板をコバルト前駆体ガスにさらすステップと、コバルトキャッピング層および誘電表面を覆ってまたは上に誘電障壁層を堆積させるステップとを包含する、基板上の銅表面をキャッピングするための方法が、提供される。別の実施形態では、堆積−処理サイクルは、気相堆積プロセスを実行した後に後処理プロセスを実行するステップを包含し、その堆積−処理サイクルは、複数のコバルトキャッピング層を形成するために繰り返されてもよい。  (もっと読む)

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】膜厚バラツキを抑制し、かつドライエッチングダメージの発生を抑制できる優れた素子特性を兼ね備えた薄膜半導体装置及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極、前記ゲート電極の側壁に形成された、低温酸化膜、低温窒化膜及び低温酸化膜の3層構造のサイドウォールスペーサー、及び島状半導体層及びゲート電極を覆う層間絶縁膜を具備することを特徴とする。

(もっと読む)

金属膜パターンの製造方法

【課題】金属微粒子分散体の基板への塗布と加熱処理による焼結とにより基板上に形成される金属膜からなる金属膜パターンの焼結性を向上させ、さらに金属膜パターンと基板との密着性を向上させることができる金属膜パターンの製造方法を提供する。

【解決手段】基板表面上に金属微粒子分散体を塗布する工程と、前記金属微粒子分散体を乾燥して金属膜前駆体を形成する工程と、前記金属膜前駆体にエネルギー線を照射して金属膜化領域を形成する工程と、誘導加熱法による加熱により前記金属膜化領域の近傍の前記金属膜前駆体をさらに金属膜化する工程と前記金属膜前駆体を除去する工程とからなる。

(もっと読む)

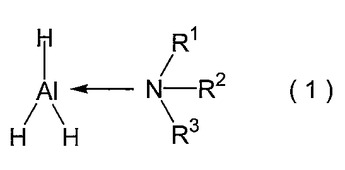

アルミニウム膜形成用組成物及びアルミニウム膜の形成方法

【課題】長期保存安定性及びラフな不活性雰囲気下における取り扱い性に優れる塗布型のアルミニウム膜形成用組成物を提供すること。

【解決手段】上記アルミニウム膜形成用組成物は、下記式(1)で表される錯体に代表される特定の錯体を含有する。

(式(1)中、R1は炭素数9〜20のアルキル基、アルケニル基もしくはアルキニル基又は炭素数7〜20の脂環式基であり、R2及びR3は、それぞれ独立に、水素原子、炭素数1〜20のアルキル基、アルケニル基若しくはアルキニル基又は炭素数3〜20の脂環式基である。)

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率ゲート絶縁膜/多結晶シリコン界面におけるダイマーの発生を既存の製造工程になじみやすい工程により抑制して、フェルミレベルピンニングを除去する。

【解決手段】 半導体基板上方に形成されたHf、Zr或いはAlの少なくとも一つと酸素とを含むゲート絶縁膜とシリコンを含むゲート電極との間に、炭素を含むキャップ層を設ける。

(もっと読む)

二座アミン安定化金属ナノ粒子

【課題】低コストで、低温でアニール可能であり、十分な貯蔵寿命を有する、安定な金属ナノ粒子組成物を提供する。

【解決手段】金属ナノ粒子の外面に会合した二座アミン安定剤を含む、二座アミン安定化金属ナノ粒子。また、分散された金属ナノ粒子の溶液を供給し、二座アミン安定化金属ナノ粒子分散液を基板上に堆積し、印刷された基板を加熱して基板の表面上に導電性構造部を形成して、基板上に導電性構造部を形成する方法。

(もっと読む)

電子素子とその製造方法

【課題】ショットキー障壁を生じさせず,所望する電気伝導特性を有する電子素子及び電子素子の製造方法を提供することを課題とする。

【解決手段】本発明に係る電子素子では,離間されて配置された一対の電極102と,電極102間それぞれに接続され,半導体的性質を有する半導体ナノワイヤ101とを備え,電極102が,ナノワイヤ101と同一の材料又は同一の半導体的性質を有する材料からなることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 ゲート電極とドレイン領域間のリーク電流の増加を抑制する。

【解決手段】 半導体基板上にゲート酸化膜を介してゲート電極を形成する工程と、ゲート電極に第1の不純物を注入し、ゲート電極をマスクとして半導体基板に第1の不純物を注入する第1の不純物注入工程と、第1の不純物を活性化させる第1の熱処理を行う工程と、ゲート電極のゲート絶縁膜から離間させた位置に第2の不純物を注入する第2の不純物注入工程と、第2の不純物を含有する領域を活性化する形成する第2の熱処置を行う工程と、を含み、第1の不純物はリンからなる。

(もっと読む)

光熱作用を利用した基板の表面構造の製造方法

【課題】光熱作用を利用して基板の表面の大きな区域にミクロ・ナノ構造を簡単、低価格に直接製造できる基板の製造方法。

【解決手段】基板表面に複数のナノ粒子を配布し、特定波長のレーザー光を照射すると、レーザー光の光エネルギーにより基板の表面のナノ粒子を励起し、光エネルギーが熱エネルギーに変換される。その結果、基板上の表面構造は励起されたナノ粒子の熱エネルギーにより形成される。これにより、既定のパターンの層を持つ基板が形成される。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】特性劣化を引き起こすゲート電極表面の凹凸が抑えられた、可視光に対して透明な薄膜トランジスタおよびその製造方法を提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、半導体層と、ソース電極と、ドレイン電極と、から少なくとも構成されるボトムゲート型の薄膜トランジスタであって、該トランジスタを構成するすべての部材は、可視光に対して透明であり、該ゲート電極と該ゲート絶縁層との界面において、該界面の垂直方向の凹部と凸部の差は30nm以下であることを特徴とする薄膜トランジスタ。

(もっと読む)

金属膜積層体、及びその製造方法、並びにそれを用いた金属配線基板

【課題】本発明の目的は、金属微粒子分散体の基板への塗布と加熱処理による焼結により基板上に形成される金属膜の基板との密着性の向上を図り、耐環境性を向上させると共にメッキ下地膜などにも利用出来る金属膜積層体、及びその製造方法、並びにそれを用いた金属配線基板を提供する。

【解決手段】本発明の金属膜積層体は、有機金属化合物から形成される金属酸化物膜と金属微粒子分散体から形成される金属膜とを基板上に複数層積層し、基板上に形成される最初の膜は金属酸化物膜であることを特徴とする。

(もっと読む)

不安定化剤を用いて金属ナノ粒子から安定剤を除去する方法

【課題】本発明の目的は、基板上に導電性特徴部を形成するための方法および安定剤により安定化される金属ナノ粒子を用いる薄膜トランジスタを製造するための方法を提供することにある。

【解決手段】本発明は、基板上に導電性特徴部を形成するための方法および安定剤により安定化される金属ナノ粒子を用いる薄膜トランジスタを製造するための方法であって、その安定剤、不安定化剤、およびその他の反応副生成物を、1)例えば約180℃より低い低温での熱アニール、または2)該基板を溶媒で洗浄することによって除去することができるようにし、それによって広範な基板上に金属特徴部を形成するために使用することができる方法である。

(もっと読む)

高性能表示装置とその製造方法

【課題】アクティブマトリックス型表示装置の製造プロセスを短縮化し、投資効率、生産効率と生産歩留りを向上させ、かつ大幅なアクティブマトリックス素子の高性能化を実現する。

【解決手段】アクティブマトリックス型薄膜トランジスタ素子基板の製造工程において、ゲート電極をパターンニング後、ゲート絶縁膜を成膜する。

次に半導体層としてポリシリコン半導体層を成膜後アモルファスシリコン半導体層を真空をやぶらずに連続成膜する。その後n+アモルファスシリコン半導体層を成膜してから、映像信号配線とドレイン電極を形成するための金属電極層を成膜する。その後、ホトリソグラフィー工程で、薄膜トランジスタ素子のチャネル領域の露光光量を変調可能なホトマスクを用いて、薄膜半導体層の素子分離形成と映像信号配線とドレイン電極の形成を1回のホトリソグラフィー工程で同時に形成する。

(もっと読む)

集積回路の配線形成方法

【課題】 半導体集積回路等の微細な集積回路の修正等を行う際、配線を低抵抗で形成することができる集積回路の配線形成方法を提供する。

【解決手段】 集積回路2上の配線を必要とする部分2cxを集束イオンビーム10aにより掘出す工程と、掘出し工程によって掘出された部分に対し、銀40をコートした走査トンネル顕微鏡探針21に電圧パルスを印加して該探針から銀原子を移動させる走査トンネル顕微鏡法により、銀配線4cを形成する工程とを有する集積回路の配線形成方法であって、配線を必要とする部分の線幅が1μm以下である場合は走査トンネル顕微鏡法を用い、線幅が1μmを超える場合は、集積回路上の配線を必要とする部分に対し、非サーマル方式のインクジェット装置から銀粒子を含むインクを噴射した後に、レーザー又は加熱した走査プローブ顕微鏡の探針でインクを乾燥させるインクジェット法により銀配線を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】LDD領域がゲート電極の下部とオーバーラップするのを防止し、素子のパフォーマンスを向上させるようにした半導体素子及びその製造方法を提供する。

【解決手段】STI領域及びゲート領域が定義された下部構造物において、前記STI領域の内部に素子隔離膜を、前記ゲート領域の内部に犠牲層を形成する段階と、前記素子隔離膜及び前記犠牲層をバリア(barrier)とし、前記素子隔離膜と前記犠牲層との間にLDD領域を形成する段階と、前記ゲート領域の内部に形成された前記犠牲層を選択的に除去する段階と、前記犠牲層が除去された前記ゲート領域の内部側壁にスペーサを形成する段階と、前記犠牲層が除去された前記ゲート領域の内部下側にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜の上部にゲート電極を形成する段階と、前記LDD領域の上部に接合領域を形成する段階と、前記LDD領域を前記ゲート領域の下部両側端まで拡散させる段階と、を含む。

(もっと読む)

121 - 140 / 375

[ Back to top ]