Fターム[4M104DD81]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 高エネルギービーム照射 (427)

Fターム[4M104DD81]の下位に属するFターム

界面層、電極層へのITM (52)

Fターム[4M104DD81]に分類される特許

61 - 80 / 375

銀超微粒子含有組成物および導電性パターン作製方法

【課題】焼結工程および浸漬処理が不要であり、優れた導電性が得られる銀超微粒子含有組成物および導電性パターン作製方法を提供する。

【解決手段】水性媒体中に、平均粒径が0.1μm以下の銀超微粒子、ポリマーラテックス、および水溶性ハロゲン化物を含有することを特徴とする銀超微粒子含有組成物。およびこの銀超微粒子含有組成物を基材表面に塗布・乾燥させることによりパターンを作製し、該パターンに紫外線の照射および/または水分の再付与を行う導電性パターン作製方法。

(もっと読む)

接続されたナノ構造体及びそのための方法

種々の材料及びアプローチの1以上を用いてナノ構造体を接続する。種々の例示的実施形態で、ナノ構造体間の接続部で2つ以上のナノ構造体が接続される。ナノ構造体は、接続部で接触するかほぼ接触してよく、接続材料を接続部で堆積及び核形成させてナノ構造体同士を結合する。種々の用途で、核形成した接続材料はナノ構造体間の伝導率(熱的及び/又は電気的)を向上させる。いくつかの実施形態では、接続材料は更に、例えばナノ構造体に沿って成長することにより及び/又はナノ構造体にドープすることにより、ナノ構造体自身の伝導率を上昇させる。  (もっと読む)

(もっと読む)

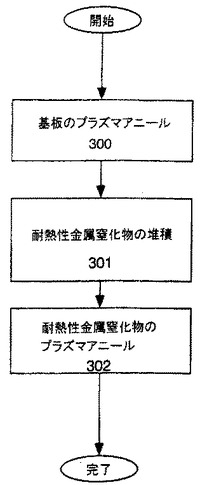

密着性を改良するための基板のプラズマアニーリング

【課題】許容可能な拡散バリア特性と基板への密着性を耐熱性金属窒化物が有するように、基板上への窒化チタンなどの耐熱性金属窒化物膜の形成を提供する。

【解決手段】材料の層が、ウェハ上に部分的に形成された集積回路内の基板上に形成される。基板はプラズマアニールを受け、その間に基板はイオンでボンバードされる(工程300)。プラズマアニールは、エネルギーを注入された窒素含有ガスから生成されたプラズマへ基板を曝すことにより実行できる。基板がプラズマアニールされた後、耐熱性金属窒化物の層が基板上に堆積される(工程301)。耐熱性金属窒化物の層は、次に、第1セットのイオンでボンバードされる。第1セットのイオンによる耐熱性金属のこのボンバードは、プラズマアニールを実行することにより達成できる。耐熱性金属窒化物は、更に、第2セットのイオンによりボンバードされる(工程302)。

(もっと読む)

成膜装置、成膜方法及び記憶媒体

【課題】真空容器内にて反応ガスによりチタンナイトライド膜を形成するにあたり、当該チタンナイトライド膜を速やかに成膜すると共に、表面形状が平滑なチタンナイトライド膜を得ること。

【解決手段】チタンナイトライド膜の成膜処理を行う時に、回転テーブル2と各ガスノズル31、32、41、42とを100rpm以上で相対的に回転させることによって、反応ガスの供給サイクル(反応生成物の成膜サイクル)を高速で行うことができるので、薄膜を速やかに形成することができ、またサイクル間の時間が極めて短いので、基板の表面に生成した反応生成物の結晶化による粒子径の粗大化が進行する前に次の反応生成物の層を上層側に積層して平滑な表面を得ることができる。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置とその製造方法

【課題】製造コストを低く、炭化珪素基板の裏層部に、電極形成用の複数の溝を形成する半導体素子の製造技術を提供する。

【解決手段】炭化珪素基板13の裏層部の転移の存在する箇所に対応して、複数のエッチピット24をウエットエッチングにより形成する。炭化珪素基板とオーミック接触するカソード電極32をスパッタ法により形成する。炭化珪素基板13の表層部にp層16を形成し、アノード電極34をスパッタ法により形成し、ジャンクション・バリア・ショットキーダイオードとする。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】製造工程を簡略化しつつソース電極及びドレイン電極の導電性を向上させた薄膜トランジスタ及びその製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、基板101上にゲート電極103を形成する工程と、ゲート電極103上にゲート絶縁層104を形成する工程と、ゲート絶縁層104上にアモルファスシリコン層105を形成する工程と、アモルファスシリコン層105上にアルミニウム層111を形成し、アルミニウム層111上にモリブデンタングステン層112を形成し、アルミニウム層111及びモリブデンタングステン層112を少なくとも含む積層体から構成されるソース電極109及びドレイン電極110を形成する工程と、ソース電極109及びドレイン電極110をマスクとしアモルファスシリコン層105にレーザを照射することでアモルファスシリコン層105の一部を結晶化させチャネル領域を形成する工程とを含む。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】カーボン膜の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化できるようにする。

【解決手段】オーミック電極5を形成するための金属層15の形成前にレーザ光の吸収効果の高いカーボン層14を形成しておき、その上に金属層15を形成してからレーザアニールを行うようにしている。これにより、金属層15を構成する金属がカーボン層14を構成する炭素(C)やn+型基板1を構成するシリコン(Si)または炭素と反応してオーミック電極5が形成されるため、カーボン層14を除去する必要がない。また、レーザアニール時にカーボン層14を用いているため、レーザ光の吸収率を高くすることができ、オーミック電極5のコンタクト抵抗の低抵抗化を十分に行うことが可能となる。したがって、カーボン膜14の除去が必要とならず、かつ、十分にコンタクト抵抗を低抵抗化することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板の内部であって、活性領域と素子分離領域との境界領域にコンタクトホールが形成された場合に、基板に流れるリーク電流を抑制できるようにする。

【解決手段】半導体基板10の上部に形成された素子分離領域10a及び活性領域10bと、半導体基板10の上に形成された絶縁膜12と、絶縁膜12に少なくとも活性領域10bを露出するように形成され、且つ、素子分離領域10aにおける活性領域10bとの境界領域を含む領域に形成されたコンタクトホール13と、コンタクトホール13における、活性領域10bの上に位置する第1の底面の上に形成された第1のバリアメタル膜14と、コンタクトホール13における、最下端に位置する第2の底面と第1の底面とをつなぐ壁面上に形成された第2のバリアメタル膜17とを備える。第2のバリアメタル膜17は、第1のバリアメタル膜14よりも比抵抗が高いことを特徴とする。

(もっと読む)

金属酸化膜の形成方法および金属酸化膜

【課題】所定パターンを有するとともに、表面抵抗率や光透過率等のばらつきが少ない金属酸化膜の形成方法およびそのような金属酸化膜を提供する。

【解決手段】基材上に、所定パターンを有する金属酸化膜の形成方法等であって、基材に対して、金属塩を含有する液状物を塗布して金属塩膜を形成する第1工程と、金属塩膜に対して、所定パターンを設ける第2工程と、金属塩膜に対して、熱酸化処理または所定のプラズマ酸化処理を行い、金属酸化膜とする第3工程と、を含む。

(もっと読む)

有機半導体素子及びその製造方法並びに有機光電変換素子

【課題】光電変換効率及び応答速度に優れ、かつ暗電流が低減された有機光電変換素子を提供すること。

【解決手段】導電性電極と、前記導電性電極と接する有機半導体層とを含む有機半導体素子であって、前記導電性電極と前記有機半導体層との接合界面における真空準位シフトが、前記接合界面への光照射により調整された、有機半導体素子。

(もっと読む)

電極形成方法および電極形成装置

【課題】基板上に電極を形成する方法および装置において、低コストで、しかも優れた生産性で、幅の異なる電極を形成することのできる技術を提供する。

【解決手段】光硬化性樹脂を含む塗布液と吐出する吐出ノズル部と、吐出された塗布液に光照射して硬化させる光照射部とを2組設け、それぞれの照射条件を異ならせる。第1ヘッド部5に設けた吐出ノズル部52と光照射部53との間隔が、第2ヘッド部7に設けた吐出ノズル部72と光照射部73との間隔よりも小さい。このため、第1ヘッド部5では、塗布液が基板Wに塗布されてから光照射されるまでの時間が短く、幅が狭くて高さのある電極が形成される。一方、第2ヘッド部7では、塗布液が基板Wに塗布されてから光照射されるまでの時間が長いので塗布液が広がり、より幅広の電極が形成される。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

配線形成方法

【課題】樹脂基板上に、接着層等を形成するための別の工程を加えることなく、基板との密着性の高い導電性配線を簡単に形成することができる配線形成方法を提供することを目的とする。

【解決手段】樹脂基板1上に、導電性微粒子を含有する分散溶液の塗布層3を形成する工程と、レーザ光6を塗布層3の特定領域に連続的に照射していくことで、導電性微細配線4を形成する工程と、導電性微細配線4以外の領域の材料を除去する工程とを備え、塗布層3の厚さをd、塗布層3の光吸収係数をα、レーザ光6の入射光強度をI0、樹脂基板1上に到達するレーザ光6の透過光強度をI1とするとき、以下の関係式から成り立つことを特徴とする。

log(I1/I0)=−αd

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 高速動作が可能な半導体装置を提供する。

【解決手段】 半導体基板上の絶縁層上に形成された半導体層と、ゲート絶縁膜を介して前記半導体層上に配置されたゲート電極と、前記ゲート絶縁膜及びゲート電極の側壁に沿うように形成された側壁絶縁膜と、前記絶縁層に底面が接する合金層を含んで構成されたソース/ドレイン層と、 前記合金層と前記半導体層との界面に自己整合的に偏析され、前記半導体層の結晶方位面に沿ってチャネル領域に対する接合面が形成された不純物導入層とを有する半導体装置を形成する。

(もっと読む)

半導体素子の製造方法

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子の製造方法を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備する層構造準備工程と、層構造30Aを設置する層構造設置工程と、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源3を用い、熱源3によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、金属層又は半導体層4を形成する金属・半導体領域形成工程と、を有する半導体素子の製造方法とすることで上記課題を解決する。

(もっと読む)

半導体素子及びその製造装置

【課題】汎用性が高く、低コストで省資源である方法を採用し、実用性に富み、任意の場所、任意の形状に金属又は半導体を二次元的又は三次元的に形成できる半導体素子及びその製造装置を提供する。

【解決手段】炭素材料と金属酸化物材料又は半導体酸化物材料とを有する還元反応構造1Aを持つ層構造30Aを準備し、還元反応構造1Aに対して局所的にエネルギーを集中することが可能で、かつ還元反応構造1Aに対して2次元的又は3次元的に走査することが可能な熱源を用い、この熱源によって酸化還元反応が起こる温度以上に還元反応構造1Aの一部を走査しつつ選択的に加熱して、炭素材料により金属酸化物材料又は半導体酸化物材料をそれぞれ金属又は半導体に還元し、所望の形状の金属領域又は半導体領域(金属層又は半導体層3A)を形成することによって製造されることを特徴とする半導体素子40Aとすることにより上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

61 - 80 / 375

[ Back to top ]