Fターム[4M104FF22]の内容

半導体の電極 (138,591) | 構造 (12,435) | コンタクトホールの孔埋め構造 (1,175) | 2以上の物質で孔埋め (943)

Fターム[4M104FF22]の下位に属するFターム

側面のみ他物質で処理 (58)

Fターム[4M104FF22]に分類される特許

201 - 220 / 885

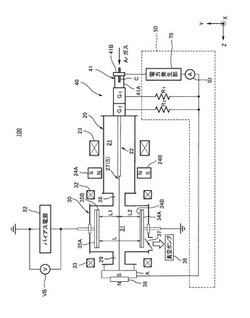

スパッタリング装置およびスパッタリング方法並びに成膜システム

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料の埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、スパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマ22を磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34BとAlターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってAlターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al堆積膜200のカバレッジ性が、プラズマ放電電流ID、ターゲットバイアス電圧VB、および、ターゲット−基板間距離Lに基づいて調整される。

(もっと読む)

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応答特性を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1および第2の絶縁層13、14と電極層とFP電極17とを備える。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成される。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成される。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成される。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成される。第1の絶縁層13は、第2の絶縁層14を構成する材料の誘電率よりも小さい誘電率を有する材料を含む。

(もっと読む)

コンタクトプラグ、配線、半導体装置およびコンタクトプラグ形成方法

【課題】薄膜であっても銅(Cu)原子の金属シリサイド膜などへの拡散を充分に安定して抑止でき、尚且つ、小さな接触抵抗をもたらす比抵抗の小さな銅(Cu)からコンタクトプラグを形成できるようにする。

【解決手段】 本発明のコンタクトプラグ100は、半導体装置の絶縁膜104に設けられたコンタクトホール105に形成され、コンタクトホール105の底部に形成された金属シリサイド膜103と、コンタクトホール105内で金属シリサイド膜103上に形成された酸化マンガン膜106と、酸化マンガン膜106上に、コンタクトホール105を埋め込むように形成された銅プラグ層107と、を備え、酸化マンガン膜は非晶質からなる膜である、ことを特徴としている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置は、GaN層10と第1の絶縁層13と第2の絶縁層14と電極層とFP電極17とを備えている。GaN層10は、高欠陥領域10aと、高欠陥領域10aよりも欠陥密度の低い低欠陥領域10bとを含み、主表面10cを有する。第1の絶縁層13は、GaN層10の主表面10cにおける高欠陥領域10aを覆うように形成されている。第2の絶縁層14は、GaN層10の主表面10aにおける低欠陥領域10bの上に形成され、開口部が形成されている。電極層は、開口部の内部に、GaN層10の主表面10aに接触するように形成されている。FP電極17は、電極層に接続するとともに、第2の絶縁層14に重なるように形成されている。第1の絶縁層13の厚みH13は、第2の絶縁層14の厚みH14よりも大きい。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】ソース/ドレイン領域のPN接合部とコンタクト間のリーク電流を抑制する。

【解決手段】半導体基板(1)と、半導体基板(1)に形成されたSTI(Shallow Trench Isolation)構造(2)と、半導体基板(1)に形成され、STI構造(2)に隣接する拡散領域(12)と、層間絶縁膜(15)を貫通して拡散領域(12)とSTI構造(2)とに到達する接続コンタクト(20)と、拡散領域(12)の側面と拡散領域(12)の下の半導体基板(1)の側面に形成され、接続コンタクト(20)と拡散領域(12)の側面とを電気的に絶縁し、かつ、接続コンタクト(20)と半導体基板(1)の側面とを電気的に絶縁する酸化膜(19)とを具備する半導体装置を構成する。その半導体装置では、STI素子分離とソース/ドレイン領域のPN接合部分の間のみに選択的に絶縁膜(酸化膜)を形成している。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ウエハが反るのを防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、互いに対向する第1及び第2の主面を有するGaAs基板と、前記GaAs基板の前記第1の主面上に形成され、Pd、Ta、Moの少なくとも1つから構成された第1の金属層と、前記第1の金属層上に形成され、Ni系合金又はNiから構成された第2の金属層と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

高アスペクト比のフィーチャーへのタングステン堆積方法

【課題】高アスペクト比のフィーチャーをタングステン含有材料で充填する。

【解決手段】部分的に製造された半導体基板上の高アスペクト比のフィーチャーをタングステン含有材料で充填する方法が提供される。ある実施形態においては、当該方法は高アスペクト比のフィーチャーにタングステン含有材料を部分的に充填する工程とフィーチャー空洞から部分的に充填された材料を選択的に除去する工程とを有する。これらの方法を用いて処理された基板においては、高アスペクト比のフィーチャーに充填されたタングステン含有材料のステップカバレッジが改善され、シームの大きさが低減する。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線の添加元素を細幅配線の添加元素とは独立に制御する。

【解決手段】

層間絶縁膜に、第1の幅を有する第1の配線溝および第1の幅より広い第2の幅を有する第2の配線溝を形成し、第1の配線溝および第2の配線溝内に、第1の添加元素を含む第1のシード層を形成し、第1のシード層上に第1の銅層を形成し、第1の配線溝内の第1の銅層および第1のシード層を残存させつつ、第2の配線溝内の第1の銅層および第1のシード層を除去し、その後、第2の配線溝内に、第2の添加元素を含む又は添加元素を含まない第2のシード層を形成し、第2のシード層の上に第2の銅層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

めっき装置

【課題】比較的簡単な構成で、めっき槽内のめっき液の流れをより均一に調節して、めっき膜の膜厚の面内均一性をより高め、めっき膜の埋込み等をより短時間で確実に行うことができるようにする。

【解決手段】めっき槽の内部に該めっき槽内のめっき液に浸漬されるように配置され、ホルダで保持した被めっき材の被めっき面に向けてめっき液を噴射してめっき槽内にめっき液を供給する複数のめっき液噴射ノズル406を有するノズル配管400を備え、該ノズル配管400は、縦パイプ402と横パイプ404とを格子状に組んで構成され、ホルダで保持してめっき槽内にめっき液に浸漬させて配置される被めっき材の被めっき面と平行に横方向及び/または縦方向に移動自在に構成されている。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上に容易なプロセスにより、微細で、高速なSOI構造の縦型のMISFETを得ること。

【解決手段】半導体基板1上に酸化膜2を介して、下部に配線層3を有する自己整合の横及び縦方向エピタキシャル半導体層からなる凸状構造の半導体層6が設けられ、凸状構造の半導体層6は素子分離領域埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。凸状構造の半導体層6の上部には高濃度及び低濃度ドレイン領域10、9が設けられ、下部には高濃度及び低濃度ソース領域7、8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられ、高濃度ドレイン領域10、下層配線3を介した高濃度ソース領域7及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている自己整合連続縦横エピタキシャル成長法によるMISFET。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線に断線が発生することを抑制し、かつエレクトロマイグレーションに対する耐性、及び熱ストレスに起因したボイドの発生に対する耐性を配線に持たせる。

【解決手段】第2導電パターン104は端が第1導電パターン100につながっており、第1導電パターン100より幅が細い。第1導電パターン100及び第2導電パターン104は、シード層110及びメッキ層120を有する。シード層110及びメッキ層120は、それぞれ銅により形成されている。メッキ層120は、底層に、表層より結晶粒が小さい小粒層122を有している。そして第2導電パターン104を形成するメッキ層120は、小粒層122を、第1導電パターン100を形成するメッキ層120より厚く有している。

(もっと読む)

半導体デバイス及びその形成方法

【課題】応力ライナによるコンタクト形成の問題が起きない、相補型金属酸化膜半導体(CMOS)デバイスの製造方法を提供する。

【解決手段】シリコン基板層上の二酸化シリコン層102と、凹んだソース/ドレイン・トレンチを有する相補型金属酸化膜半導体(CMOS)デバイスを準備し、凹んだソース/ドレイン・トレンチ内に窒化物応力ライナ104を堆積し、その上に酸化物層106を堆積する。CMOSデバイスをハンドリング・ウェハ上に置きシリコン基板層を除去し二酸化シリコン層102をエッチングしてソース/ドレイン領域170の一部に当接する開口部を形成しコンタクト180を形成する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線を有する半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1上に第1配線用絶縁膜IM1を形成し、第1配線用絶縁膜IM1に配線溝TM1を形成する。その後、配線溝TM1に銅を主体とする導体膜を埋め込むことで配線MW1を形成する。続いて、配線MW1上にキャップ導体膜MC1を形成した後、キャップ導体膜MC1に表面研磨を施す。特に、キャップ導体膜MC1はALD法によって配線MW1上に選択的に形成する。

(もっと読む)

201 - 220 / 885

[ Back to top ]