Fターム[4M104GG14]の内容

Fターム[4M104GG14]に分類される特許

21 - 40 / 3,371

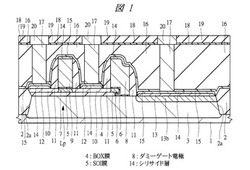

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】X線検出用フォトダイオード等においては、初期結晶材料として、裏面側に高濃度の不純物がドープされた単結晶ウエハ等を使用する場合がある。このような場合、裏面側不純物の外方拡散によるクロスコンタミネーション等を防止するために、予め、ウエハの裏面に、酸化シリコン膜等の不純物外方拡散防止膜等を形成しておく等の対策が講じられる。しかし、裏面に不純物外方拡散防止膜を形成する際に、ウエハの表面を損傷する等の問題が有る。

【解決手段】本願発明は、裏面に高濃度の不純物ドープ層を有する半導体ウエハの裏面に、不純物防止膜を形成するに当たり、まず、前記半導体ウエハの表面に酸化シリコン系絶縁膜等の表面保護膜を形成し、その状態で、前記裏面に、前記不純物防止膜を形成し、その後、ウエットエッチングにより、前記不純物防止膜を残した状態で、前記表面保護膜をほぼ全面的に除去するものである。

(もっと読む)

半導体装置、および、その製造方法、固体撮像装置

【課題】ショートチャネル特性などを向上する。

【解決手段】n型FET111Nの半導体活性層111Cの上面に、バックゲート絶縁膜401を介してバックゲート電極121を金属材料で形成する。ここでは、バックゲート電極121,221について、半導体活性層111Cの上面においてゲート電極111Gおよび一対のソース・ドレイン領域111A,111Bに対応する部分を被覆するように、バックゲート電極121を形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

銅層および/または銅合金層を含む金属膜用エッチング液組成物およびそれを用いたエッチング方法

【課題】 本発明の課題は、銅層および/または銅合金層を有する金属膜や、該層と他の金属からなる層との積層膜を精度良くエッチングでき、液寿命が長いエッチング液組成物を提供することにある。

【解決手段】 本発明は、銅層および/または銅合金層を含む金属膜をエッチングするためのエッチング液組成物であって、銅(II)イオン、β−アラニンおよび水を含む、前記エッチング液組成物、ならびに、該エッチング液組成物を用いたエッチング方法に関する。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法

【課題】大型化に適した薄膜トランジスタ、薄膜トランジスタアレイ基板、フレキシブル表示素子、フレキシブル表示装置及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】フレキシブルな樹脂基板60に形成された薄膜トランジスタ200であって、周面の一部又は全部が導電性材料20により覆われたワイヤー10と、前記導電性材料を覆う絶縁膜30と、該絶縁膜を介して前記導電性材料上に形成された薄膜半導体40と、が一体的に構成されたゲート・チャネル一体形成部50を有し、該ゲート・チャネル一体形成部が前記樹脂基板の表面上又は内部の所定位置に設けられ、前記薄膜半導体の両側に第1及び第2の電極70、80が接続されて形成されたことを特徴とする。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置の製造方法、半導体装置および基板処理装置

【課題】耐酸化性に優れ、導電性や仕事関数の劣化を防止または抑制できる電極を備えた半導体装置の製造方法、半導体装置および基板処理装置を提供する。

【解決手段】処理室に、表面にゲート絶縁膜302またはキャパシタ絶縁膜が形成された基板を搬入する基板搬入工程と、基板上に、導電性酸化膜を含む電極であって、導電性酸化膜の仕事関数を変調する添加剤が添加された電極を形成する電極形成工程と、電極が形成された基板を処理室から搬出する基板搬出工程と、を有する。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法および表示装置

【課題】ソースおよびドレインと半導体層との間において良好なコンタクトを確保することが可能な有機薄膜トランジスタを提供する。

【解決手段】有機薄膜トランジスタは、有機材料よりなる半導体層上のソース電極およびドレイン電極に対向する第1および第2の領域のそれぞれに導電層を有し、この導電層が、還元反応によって導電性が変化する酸化物を含むものである。導電層が、半導体層とソース電極およびドレイン電極とのコンタクト層として機能すると共に、トップコンタクト構造では、製造プロセスにおいて半導体層上に、上記導電層を含むエッチングストッパ層を形成可能となる。

(もっと読む)

表示装置およびその製造方法、並びに電子機器

【課題】互いに電気的に接続された薄膜トランジスタの第2電極と配線層との間の電食の発生を防止して、安定した電気特性を得ることできる表示装置およびその製造方法、並びに電子機器を提供する。

【解決手段】薄膜トランジスタおよび配線層を備え、前記薄膜トランジスタは、制御電極

と、前記制御電極と対向する半導体層と、前記半導体層に電気的に接続され、光透過性材

料からなる第1電極と、前記光透過性材料よりも低抵抗の金属膜を含むと共に、前記半導

体層および前記配線層にそれぞれ電気的に接続された第2電極とを備え、前記金属膜の構

成材料と前記配線層の少なくとも一部を構成する導電材料とのイオン化傾向の差は、前記

光透過性材料と前記導電材料とのイオン化傾向の差よりも小さい表示装置。

(もっと読む)

トップゲート型アクティブマトリックス基板、およびその製造方法

【課題】データ配線が銀や銀合金により形成されており、またデータ配線に、ゲート絶縁層によって被覆されておらずむき出しとなっている部分があった場合でも、当該むき出しとなっている部分でマイグレーション現象が生じることがないトップゲート型アクティブマトリックスを提供する。

【解決手段】基材と、前記基材上に直接または間接的に形成された、ソース電極、ドレイン電極、半導体層、ゲート絶縁層、ゲート電極、層間絶縁層、画素電極、および前記ソース電極と接続したデータ配線と、を有するトップゲート型アクティブマトリックス基板において、前記ソース電極と前記データ配線をともに銀または銀合金で形成し、前記ゲート電極を銀または銀合金以外で形成し、前記データ配線においてむき出しとなっている部分をゲート電極と同じ材質からなる被覆層によって被覆する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置の製造方法、基板処理方法、基板処理装置およびプログラム

【課題】 金属炭化物系の膜を段差被覆性良く形成する。

【解決手段】 基板に対して、第1金属元素とハロゲン元素とを含む第1原料と第2金属元素と炭素とを含む第2原料とを交互に所定回数供給する工程と、基板に対して、窒化原料を供給する工程と、を交互に所定回数行うことで、基板上に、所定膜厚の第1金属元素を含む金属炭窒化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

21 - 40 / 3,371

[ Back to top ]