Fターム[5F004DB02]の内容

半導体のドライエッチング (64,834) | 被エッチング物 (6,778) | Si (1,365) | 多結晶Si (435)

Fターム[5F004DB02]に分類される特許

141 - 160 / 435

半導体素子の製造方法

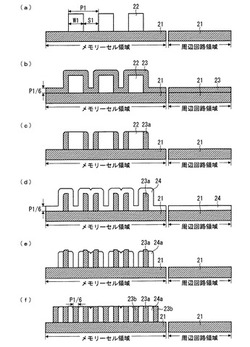

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

半導体基板の表面処理装置

【課題】パターンの倒壊を防止しつつ基板を洗浄・乾燥させる半導体基板の表面処理装置を提供する。

【解決手段】薬液を用いて半導体基板を洗浄し、純水を用いて前記薬液を除去し、前記半導体基板表面に撥水性保護膜を形成し、純水を用いて前記半導体基板をリンスし、前記半導体基板を乾燥させる。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETの耐圧性向上を目的として設けられた電界緩和リング(FLR)の側面に、エッチングの際に残るPoly−Si膜によって、FLRパターンの配線間の寸法差にばらつきが発生することを防止する。また、その寸法差のばらつきによるVDSS耐圧特性の不具合の発生を防止し、歩留まりを向上させる。

【解決手段】半導体基板3上のPoly−Si膜をドライエッチングにより加工し、ゲート電極8Gを形成する際、エッチングガスに使用するCl2及びO2ガスに加え、SF6ガスを添加してエッチングすることにより、等方性エッチングを可能にし、FLR5の側面のエッチング残り9の量を低減させる。

(もっと読む)

スペーサマスクパターニングプロセスフローを用いた大きい特徴部と配列との一体パターニング

【課題】パターン形成特徴部の幅とパターン形成特徴部の間の間隔(トレンチ幅)の双方を集積回路内で変化させつつ単一高解像度フォトマスクを用いた標準フォトリソグラフィ処理技術を用いて可能であるものと比較して高密度(即ち、低ピッチ)を持つ基板上にパターン形成特徴部を形成する方法を提供する。

【解決手段】基板の上にコア層と保護層を形成し252、レジストパターンをコア層に転写256、レジスト除去自己制限的エッチングにより狭いパターン上の保護層すべてと、広いパターンの保護層の一部を除去260し、コンフォーマル誘電体層を形成、方向性エッチング264後、狭いパターン構造からコア層を除去268してパターン形成特徴部が形成される。

(もっと読む)

半導体装置の製造方法および半導体洗浄用組成物

【課題】熱酸化シリコン膜、非ドープCVD酸化シリコン膜、多結晶シリコン膜、窒化シリコン膜を含む積層膜に対して、常温において洗浄時の各種膜に対するエッチング量差を低減し、また、各種膜に対するエッチング速度を適度に制御することを可能とする。

【解決手段】半導体基板の主面上に絶縁層を形成する工程と、前記絶縁層の上に導電層を堆積する工程と、前記導電層の上にフォトレジスト膜を形成する工程と、前記絶縁層および前記導電層をエッチングすることによってゲート素子を形成する工程と、前記フォトレジスト膜を除去した前記半導体基板の主面を半導体洗浄用組成物によって洗浄する工程と、前記半導体洗浄用組成物のリンス処理および乾燥処理を行う工程とを含む半導体装置の製造方法であって、前記半導体洗浄用組成物は、フッ化アンモニウムと、フッ化水素酸と、過酸化水素と、脂肪族第1級アミンとを含む20℃〜28℃の混合水溶液からなる。

(もっと読む)

基板処理装置および半導体デバイスの製造方法

【課題】 ノズル等のガス出力手段の内壁全体をクリーニングガスによってクリーニングすることができるようにする。

【解決手段】 基板に所定の処理を施す反応管と、反応管内に反応ガスを供給する複数のノズルと、複数のノズルとは別に設けられ、反応管内にクリーニングガスを供給するクリーニング用ノズルと、ノズルの内部をクリーニングする場合に、複数のノズルのうち選択したノズルにクリーニングガスを供給し、選択していないノズルに不活性ガスを供給すると共に、反応管の内部をクリーニングする場合に、少なくともクリーニング用ノズルより反応管内にクリーニングガスを供給するように制御するコントローラと、を有する。

(もっと読む)

半導体装置の製造方法

【課題】疎部及び密部のそれぞれにおいて、所望の寸法のデバイスパターンを簡単にエッチングにより形成できるようにする。

【解決手段】金属層12上に2層のマスク層13,14を形成する工程と、2層のマスク層13,14に対して、各層ごとに、デバイスパターンを疎に形成する疎部または密に形成する密部におけるCDシフト量を調整する1種類のエッチングパラメータを変更させてエッチングを行い、マスクパターン13−1〜13−4,14−1〜14−4を形成する工程と、マスクパターン13−1〜13−4を用いて金属層12をエッチングし、ゲート電極12−1〜12−4を形成する。

(もっと読む)

プラズマエッチング方法及びプラズマエッチング装置

【課題】アスペクト比エッチングを行う際に,エッチングレートとレジスト選択比の両方を従来以上に向上させることができるプラズマエッチング方法を提供する。

【解決手段】堆積性を有するエッチングガス(例えばフルオロカーボン系ガス)を含む処理ガスにSF6ガスを添加ガスとして加えて処理室102内に導入してプラズマを形成し,その際に添加ガスの流量を調整することによって,ウエハW上に堆積する堆積物の膜厚を制御するとともに,堆積物の硬さを制御しながら,被エッチング膜のエッチングを進行させる。

(もっと読む)

半導体装置の製造方法

【課題】ドライクリーニングにおいてガス供給管の破損を防ぎ、メンテナンス効率を高めるようにする。

【解決手段】ウエハ200を処理室201内に搬入する工程と、ガス供給管165,166,167に原料ガスを供給して処理室201内に原料ガスを導入し、基板200にシリコン又はシリコン化合物の膜を形成する工程と、処理室201内から基板を搬出する工程と、処理室201内を加熱する加熱工程と、加熱工程後に処理室201内の温度を低下させる降温工程と、降温工程後にガス供給管165,166,167にクリーニングガスを供給して処理室201内にクリーニングガスを導入するクリーニングガス導入工程と、を含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】高アスペクト比を有する多結晶シリコン膜のエッチング加工において、加工性の向上を図る。

【解決手段】シリコン基板1の上面にゲート絶縁膜4が形成され、その上面に多結晶シリコン膜5、7、電極間絶縁膜6などからなるゲート電極の積層膜からなる加工対象膜が形成されている。この上面に、ハードマスクとして機能するシリコン窒化膜8、酸化アルミニウム膜9が積層される。従来相当のシリコン窒化膜10が単層の構成のハードマスクに比べ、ハードマスクを薄くすることができる。これによって、リソグラフィのパターン幅Aに対して最終加工幅C1はC2に対して小さくすることができ、加工変換差を小さくすることができる。

(もっと読む)

プラズマ処理装置

【課題】真空雰囲気において処理容器内の基板に対して処理ガスをプラズマ化したプラズマを供給してプラズマ処理を行うにあたって、面内均一性高く処理を行うこと。

【解決手段】基板を載置する載置台に対向するように、下面に多数のガス吐出孔が形成されたガスシャワーヘッドを処理容器の天壁に設けると共に、このガスシャワーヘッドの周囲における処理容器の天壁を誘電体により構成し、この誘電体上に基板の上方の処理領域の周囲にマイクロ波により前記基板の径方向に概略平行な電界を形成し、更にガスシャワーヘッドに負の直流電圧を印加する。

(もっと読む)

プラズマ加工装置及びプラズマ加工方法

【課題】水素ガスをエッチングガスとして用いた場合に、シリコン材料の表面粗さを悪化させることなく、シリコン基板を鏡面加工し得るプラズマ加工装置及びプラズマ加工方法を提供する。

【解決手段】プラズマ加工処理装置10は、水素雰囲気下にてシリコン基板2に近接させた電極11とシリコン基板2との間に生成した水素プラズマ6を、シリコン基板2の表面に接触させてシリコン基板2をエッチングする。水素プラズマ6を生成するためのマイクロ波を出力するマイクロ波発振器23と、電極11を形成するパイプ内を通して水素ガスをシリコン基板2の加工面へ向けてプラズマ内部へ供給する水素導入ライン12とを備える。シリコン基板2の内部への水素の拡散速度以上のエッチング速度にてシリコン基板2をエッチングする。

(もっと読む)

プラズマ処理方法及び装置

【課題】大気圧プラズマ処理において、フッ素原料の回収率又は回収濃度の変動を抑制し、処理の安定性を確保する。

【解決手段】大気圧プラズマ処理部2から排出ライン30に出された排出ガスを、分離部40の分離膜41で回収ライン50への回収ガスと放出ライン60への放出ガスに分離する。回収ガスをプロセスガスの少なくとも一部に充てる。上記分離に際し、フッ素系原料の回収率及び回収濃度のうち何れか一方又は両方が所望になるよう、回収ガス、放出ガス、排出ガスのうち少なくとも2つのガスの上記分離に係る物理量(好ましくは圧力)をプロセスガスの流量に応じて調節する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長を決めるドライエッチングにおいてプラズマ発光をモニターすることによる終点検出方法を用いることにより半導体装置のゲート長を安定して製造する。

【解決手段】ソース拡散層、ドレイン拡散層及び柱状半導体層が基板上に垂直方向に階層的に配置され、柱状半導体層の側壁にゲートが配置される半導体装置の製造方法であって、柱状半導体層を埋め込むように第1の絶縁膜又は導電膜を成膜し、第1の絶縁膜又は導電膜を柱状半導体層上部に形成されたストッパーにより終点検出を行い平坦化し、第2の絶縁膜又は導電膜を成膜し、第2の絶縁膜又は導電膜のエッチングすると共にエッチング時のエッチングレートを算出し、第2の絶縁膜又は導電膜をエッチバックする際の第2の絶縁膜又は導電膜のエッチングレートを用いて第1の絶縁膜又は導電膜のエッチングの終点検出を行うことにより、第1の絶縁膜又は導電膜のエッチング量を制御する。

(もっと読む)

基板処理装置及び光学定数算出方法並びにその方法を実行するプログラムを記憶した記録媒体

【課題】基板上の積層膜構造における各膜の光学定数を算出する際に,各光学定数の算出精度を向上させる。

【解決手段】基板上に形成された積層膜構造における各膜の光学定数を算出する光学定数算出方法であって,各膜をそれぞれ下から順に対象膜とし,その対象膜の光学定数を既に算出された下層膜の光学定数を用いて算出することによって,各膜の光学定数を順次算出する基本ステップと,基本ステップで算出した対象膜の光学定数を,再フィッティング処理によって下層膜の光学定数を修正しながら算出し直す再計算ステップとを有する。これにより,下層膜の光学定数を物理的に正しい解に導くことができ,光学定数の算出精度を向上させることができる。

(もっと読む)

コンタクトホール側壁の抵抗値測定方法

【課題】コンタクトホール側壁に付着した有機膜の抵抗値を簡単且つ的確に測定する。

【解決手段】基板20上に形成された下部電極であるポリSi膜22aと、このポリSi膜22a上にBPSG膜23を介して形成された中間電極であるポリSi膜24aと、このポリSi膜24a上にBPSG膜25を介して選択的に形成されたホトレジスト膜からなるホールパターン26aと、このホールパターン26aをマスクにしてプラズマエッチングにより形成され、ポリSi膜24a,22aを貫通するコンタクトホール27と、このコンタクトホール27の形成時に、コンタクトホール側壁に付着する有機膜28と、を有する半導体装置を用意する。そして、ポリSi膜22a,24a上に有機膜・レジスト膜26bが被着された状態で、ポリSi膜22a,24a上から、プローブ針31により複数回コンタクトを実施し、有機膜28の抵抗値を測定する。

(もっと読む)

プラズマ処理装置

【課題】エッチング加工形状のウエハ面内における均一性が良好で、極微細加工、あるいは多層膜エッチングに好適なプラズマ処理装置を提供する。

【解決手段】内部を減圧可能な減圧処理室8と、該減圧処理室内に処理ガスを供給するガス供給手段9と、前記減圧処理室内にマイクロ波を供給してプラズマを生成するマイクロ波供給手段1と、前記減圧処理室内に被処理材である試料を載置して保持する試料載置電極11と、前記減圧処理室に接続され該減圧処理室内のガスを排気する真空排気手段14を備え、前記減圧処理室、ガス供給手段の処理室へのガス供給部、マイクロ波供給手段の処理室へのマイクロ波導入部、試料載置電極、および真空排気手段を前記減圧処理室の中心軸に対して同軸上に配置し、前記マイクロ波導入部は、入力されたマイクロ波の偏波面を回転させて前記処理室に供給するマイクロ波回転発生器22を備えた。

(もっと読む)

半導体加工方法

【課題】高誘電率絶縁膜上に金属膜及び多結晶Siを堆積した構造の半導体を垂直にかつ微細に加工する。

【解決手段】半導体基板上に形成されたHfあるいはZrを含む絶縁膜102、該絶縁膜上に並置して形成された互いに仕事関数が異なる第1および第2の金属膜103,104、該第1および第2の金属膜上に堆積して形成した多結晶シリコン膜105を有し、該多結晶シリコン膜上に形成したレジスト108を用いて、プラズマ雰囲気中で前記多結晶シリコン膜並びに前記第1および第2の金属膜をエッチング加工する半導体加工方法において、前記前記複数種の金属膜上の多結晶シリコン膜のうちエッチング終了が早い方である第2の金属膜上の多結晶シリコン膜のエッチング終了後は、前記処理ガスとして、HBrおよび酸素を含むガスを用いる。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を増加させることができる半導体素子のパターン形成方法を提供する。

【解決手段】基板300上のデュアルマスク層をパターニングして第1領域Aには第1マスクパターン320Aを形成し、第2領域Bには第1マスクパターン320Aより幅広である第2マスクパターン320Bを形成する。第1マスクパターン320Aの両側壁を覆う第1スペーサ350Aと第2マスクパターン320Bの両側壁を覆う第2スペーサ350Bとを同時に形成する。第1マスクパターン320Aを除去した後、第1領域Aでは、第1スペーサ350Aをエッチングマスクとして利用し、第2領域Bでは第2マスクパターン320B及び第2スペーサ350Bをエッチングマスクとして利用して第1領域A及び第2領域Bで同時に基板300をエッチングする。

(もっと読む)

テクスチャー形成方法及び真空処理装置

【課題】シリコン表面における発電面積を大きくしうるテクスチャーを効率良く形成する技術を提供する。

【解決手段】本発明は、シリコン基板の表面の自然酸化膜をドライエッチング法によって除去する自然酸化膜除去工程(P2)と、シリコン基板の表面をドライエッチング法によってテクスチャーを形成するテクスチャー形成工程(P4)と、シリコン基板の表面におけるテクスチャーの形成時にダメージを受けた層をドライエッチング法によって除去するダメージ層除去工程(P6)と、シリコン基板のテクスチャーの形状をウェットエッチング法によって丸めるテクスチャー丸め工程(P7)とを有する。自然酸化膜除去工程(P2)、テクスチャー形成工程(P4)、ダメージ層除去工程(P6)を同一の真空処理槽2内で行う。

(もっと読む)

141 - 160 / 435

[ Back to top ]