Fターム[5F033JJ07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566)

Fターム[5F033JJ07]の下位に属するFターム

Fターム[5F033JJ07]に分類される特許

161 - 180 / 1,123

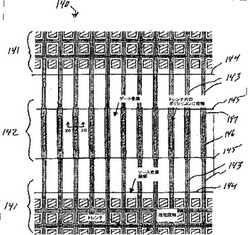

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置

【課題】マイクロバンプの半導体素子側への接着力を向上できる半導体装置を提供する。

【解決手段】半導体素子2と半導体素子の電極パッドと、電極パッド20を露出する開口41を有するバッファーコート膜40と、開口を介して電極パッドに電気的に接続されたマイクロバンプ50とを備え、マイクロバンプと開口の側面41bとの接触面積は、マイクロバンプと開口の底面60aとの接触面積より大きいことを特徴とする半導体装置。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置

【課題】低抵抗かつ微細化が可能なグラフェン配線を有する半導体装置およびその製造方法を提供する。

【解決手段】一実施の形態によれば、半導体装置は、配線と前記配線に接続されるコンタクトプラグを有する。前記配線は、長さ方向の両側面に触媒層を有する基体と、前記基体の前記両側面上に前記触媒層と接して形成され、前記基体の前記両側面と垂直に積層された複数のグラフェンを有するグラフェン層を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】再配線間のリークを抑制しつつ、再配線のピッチを微細化するとともに、再配線上のビア開口時のマージンを上げる。

【解決手段】緩衝層4上には再配線7bが形成され、再配線7b上には表面層8bが形成されている。表面層8bは、再配線7bから幅方向にはみ出すようにして再配線7bに沿うように配置され、再配線7bよりもエッチング耐性が高い。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

半導体基板の製造方法

【課題】ビア配孔内に形成したカーボンナノチューブを埋め込む埋め込み膜が基板に均一に形成されないため基板の平坦化処理工程において層間絶縁膜が不均一に研磨されて、下層配線と上部電極がビア配線以外で電気的につながってしまう場合が発生する。

【解決手段】半導体基板における層間絶縁膜内のビアホール内にカーボンナノチューブを形成した後、基板全体をフッ化処理することにより、カーボンナノチューブが存在するビアホールにのみ埋め込み膜が形成され、その後に基板全体の平坦化処理のために基板を研磨する工程において、層間絶縁膜が局所的に研磨されることを防止する。

(もっと読む)

半導体デバイス

【課題】応力による半導体回路の特性劣化を抑制した半導体デバイスを提供する。

【解決手段】縦導体は、半導体基板の厚み方向に設けられた微細孔を満たし、第1結晶組織301と第2結晶組織302とを含むナノコンポジット結晶構造を有する。ナノコンポジット結晶構造において、第1結晶組織301及び第2結晶組織302の少なくとも一方は、ナノサイズである。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】MRAMにおいては、書き込み電流の低減やディスターブ回避を目的に、書き込みに使用する配線を強磁性体膜で覆うクラッド配線構造がよく用いられている。また、高信頼性製品の信頼性確保のためCu配線中に微量のAlを添加するCuAl配線が広く使用されている。MRAMも高信頼性製品に搭載される可能性が高く、信頼性は重要である。しかし、クラッド配線は、もともと配線抵抗が高いCuAl配線の配線抵抗を更に上昇させるというデメリットがあるため、両方の技術を同時に使用すると配線抵抗のスペックを満たさなくなる可能性が高い。

【解決手段】本願発明は、多層銅埋め込み配線を有する半導体装置において、MRAMメモリセルマトリクス領域を構成する複数の銅埋め込みクラッド配線の銅配線膜を比較的純粋な銅で構成し、これらの配線層よりも下層の銅埋め込み非クラッド配線の銅配線膜を、Alを添加したCuAl配線膜とするものである。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造を有するCu配線において、バリア膜の拡散防止機能を低下させずにCu配線内のCuの埋め込み性を改善し、半導体装置の歩留まりおよび信頼性を向上する。

【解決手段】ダマシン配線を有する半導体装置において、第2層間絶縁膜6に形成した配線溝G2およびビアホールV2のそれぞれの内壁にバリア膜としてTaN膜7およびCuと濡れ性の良いTiからなるTi膜8とを順に形成することにより、Ti膜8上に均一にCuシード膜9aを形成することを可能とする。これにより、Cuシード膜9aを電極として電界メッキ法によりCu膜9を形成した際に、配線溝G2およびビアホールV2内に空隙が形成されることを防ぐ。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体装置

【課題】ディッシング及び埋め込み不良のないパッド構造を短時間で安定して形成する。

【解決手段】基板100上に形成された第1の絶縁膜108Bに、複数のパッド配線109pを含むパッドが形成されている。第1の絶縁膜108B上に、前記パッドの少なくとも一部分の上に位置する開口部を有する第2の絶縁膜110が形成されている。複数のパッド配線109pのうち互いに隣り合う配線同士を電気的に接続するように配線接続部109qが設けられている。各パッド配線109pの幅W1は、各パッド配線109pの高さよりも小さく且つ配線接続部109qの幅W3よりも大きい。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】金属マスクを形成する工程を含む半導体装置の製造方法において、金属片が支持基板に付着することを防止する。

【解決手段】この製造方法は、支持基板10の表面10aに貼付された半導体ウェハ12上にネガレジストを塗布し、該ネガレジストを露光することにより所定のパターンを有するレジスト18を形成するレジスト形成工程と、半導体ウェハ12上にメッキ処理を施すことにより金属マスク20を形成したのちレジスト18を除去する金属マスク形成工程と、金属マスク20を介して半導体ウェハ12にエッチングを施すことにより、貫通孔12dを形成するエッチング工程と、金属マスク20を除去したのち、貫通孔12dの内面及び半導体ウェハ12の裏面12bに金属膜26を形成する金属膜形成工程と、半導体ウェハ12を支持基板10から取り外す取外し工程とを含む。

(もっと読む)

半導体装置及び製造方法

【課題】 基板及び表面層にビアホールが形成された半導体装置において、表面層の剥離及び破壊を抑制すること。

【解決手段】 本半導体装置は、基板10と、基板10上に設けられた基板10と異なる材料からなる表面層20と、表面層20上に設けられた電極パッド50と、を備え、基板10及び表面層20にはビアホール30が形成され、ビアホール30内には、電極パッド50と電気的に接続された金属層32が設けられ、ビアホール30の開口部の周囲には、ビアホール30を囲むように表面層20に溝22が形成されている。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

固体撮像装置

【課題】 暗電流やリーク電流の発生を抑制することが可能な固体撮像装置を提供する。

【解決手段】 固体撮像装置は、光電変換素子が主面に配された第1基板と、導電体を含む第1の接合部を有する第1配線構造と、周辺回路の一部が主面に配された第2基板と、導電体を含む第2の接合部を有する第2配線構造と、を有する。そして、第1基板と、第1配線構造と、第2配線構造と、第2基板とがこの順に配置されるように第1の接合部及び第2の接合部とが接合されている。そして、第1の接合部の導電体と、第2の接合部の導電体とは、導電体に対する拡散防止膜で囲まれている。

(もっと読む)

貫通配線基板および製造方法

【課題】ボイドを生じさせない貫通ビアを設けた貫通配線基板。

【解決手段】貫通ビアが設けられた貫通配線基板であって、貫通孔が形成された基板と、貫通孔内に設けられ、基板の上面と下面の間を電気的に接続する導電体と、導電体と貫通孔の間の隙間に充填された樹脂と、を備える貫通配線基板および製造方法を提供する。基板は、ガラス基板であってよい。樹脂は、ポリイミドであってよい。樹脂は、ポリマーであってもよい。樹脂は、光に反応して固体に変化する光硬化樹脂であってもよい。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】研磨工程を含む新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜に、第1の深さを有するダミー溝と、第1の深さよりも深い第2の深さを有する配線溝と、配線溝の底面に配置されるビアホールとを形成する凹部形成工程と、ダミー溝内、配線溝内、ビアホール内、及び絶縁膜上方に、導電材を堆積させる工程と、絶縁膜上方の導電材を研磨除去する工程とを有する。

(もっと読む)

161 - 180 / 1,123

[ Back to top ]