Fターム[5F033JJ07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566)

Fターム[5F033JJ07]の下位に属するFターム

Fターム[5F033JJ07]に分類される特許

201 - 220 / 1,123

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

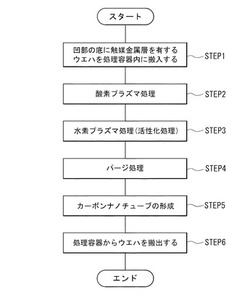

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】上面にストラップ配線が形成された絶縁膜と、この絶縁膜の下面に形成された配線と間で剥離が生じることが抑制された半導体装置および半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板SSと、半導体基板SS上に形成され、周辺配線P1および配線L2が形成された配線層LL1,LL2と、配線層LL2に形成され、配線L3を含む配線層LL3と、配線層LL3上に形成され、磁気記憶素子MRを含む配線層LL4とを備え、配線L1,L2上に形成された拡散防止膜NF1,NF2は、SiCN膜またはSiC膜から形成され、配線L3上に形成された拡散防止膜NF3は、SiNから形成される。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置において、貫通電極によって被覆された貫通孔の内部を充填する保護層にクラック等が発生する不具合を防止する。

【解決手段】

貫通電極9を被覆するとともに、貫通孔6内を充填する保護層10を備える半導体装置1において、保護層10が複数層11、12からなり、複数層の保護層のうち最も半導体基板2の一面2aに近い層が、少なくとも貫通電極の底面9aと側面9bの交差部を被覆し、かつ、ポジ型感光性樹脂を用いて形成されることを特徴とする半導体装置を提供する。

(もっと読む)

薄膜の形成方法

【課題】埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させることが可能な薄膜の形成方法を提供する。

【解決手段】表面に凹部8を有する被処理体Wの表面に薄膜を形成する形成方法において、被処理体の表面に埋め込み用の金属膜16して凹部を埋め込む埋め込み工程と、金属膜を覆うようにして被処理体の表面の全面に拡散防止用の金属膜18を形成する拡散防止膜形成工程と、被処理体をアニールするアニール工程とを有する。これにより、埋め込み金属との密着性及び埋め込み特性の改善を図ることができるのみならず、エレクトロマイグレーション耐性も向上させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドのプローブ領域とボンディング領域とを、光学顕微鏡による拡大観察で明確に識別することができる半導体装置を提供する。

【解決手段】半導体基板に形成された回路と接続される下層メタル配線20と、下層メタル配線20の上に形成され、複数のビアホール35、36を有する層間絶縁膜30と、複数のビアホール35、36を埋める複数の配線部40と、層間絶縁膜30及び複数の配線部40の上に形成され、複数の配線部40を介して下層メタル配線20と電気的に接続する上層メタル配線50とを具備する。層間絶縁膜30は、複数の第1ビアホール35を有する第1絶縁部31と、複数の第2ビアホール36を有する第2絶縁部32と、第1絶縁部31と第2絶縁部32との間に位置し、上面が平らな第3絶縁部33とを備える。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置の製造方法

【課題】配線溝パターンの深さを精密に制御でき、かつ当該配線溝パターンのダメージ形成を抑制できる半導体装置の製造方法を提供する。

【解決手段】拡散防止膜ADF上に、第2の低誘電率膜LOWK2c、第3の低誘電率膜LOWK3c、マスク層となるべき膜がこの順に積層される。マスク層となるべき膜をエッチングし、底面が第3の低誘電率膜LOWK3cの表面により構成される配線溝パターンを形成することにより、マスク層SIO2dが形成される。アッシング処理により第1のレジストマスクが除去される。マスク層の配線溝パターンを用いて、底面が第2の低誘電率膜LOWK2cとなるように、配線溝TRCHが形成される。充填される銅金属CUaの頂面から第3の低誘電率膜LOWK3cまでの層がCMP法により除去される。上記各低誘電率膜はFSGよりも誘電率が低く、第2の低誘電率膜LOWK2cは第3の低誘電率膜LOWK3cよりも誘電率が低い。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。更に、その回路基板とその他のチップとを積層して、それらをボンディングワイヤで絶縁基板に支持されないリードへ接続する。

(もっと読む)

高電圧スイッチング回路

【課題】高電圧処理能力および改善された実行能力を有する効率的なスイッチング回路を提供する。

【解決手段】第1および第2のIII−V族トランジスタを有し、第2のIII−V族トランジスタは、第1のIII−V族トランジスタよりも大きな降伏電圧を有する。さらに、第1のIII−V族トランジスタと並列に配置されるシリコンダイオードを有し、この並列配置は、第2のIII−V族トランジスタと直列に接続、効率的な3端子デバイスであり、第1端子は第2のIII−V族トランジスタのゲート、第1のIII−V族トランジスタのソースおよびシリコンダイオードのアノードに結合する。第2端子は第1のIII−V族トランジスタのゲートと結合し、第3端子は第2III−V族トランジスタのドレインと結合する。

(もっと読む)

半導体装置およびその製造方法

【課題】 銅からなる配線上に半田ボールが設けられた半導体装置において、半田ボール中の錫が配線に拡散するのをより一層抑制することができるようにする。

【解決手段】 配線7のランド上面には錫拡散抑制層12が設けられ、この錫拡散抑制層12上に半田ボール13が設けられている。この場合、錫拡散抑制層12は、銅含有率が高い非共晶組成の錫銅系鉛フリー半田によって形成され、リフロー時の加熱温度180℃以上280℃以下で溶融して固化した後同じ加熱温度180℃以上280℃以下で再溶融しないものからなっている。そして、この半導体装置が大きな電流を扱う電源IC等であっても、錫拡散抑制層12の存在により、半田ボール13中の錫が配線7に拡散するのをより一層抑制することができる。

(もっと読む)

半導体チップ、半導体多層回路、及び、半導体チップの製造方法

【課題】表面から裏面に電気信号を伝播させる接続用配線を有する半導体チップを提供するにあたり、従来周知の半導体技術を利用して、製造時間やコストを増加させることなく、電気信号の減衰を抑制する。

【解決手段】半導体基板20と、表面配線30と、接続用配線40を備えている。半導体基板は、第1主表面20aから第2主表面20bに向けて面積が小さくなる開孔25を有している。表面配線は、半導体基板の第1主表面上に形成されている。また、接続用配線は、開孔の側面上に形成されていて、表面配線と接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホール内のコンタクト材料としてカーボンナノチューブ(CNT)を用いつつ、ビア抵抗の低減及びプロセスの容易化をはかる。

【解決手段】配線層間のビアにCNTを用いた半導体装置であって、表面にCu配線17を有する基板上に設けられた層間絶縁膜19と、層間絶縁膜19に形成されCu配線17に接続されるビアホールと、ビアホール内に露出するCu配線17上に選択的に形成され、Cu配線17に対するバリアとなり、且つCNTの成長の助触媒となる第1の金属膜21と、ビアホール内の少なくとも第1の金属膜21上に形成された、CNTの成長の触媒となる第2の金属膜22と、第1及び第2の金属膜21,22が形成されたビアホール内に形成されたCNT23と、を備えた。

(もっと読む)

ミクロスケール構造中でのシード層堆積

半導体装置およびその製造方法

【課題】 銅からなる柱状電極上に半田ボールが設けられた半導体装置において、半田ボール中の錫が柱状電極への拡散をより一層抑制することができるようにする。

【解決手段】 下地金属層8をメッキ電流路とした銅、ニッケルおよび半田の電解メッキをこの順で連続して行なうことにより、メッキレジスト膜25の開口部26内の上部金属層9のランド上面に柱状電極10、錫拡散抑制層11および酸化抑制層12をこの順で形成する。この結果、この半導体装置が大きな電流を扱う電源IC等であっても、酸化抑制層12を含む半田ボール14中の錫が柱状電極10に拡散するのをより一層抑制することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドやシームが発生しにくい構造体とする。

【解決手段】本発明の半導体装置は、半導体基板101に形成された層間絶縁膜103と、層間絶縁膜103に形成されたコンタクト孔104と、コンタクト孔104を埋め込むCu膜107と、コンタクト孔104の内部の側壁に形成され、Cu膜107の下地となる金属含有下地膜13と、を備える。コンタクト孔104の開口に接続している側壁の一部を含む第一の領域11において、金属含有下地膜13は、Cu膜107との界面に金属窒化層106を有する。第一の領域11よりも半導体基板101側の側壁を含む第二の領域12において、金属含有下地膜13は、Cu膜107との界面に金属層105を有する。金属層105の表面におけるCu膜107の成膜速度は、金属窒化層106の表面におけるCu膜107の成膜速度よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】誘電率が低くかつ金属との密着性に優れた絶縁層を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板(シリコン基板)と、基板上に設けられており、炭素−炭素結合を有し、かつ炭素原子数とシリコン原子数との比(C/Si)が2以上である、多孔質SiOCH膜12bと、多孔質SiOCH膜12bに設けられた凹部と、凹部を埋め込むように設けられた金属膜(Cu膜22b)と、Cu膜22bと接しており、凹部内の多孔質SiOCH膜12bの表面に設けられた、改質層31bと、を備え、改質層31bは、多孔質SiOCH膜12bの内部と比較して、C/Si比が小さく、かつO/Si比が同等である。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、バリアメタルの絶縁膜及びCuに対する密着性と、Cu拡散防止とを両立する。

【解決手段】 第1絶縁膜に設けた凹部の側壁に第2絶縁膜を形成し、第2絶縁膜の内側に順に第2絶縁膜との密着性が優れている第1の導電性バリア層、炭素を含有する第2の導電性バリア層、及び、Cu系埋込電極との密着性が優れている第3の導電性バリア層の3層構造のバリア層を介してCu系埋込電極を設けるとともに、前記第1の導電性バリア層と前記第2の導電性バリア層との界面と、前記第2の導電性バリア層と前記第3の導電性バリア層との界面に炭素混合領域を設ける。

(もっと読む)

半導体チップの多チップ・アセンブリを形成する方法

電子デバイス用基板及び電子デバイス

【課題】高周波領域における高周波伝送特性に優れ、コストが安価で、しかも、化学的安定性、電気絶縁性、耐熱衝撃性及び耐熱変形性に優れた絶縁構造を有する電子デバイス用基板及び電子デバイスを提供すること。

【解決手段】環状絶縁部3は、ガラスを主成分とする無機絶縁層33を含み、無機絶縁層33は、縦導体2を取り囲んで、半導体基板1に設けられた環状溝30の内部に充填されている。

(もっと読む)

201 - 220 / 1,123

[ Back to top ]