Fターム[5F033JJ07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566)

Fターム[5F033JJ07]の下位に属するFターム

Fターム[5F033JJ07]に分類される特許

101 - 120 / 1,123

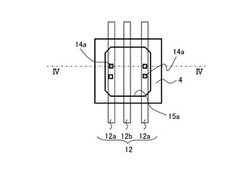

半導体装置、及びその製造方法

【課題】ピラーを確実に配置することが可能な半導体装置、及びその製造方法を提供する。

【解決手段】本発明の一態様にかかる半導体装置30は、内部回路領域20と、内部回路領域20の外側に設けられたI/O領域10と、を備える半導体チップ1と、半導体チップ1とフリップチップ接続されたパッケージ基板6と、半導体チップ1とパッケージ基板6との間に配置され、半導体チップ1の最上層配線層12に含まれる2本以上の接地配線12a上に形成されて、2本以上の接地配線12aを接続する導電性のピラー4と、を備えるものである。

(もっと読む)

バッチ製作された3D相互接続

【課題】ウェハ貫通ビア(TWV)を使用した相互接続において、ダイ区域の消費を低減し、ダイ区域を利用可能とする、バッチ製作された3D相互接続を提供する。

【解決手段】1つまたは複数の垂直相互接続を製作する。ウェハ積層体を形成するために複数のウェハをパターニングおよび積層するステップを含む。ウェハ積層体の1つまたは複数の切断刃の通り道内でウェハ積層体に複数の開口を形成し、導電性材料を複数の開口の側壁に堆積させる。ウェハ積層体は、側壁の導電性材料が、結果として得られる積層ダイの縁部部分に露出されるように、1つまたは複数の切断刃の通り道に沿い、複数の開口を通ってダイシングする。

(もっと読む)

室温金属直接ボンディング

【課題】外からの圧力を用いることなく、低温または室温でウエーハーを貼り合わせる。

【解決手段】貼り合わされたデバイス構造であって、デバイスまたは回路に接続された第1の組の金属ボンディングパッドおよび第1の基板10上の金属ボンディングパッドに隣接する第1の非金属領域を有する第1の基板、デバイスまたは回路に接続された第1の組の金属ボンディングパッドに隣接する第2の組の金属ボンディングパッド、および第2の基板13上の金属ボンディングパッドに隣接する第2の非金属領域を有する第2の基板、および第2の非金属領域に対して第1の非金属領域を接触ボンディングさせることにより形成される第1と第2の組の金属ボンディングパッドの間の接触ボンディングされた界面を含むボンディングされたデバイス構造。第1と第2の基板の少なくとも一方は弾性的に変形され得る。

(もっと読む)

配線形成方法、及び配線形成装置

【課題】絶縁層が積層された導電層に該絶縁層を貫通するカーボンナノチューブが接続される配線構造にて電気的特性を向上することのできる配線形成方法、及び該方法を用いる配線形成装置を提供する。

【解決手段】

下部配線層32に積層された絶縁層34を貫通するホール35に、その内表面の全体が含まれるように触媒層36,37を形成した後、ホール35の内部にシースShが形成され、且つホール35の内壁面35aに対するシースの厚さがホール35の底壁面35bに対するシースShの厚さよりも小さくなるようにプラズマを生成する。そして、ホール35の内壁面35aに形成された触媒層36,37をプラズマ中のスパッタ粒子Spによって除去した後、ホール35の底壁面35bに残された触媒層36,37を用いて該底壁面35bからカーボンナノチューブ38を形成する。

(もっと読む)

ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法

【課題】ナノ物体を外部電気システムに接続する素子、及びその素子を作る方法を提供する。

【解決手段】特に分子の特性評価に適用される本発明によると、以下を備える素子が作られる:ナノ物体(2)に接続される上部接触パッド(8)を備えた上部層(16);外部電気システム(4)に接続される下部接触パッド(12)を備えた下部層(18);前記下部層上にあり、前記下部パッドと接触する電気的貫通ビア(22)を備えた接着層(20);前記接着層と前記上部層の間にあり、前記上部パッドを前記下部パッドに接続するための導電ライン(25)及び電気的ビア(26)を備えた少なくとも2つの層(22、24)。

(もっと読む)

電子デバイス及びその製造方法

【課題】バンプを排除した積層構造を備える電子デバイス、及びその製造方法を提供する。

【解決手段】本発明に係る電子デバイス1は、積層された複数枚の基板11〜13を含む。複数枚の基板は、それぞれ、板面を重ね合わせて積層され、1以上の貫通電極2を含んでいる。また、1以上の貫通電極2は、複数枚の基板11〜13のうち、2枚以上の基板11〜13にわたって延在する連続導体である。本発明に係る電子デバイス1は、このように、各基板の板面同士が重ね合わせられ、2枚以上の基板11〜13にわたって延在する連続導体である貫通電極2を備えている。したがって、本発明に係る電子デバイスは、複数枚の基板11〜13が、バンプを用いることなく、積層された構造を有している。

(もっと読む)

合金材料、回路基板、電子デバイス及びその製造方法

【課題】凝固点が低く低温溶融作業が可能でありながら、凝固後の融解点が高くなる温度階層(hierarchy)を有する電気伝導体用合金材料、この合金材料による電気伝導体を有する回路基板、この回路基板を用いた電子デバイス及びそれらの製造方法を提供すること。

【解決手段】微細空間を充填する合金材料であって、Biと、Snと、Agとを含有し、融解点が257℃以上で、凝固点が240℃以下である。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】銅又は銅合金からなる配線との密着性が高いバリアメタル層を備え、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置では、半導体基板100の上方に配置された絶縁膜106と、絶縁膜106中の溝に配置され、銅又は銅合金からなる配線115とを備え、絶縁膜106と配線115との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、非晶質構造を有する第1のバリアメタル層109と第1のバリアメタル層109の上に配置された多結晶構造を有する第2のバリアメタル層110からなる積層構造であり、第2のバリアメタル層110には銅が含まれており、第2のバリアメタル層110中の金属に占める銅の割合は50at%以下である。

(もっと読む)

半導体装置

【課題】貫通電極の形成に時間を要さず、貫通電極内でのボイドの発生を抑制できる半導体装置、およびこの半導体装置の製造方法を提供すること。

【解決手段】半導体装置1は、孔111が形成された絶縁性あるいは半導体の層11と、層11の孔111内に設けられた貫通電極12と、を備える。貫通電極12は、シード層121と、めっき層122と、を備える。シード層121は、孔111の底面111Aを覆う。また、シード層121は、孔111の側面111Bのうち、孔111の開口から、孔111の開口と孔111の底面111Aとの間の所定の位置までの第1の領域を未被覆とし、この第1の領域(未被覆領域)111B1を除いた第二の領域を被覆している。めっき層122は、シード層121と、未被覆領域111B1の少なくとも一部を覆う。

(もっと読む)

半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路装置用バリア材

【課題】従来のルテニウムバリア材と同様に優れた銅拡散の抑制効果を有し、供給性の点で問題がなく、比較的低コストの金属又はその金属を含む金属間化合物からなる新規な半導体集積回路装置用バリア材の探索方法及び当該探索方法によって探索される半導体集積回路用バリア材を提供する。

【解決する手段】バリア膜若しくはバリア膜とシード膜からなる複合膜の上に銅配線層を有する半導体集積回路装置の前記バリア膜を構成するバリア材として、単位結晶格子の最近接原子間距離(DM)がルテニウムの単位結晶格子の最近接原子間距離(DRu)に近い領域、具体的には、オングストローム(Å)単位で−0.200Å<(DM―DRu)<0.12Åの関係にあって、かつ融点若しくは変態点が650ケルビン(K)以上である金属又は金属間化合物を選択することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ヒートシンクに生じる不具合を低減すること。

【解決手段】半導体装置は、第1面及び第2面を有し、第1面と第2面とを貫通するバイアホールを有する半導体基板と、第1面上に、バイアホールの開口と少なくとも部分的に重複するように形成された配線又は電極と、第2面上に形成され、バイアホールの開口と少なくとも部分的に重複する開口を有する応力緩衝層と、応力緩衝層上からバイアホールの内壁面に沿って延在し、配線又は電極と電気的に接続されたヒートシンクと、を備える。バイアホールの第2面における開口の大きさは、第1面における開口の大きさよりも大きい。応力緩衝層の熱膨張係数は、ヒートシンクの熱膨張係数未満である。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線を高信頼性化する。

【解決手段】一つの実施形態によれば、半導体装置は、第1の配線材、開口部、及び電極端子部が設けられる。第1の配線材は、半導体基板上の第1の層間絶縁膜上に設けられ、配線層として用いられる。開口部は、第1の配線材上に設けられた第2の層間絶縁膜をエッチングして形成される。電極端子部は、開口部及び開口部周囲の第2の層間絶縁膜上に設けられ、第1の配線材に接するバリアメタル膜、シードメタル膜、及び第2の配線材が開口部を覆うように積層形成され、第2の配線材の上部及び側面に被覆メタル膜が形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

材料を付着させる方法

【課題】改良された付着プロセスを提供すること。

【解決手段】ビームを使用して、自発的反応の開始をサポートする条件を提供するように準備された表面の領域における前駆体ガスの自発的付着によって、材料を、所望のパターンに付着させる。いったん反応が開始されると、ビームが存在しなくなっても、反応が開始された表面の領域において反応は継続する。

(もっと読む)

半導体装置

【課題】半導体装置の小型化、特に、狭ピッチ化に対する技術を提供する。

【解決手段】半導体チップ1C上に設けられたパッド2と、プローブ領域10Aおよび接続領域10Bのパッド2上に開口部11を有し、半導体チップ1C上に設けられたパッシベーション膜3と、接続領域10Bのパッド2上に開口部12を有し、パッド2上およびパッシベーション膜3上に設けられたパッシベーション膜5と、パッド2と電気的に接続され、接続領域10B上およびパッシベーション膜5上に設けられた再配線7とを備える。接続領域10Bより半導体チップ1Cの外周部側に設けられたプローブ領域10Aのパッド2にプローブ痕100が存在し、接続領域10Bから半導体チップ1Cの中央部側に延びて再配線7が存在している。

(もっと読む)

101 - 120 / 1,123

[ Back to top ]