Fターム[5F033JJ07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566)

Fターム[5F033JJ07]の下位に属するFターム

Fターム[5F033JJ07]に分類される特許

81 - 100 / 1,123

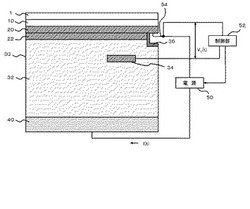

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に形成された開口部の側壁全体を均一に成膜することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一実施形態に係る半導体装置の製造方法は、底壁及び複数の凹部を有する側壁により構成された開口部を素子が形成された半導体基板に形成し、前記開口部側から蒸着又はスパッタリングを行い、前記底壁及び前記側壁の各凹部の前記底壁側に成膜部材を堆積させ、前記半導体基板に所定の電圧を印加しつつスパッタリングを行うことにより前記成膜部材を前記側壁の各凹部の前記開口部側に堆積させることを特徴とする。

(もっと読む)

半導体積層体の製造方法

【課題】信頼性の高い半導体積層体を製造することのできる半導体積層体の製造方法を提供する。

【解決手段】貫通電極用溝2が形成されたウエハ1の貫通電極用溝2を有する面に、半導体加工用テープ4を介して支持体5を積層する工程(1)と、ウエハ1を半導体加工用テープ4と反対側の面から研削し、貫通電極用溝2を露出させる工程(2)と、露出した貫通電極用溝2に電極部6を形成する工程(3)と、ウエハ1の半導体加工用テープ4と反対側の面に封止樹脂層7を形成する工程(4A)と、封止樹脂層7を介してウエハ1にダイシング用テープ8を貼り合わせ、半導体加工用テープ4及び支持体5を剥離する工程(4B)と、ウエハ1を個片化して半導体チップを作製する工程(5)と、前記半導体チップを、封止樹脂層7を介して他の半導体チップ又は基板に積層する工程(6)とを有する。

(もっと読む)

電極構造及びその製造方法

【課題】ウェハハンドリングが容易であり、高精度の位置合わせを必要とせず、ビアホールとして機能する開口部を浅く形成でき、さらに開口部を埋め込む第1電極と基板との界面の割れを防止できる電極構造、及びその製造方法を提供することにある。

【解決手段】基板に、第1主表面側から、深さが基板の厚さよりも小さい開口部33を形成する。次に、開口部を埋め込む第1電極35を形成する。次に、第1主表面と対向する基板を第2主表面側から薄層化して、開口部の深さよりも大きい厚さとする。次に、第2主表面側111bから開口部の底面33bへ向けて、基板111に切り込みを入れる39ことによって、第2主表面側から第1電極を露出させる。次に、切り込みを埋め込む第2電極44を形成する。

(もっと読む)

半導体装置の製造方法

【課題】膜の形成によって生じる半導体基板の反りを緩和できる、半導体装置の製造方法を提供する。

【解決手段】SiC半導体基板10の主面上にイオン注入用マスク材18を形成する。マスク材は半導体基板とは異なる熱膨張係数を有する。レジスト膜20をマスクとしてドライエッチングにより複数の装置形成領域の間の領域上(ダイシングライン)14に切欠き部16aを有するマスク用膜16を形成する。イオン注入などの工程を経て半導体装置を形成後、ダイシングラインに沿って各装置形成領域に分離する。

(もっと読む)

半導体装置、電子デバイス、及び、半導体装置の製造方法

【課題】 より信頼性の高いCu−Cu接合界面を有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体装置1を、第1の配線18を含む第1半導体部10と、第1半導体部10と貼り合わせて設けられ、第1の配線18と電気的に接合された第2の配線28を含む第2半導体部20とを備える構成とする。さらに、半導体装置1は、酸素に対して水素よりも反応し易い金属材料と酸素とが反応して生成された金属酸化物17bを備える。そして、この金属酸化物17bを、第1の配線18及び第2の配線28の接合界面Sj、並びに、第1の配線18及び第2の配線28の少なくとも一方の内部を含む領域に拡散させた構成とする。

(もっと読む)

半導体基板、その製造方法、および電子装置

【課題】カーボンナノチューブを用いた特性が良好な半導体基板、その製造方法、および電子装置を提供することにある。

【解決手段】

本発明の一態様による半導体基板は、一主面に下部電極を有する基板と、前記基板上の前記下部電極以外の部分に設けられた層間絶縁膜と、前記下部電極の上に設けられた触媒層と、前記触媒層上に設けられ、前記下部電極の一主面に垂直な方向に延伸する複数のカーボンナノチューブと、前記カーボンナノチューブ上に設けられ、前記下部電極と対向する上部電極と、前記触媒層および前記カーボンナノチューブの前記触媒層側の端部を覆う第1の埋め込み膜と、前記カーボンナノチューブの他端部の間に満たされ、前記第1の埋め込み膜よりも高密度のである第2の埋め込み膜と、を有する。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供する。

【解決手段】基板上に設けられた層間絶縁膜40に開口部48を形成する工程と、開口部48の側面上および底面上、ならびに層間絶縁膜40上に第1金属材料からなる第1膜10を形成する工程と、第1膜10上であって、開口部48内および層間絶縁膜40上に、第1金属材料よりも電気陰性度が小さい第2金属材料からなる第2膜20を形成する工程と、第2膜20上に、第2金属材料よりも電気陰性度が小さい第3金属材料からなる第3膜30を形成する工程と、熱処理する工程と、開口部48外に位置する第1膜10および第2膜20、ならびに第3膜30を研磨によって除去する工程と、を備える。

(もっと読む)

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した性能と高い生産性とを実現する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態によれば、メモリセルアレイ部と、第1平面内においてメモリセルアレイ部と並置されたコンタクト部と、を備えた不揮発性半導体記憶装置が提供される。メモリセルアレイ部は、積層体、半導体層、メモリ膜を含む。積層体は、第1平面に対して垂直な第1軸に沿って積層された複数の電極膜とそれらの間の電極間絶縁膜とを含む。半導体層は電極膜の側面に対向する。メモリ膜は電極膜と半導体層との間に設けられ電荷保持層を含む。コンタクト部は、コンタクト部絶縁層と複数のコンタクト電極とを含む。コンタクト部絶縁層は、コンタクト部絶縁膜と粒子とを含む。コンタクト電極はコンタクト部絶縁層を第1軸に沿って貫通する。コンタクト電極は電極膜に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】結晶欠陥が可及的に少なく、従来よりも抵抗率の低い高質のグラフェンを備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板の上方に設けられた配線とを具備する。前記助触媒層のうち前記触媒層と接触している部分は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向しているか、または、前記助触媒層のうち前記触媒層と接触している部分は、アモルファス構造もしくは微結晶構造を有する。前記触媒層は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向する。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

半導体装置、製造方法、および電子機器

【課題】製造コストの低減を図ることができる。

【解決手段】シリコンウェハ31の上面側の内部にメタルパッド32が形成され、シリコンウェハ31の上面にガラスシール材33が積層され、メタルパッド32がシリコンウェハ31の上面に露出するようにシリコンウェハ31およびガラスシール材33に加工された開口部にストッパ層34が形成される。そして、シリコンウェハ31の下面からストッパ層34まで開口するように縦孔35が形成され、縦孔35の先端部においてストッパ層34を介してメタルパッド32に電気的に接続され、シリコンウェハ31の下面まで延在するようにメタルシード層37が形成される。本発明は、例えば、固体撮像装置に適用できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 はんだからなるバンプの形成工程中やフリップチップ実装時に、スズのようなはんだ成分がバンプ電極のアンダーバリアメタルを透過してその下のパッド電極と反応し、バンプとパッド電極間の接合信頼性が低下することを防止する。

【解決手段】 半導体基板1上に形成されたパッド電極3とはんだからなるバンプ8間にアンダーバリアメタル6が形成される。アンダーバリアメタル6は保護絶縁膜4に形成された開口5に露出するパッド電極3上から開口5周囲の保護絶縁膜4上までを被覆する。しかしバンプ8の底面はアンダーバリアメタル6より小さく、望ましくは開口5より小さく、且つ開口5内部領域の垂直上方に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

81 - 100 / 1,123

[ Back to top ]