Fターム[5F033JJ17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010)

Fターム[5F033JJ17]の下位に属するFターム

Fターム[5F033JJ17]に分類される特許

161 - 180 / 437

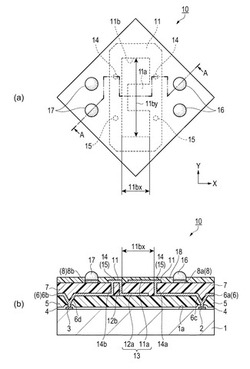

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

半導体装置の製造装置

【課題】装置の高いスループットを維持しつつ、バリアメタルの酸化工程の追加や異なる種類のシード層の積層、バリア層の積層等を行い配線の信頼性を向上させる。

【解決手段】薄膜の合金シード層を成長させるチャンバー、または、薄膜のバリアメタルを成長させるチャンバーのうち、最も短いタクト時間のチャンバー数を最も少なくして、あるいは、統一して1台の装置で専用に用い、タクト時間の長い工程のチャンバーを2または、3チャンバー以上にすることにより、薄膜工程のチャンバー間バラツキを無くして、装置のスループットを向上させる。

(もっと読む)

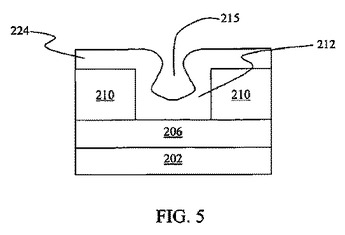

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

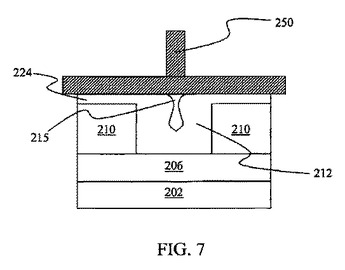

相変化メモリデバイスに電極を形成する方法

サブリソグラフィックな寸法又は高アスペクト比を含む、小寸法の開口内に電極材料を均一に形成する方法を提供する。この方法は、内部に形成された開口を有する絶縁層を提供するステップと、開口の上部及び内部に非等質的導電又は準抵抗性材料を形成するステップと、導電材料を移動化して開港内に圧縮するステップとを有する。この方法は、導電又は準抵抗性材料における空孔又は欠陥密度を堆積されたままの状態に対して低減する。移動化するステップは、押出又は熱的リフローによって達成され、空隙又は欠陥を合体、崩壊、染み透り又は他の方法によって堆積したままの導電又は準抵抗性材料から除去する。  (もっと読む)

(もっと読む)

薄膜素子およびその製造方法

【課題】耐熱性の高い仮基板から耐熱性の低いフィルム基板に移載して形成薄膜トランジスタパネルにおいて、絶縁膜の貫通孔内に設けられた有底筒状の画素電極(薄膜)の底部周辺部が破損しにくいようにする製造方法の提供。

【解決手段】仮基板51上に分離層52、下地絶縁膜1およびゲート絶縁膜4を形成する。下地絶縁膜1およびゲート絶縁膜4に貫通孔12を形成して、分離層52の上面側に凹部12aが形成される。貫通孔12および凹部12aの部分に有底筒状の画素電極13を形成する。画素電極13およびゲート絶縁膜4上に窒化シリコン等からなる補強膜41を形成し、その上にフィルム基板42を接着層43を介して接着した後、仮基板51および分離層52を除去する。この状態では、画素電極13の底部が下地絶縁膜1の下側に突出されるが、補強膜41により、画素電極13の底部周辺部が破損しにくいようにすることができる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通孔底部にノッチを有する半導体装置のノッチ部に被覆性良好な連続した金属膜を積層するプロセスを提供し、半導体装置の歩留まりと信頼性向上をはかること。

【解決手段】ノッチ部を含む貫通孔にCVD絶縁膜を積層した後に、バリア層およびシード層のメタル層をスパッタ法により形成する。メタル層のスパッタ成膜中に基板バイアス(負電圧)を印加して、アルゴンやクリプトン等の希ガスのプロセスガスイオンを貫通孔内部へ引き込み、既にある程度貫通孔底部に積層したメタル層をスパッタエッチングするか、貫通孔底部にメタル層を積層すると同時にスパッタエッチングしたメタル材料を貫通孔底部周辺のノッチ部分へ飛散させる。飛散したメタル材料はノッチ部分の絶縁膜上に付着し積層する。Ar+イオン等により飛散されたメタルは高いエネルギーを有する為、メタル層がノッチ内部へ強固に付着する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクト歩留を向上させる、スタックドコンタクト構造を有する半導体装置を提供する。

【解決手段】NAND型フラッシュメモリのビット線コンタクトには、スタックドコンタクトを構成する第1のコンタクト開口部CH1、第2のコンタクト開口部CH2a、及び第3のコンタクト開口部CH2bが設けられる。下層の第1のコンタクト開口部CH1はビット線コンタクトの中央部に配置され、上層の第2のコンタクト開口部CH2aはビット線コンタクトの左部に配置され、その中心位置がビット線コンタクトの中心位置に対して第2のコンタクト開口部CH2aのズレ量だけ左方向に配置され、上層の第3のコンタクト開口部CH2bはビット線コンタクトの右部に配置され、その中心位置がビット線コンタクトの中心位置に対して第3のコンタクト開口部CH2bのズレ量だけ右方向に配置される。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

半導体装置、半導体装置の作製方法

【課題】支持基板上に、単結晶半導体層を多層構造とした、多層集積回路を形成する場合の、工程数の簡略化を図る。また同集積化の向上を図る。

【解決手段】複数の半導体素子が絶縁層を介して積層される半導体装置において、絶縁層を介して半導体素子を構成する半導体層が積層された構造を有し、一の半導体層が配線とコンタクトする領域が、絶縁層を介して設けられる他の半導体層と重畳するように配置された構成とする。当該コンタクトする領域は、該一の半導体層に設けられる一導電型不純物領域から延在するシリサイド層によって形成される。すなわち、一の半導体素子と配線とのコンタクト領域をシリサイドで形成すると共に上層半導体素子と重畳する位置に配置させ、該半導体素子を構成する一導電型不純物領域と配線とのコンタクト領域との間をシリサイドで連結する構成を有する。

(もっと読む)

半導体基板の電解めっき方法および電解めっき装置

【課題】貫通孔を有するシリコンウエハの貫通孔にオーバーハング形状や内部ボイドがなくめっきを充填する方法を提供すること。

【解決手段】シリコンウエハ内の貫通孔開口部と同位置に開口部を有するプレートを一定の距離をおいてシリコンウエハの貫通孔開口部にプレート開口部を合わせて、めっき電極側に向けて配置してめっきを行う。プレート開口径は貫通孔開口径より少し小さくする。プレート開口径と貫通孔開口径Rの差を2xとしたとき、x/Rを0.1〜0.3、シリコンウエハとプレートの距離を0.05mm〜1.0mmとしたときに、前記課題を実現できる。プレートは、多孔質セラミックのような絶縁体でかつ多孔質材料が望ましく、シリコンウエハ表面のめっき成長も抑制できる。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置70には、積層形成される配線膜6及び10から構成される配線層が設けられる。キャップ膜3上に形成される層間絶縁膜4の第1の開口部には、配線膜6が埋設される。配線膜6の底部及び側面部にはバリアメタル膜5が設けられる。層間絶縁膜4及び配線膜6上に形成されるキャップ膜7及び層間絶縁膜8の第2の開口部には、配線膜10が埋設される。配線膜10の底部及び側面部にはバリアメタル膜9が設けられる。層間絶縁膜8及び配線膜10上に形成される。配線膜10は配線膜6上に設けられ、配線膜10の端部は配線層6の端部よりも内側に設けられる。

(もっと読む)

基板モジュールおよびその製造方法ならびに電子機器

【課題】基板モジュールの製造工程中において、絶縁層の剥離ならびに接続電極の断線および剥離が発生する虞があった。

【解決手段】基板モジュール1では、接続電極4が基板2の第一の表面2a上に設けられており、第一の貫通孔部5が接続電極4の裏面に達するように基板2の厚み方向に貫通しており、第一の貫通孔部5の内部には貫通電極6が設けられている。貫通電極6は接続電極4の裏面に対向する部分に凹部6aを有し、貫通電極6の上部は貫通電極6の側部よりも分厚い。貫通電極6は、基板2の第二の表面2b上にも設けられており、第二の表面2b上において配線電極7に接続されている。絶縁層8が配線電極7の表面を覆うように第二の表面2b上に設けられており、貫通電極6の凹部6a内にも設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセルトランジスタのコンタクト抵抗を低減する。

【解決手段】半導体装置70には、半導体基板1上に複数の絶縁ゲート型電界効果トランジスタが設けられる。絶縁ゲート型電界効果トランジスタのゲートの間に形成され、側面が側壁絶縁膜8及び絶縁膜9により絶縁ゲート型電界効果トランジスタのゲートと分離された自己整合コンタクト開口部の底部には凹部形状のポリシリコンプラグ11が設けられる。ポリシリコンプラグ11上にはバリアメタル膜12が設けられる。バリアメタル膜12上には、自己整合コンタクト開口部を覆うように金属プラグ13が埋設される。

(もっと読む)

半導体装置及びその製造方法

【課題】バリア膜を薄くする場合であっても良好なバリア性を確保し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に形成された第1の導電体32と、半導体基板上及び第1の導電体上に形成され、第1の導電体に達するコンタクトホール52と、コンタクトホールの上部に接続された溝54とが形成された、酸素を含む絶縁膜48と、コンタクトホールの側面並びに溝の側面及び底面に形成された酸化ジルコニウム膜62と、コンタクトホール内及び溝内における酸化ジルコニウム膜上に形成されたジルコニウム膜64と、コンタクトホール内及び溝内に埋め込まれたCuより第2の導電体70とを有している。

(もっと読む)

半導体装置の製造方法

【目的】パターン密度の違いによるエッチング差を抑制する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上にポロジェン材料を含む絶縁膜を形成する工程(S104)と、前記絶縁膜に含まれる前記ポロジェン材料の一部を除去する工程(S106)と、前記ポロジェン材料の一部が除去された前記絶縁膜に前記絶縁膜の底部を残すように開口部を形成する工程(S112)と、前記絶縁膜に含まれる前記ポロジェン材料の残部を除去する工程(S114)と、前記開口部の前記底部をエッチングする工程(S116)と、を備えたことを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】データ線から発生する電気力線が画素電極に進入することを防止し、開口率を大きくすることができる液晶表示装置を提供する。

【解決手段】第1基板100Aは、データ線12を覆う無機絶縁膜15と、データ線12の上方において無機絶縁膜15上に設けられた突起状の有機絶縁膜21と、有機絶縁膜21を覆い、かつ、上方から見たときにデータ線12を覆うシールド共通電極26と、を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、コンタクトプラグの高抵抗化を抑制することができ、また当該コンタクトプラグの構成材料のソース・ドレイン領域への拡散が起こらず、かつ簡略な製造プロセスにより作製可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ゲート電極4、第一の層間絶縁膜7、第一のコンタクトプラグ8、第二の層間絶縁膜9および第二のコンタクトプラグ10を有する。第一の層間絶縁膜7の上面は、ゲート電極4の上面と同じ高さ位置である。第一のコンタクトプラグ8は、第一の層間絶縁膜7の膜厚方向に貫通して形成され、下面においてソース・ドレイン領域5と電気的に接続され、第一の電気抵抗率を有する。第二のコンタクトプラグ10は、第二の層間絶縁膜9の膜厚方向に貫通して形成され、下面において第一のコンタクトプラグ8の上面と電気的に接続され、第一の電気抵抗率より低い第二の電気抵抗率を有する。

(もっと読む)

161 - 180 / 437

[ Back to top ]