Fターム[5F033JJ17]の内容

半導体集積回路装置の内部配線 (234,551) | 層間接続のコンタクト層の材料 (22,060) | 金属及びその合金(シリサイドを除く) (14,566) | 高融点金属 (7,010)

Fターム[5F033JJ17]の下位に属するFターム

Fターム[5F033JJ17]に分類される特許

81 - 100 / 437

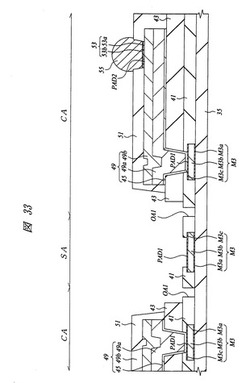

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】不均一な結晶相の形成を抑制してオーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成され、コンタクトメタル電極の結晶配向性と整合する結晶配向性を有する拡散障壁層200と、拡散障壁層200上に形成されたAl配線160を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】オーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成された第1のAl配線160と、第1のAl配線160上に形成された拡散障壁層180と、拡散障壁層180上に形成された第2のAl配線200を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

Cu配線の形成方法

【課題】配線形成後に500℃以上の高温プロセスが存在する場合に適用可能なCu配線を形成すること。

【解決手段】500℃以上の温度の処理をともなう後工程が施されるCu配線の形成方法は、表面にトレンチおよび/またはホールを有する基板上の少なくともトレンチおよび/またはホールの底面と側面に、Cuの格子面間隔との差が10%以内の格子面間隔を有する金属からなる密着膜を形成する工程と、密着膜の上に前記トレンチおよび/またはホールを埋めるようにCu膜を形成する工程と、 Cu膜形成後の基板に350℃以上のアニール処理を行う工程と、Cu膜を研磨してCu膜のトレンチおよび/またはホールに対応する部分のみを残存させる工程と、研磨後のCu膜にキャップを形成してCu配線とする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

相互接続構造およびこれを形成する方法(細い相互接続開口のための導電性構造)

【課題】電気的抵抗が低い相互接続構造、および、かかる相互接続構造を形成する方法を提供する。

【解決手段】相互接続構造は、少なくとも1つの開口を含む誘電物質を含む。少なくとも1つの開口内には、任意のバリア拡散層、結晶粒成長促進層、凝集めっきシード層、任意の第2のめっきシード層、および導電性構造が配置される。典型的にはCuである金属含有導電性物質を含む導電性構造は、バンブー微細構造を有し、平均グレイン・サイズが0.05ミクロンよりも大きい。いくつかの実施形態では、導電性構造は、(111)結晶方位を有する導電性結晶粒を含む。

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

半導体装置

【課題】駆動安定性を高め、積層工程での歩留まりを向上させ、実装形態での長期信頼性を向上させた薄型半導体チップの積層パッケージを実現する。

【解決手段】チップ表面に半導体素子110と、半導体素子110に信号を供給する配線と信号用電極と電源用電極とグランド用電極を有し、チップ裏面に信号用電極と電源用電極とグランド用電極を有し、チップ表面の電極とチップ裏面の電極とを電気的に接続する貫通配線を有し、チップの裏面を覆い、グランド用電極と接続した導体層120が形成されている複数の半導体チップ500、501とインターポーザ502とが積層されている半導体パッケージ。

(もっと読む)

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体基板上のスルーインターコネクトを製造する方法

半導体基板のスルーインターコネクトを製造する方法は、基板の第1側部上に基板を部分的に通るビアを形成するステップと、第1側部上及びビア内に電気絶縁層を形成するステップと、絶縁層上にビアを少なくとも部分的にライニングする導電層を形成するステップと、ビア内の導電層上に第1コンタクトを形成するステップと、ビア内の、少なくとも絶縁層まで基板の第2側部から基板を薄層化するステップとを含む。また、本方法は、第1コンタクトと電気接続状態にある第2コンタクトを基板の第2側部に形成するステップをも含み得る。本方法は、ウエハスケールのインターコネクト要素を形成するように半導体ウエハ上で実行可能である。さらに、インターコネクト要素を、発光ダイオード(LED)システムのような半導体システムを構築するのに使用可能である。 (もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、半導体基板が樹脂層により被覆されない構造のため、半導体基板端部が欠け易い問題があった。

【解決手段】本発明の半導体装置1では、シリコン基板2上面に配線層13が形成され、配線層13を被覆するように樹脂層14が形成される。配線層13上には樹脂層14の開口領域15を介してバンプ電極18が形成される。また、保護シート19は、シリコン基板2の裏面及びシリコン基板2の側面20の一部を被覆する。この構造により、シリコン基板2の裏面側では、保護シート19が緩衝材として機能し、シリコン基板2のチッピングが防止される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の再配線層において配線を狭ピッチ化して隣接する配線間距離が著しく近接しても、配線間でイオンマイグレーションを効果的に抑制する。

【解決手段】一方の主面11aに半導体デバイスおよび電極11cが設けられた半導体基板11と、一方の主面11aの上に形成された層間絶縁層12と、層間絶縁層12上において個々の配線パターンに沿って複数形成されたポリイミドからなる樹脂パターン部13と、樹脂パターン部13の上にそれぞれ形成された再配線層14と、再配線層14の上を封止する封止絶縁層15とを有し、樹脂パターン部13の側面13aが、配線パターンの長手方向に垂直な断面において凹凸状とされている。

(もっと読む)

固体撮像装置及びその製造方法

【課題】画素における光のクロストーク等の光学特性を改善することにより、画素の微細化を実現することができる固体撮像装置を提供することである。

【解決手段】半導体基板に配され、光を電荷に変換する複数の光電変換素子(11)と、半導体基板に配され、光電変換素子により変換された電荷を電圧に変換する第1の半導体領域(13)と、第1の半導体領域に接続されたゲート電極を有し、第1の半導体領域により変換された電圧を増幅する増幅MOSトランジスタと、半導体基板を覆う絶縁膜(23)と、絶縁膜上に配される金属配線層(42)と、第1の半導体領域及び増幅MOSトランジスタのゲート電極とを金属配線層を介さず接続する第1の導電体(21)と、半導体基板に配され、第1の半導体領域とは異なる第2の半導体領域(18)と、第2の半導体領域と金属配線層の少なくとも一部とを接続する第2の導電体とを有する固体撮像装置が提供される。

(もっと読む)

バリヤ層、成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の第2の金属を含む第2金属含有膜を形成する際に、下地膜としてRu等の第1の金属を含む第1金属含有膜を介在させることにより上記第2金属含有膜を効率的に形成する。

【解決手段】底面に金属層3が露出する凹部2を有する絶縁層1が表面に形成された被処理体に対して成膜処理を施す成膜方法において、第1の金属を含む第1金属含有膜を形成する第1金属含有膜形成工程と、前記第1金属含有膜形成工程の後に行われ、前記凹部に埋め込まれる埋め込み金属に対してバリヤ性を有する第2の金属を含む第2金属含有膜を形成する第2金属含有膜形成工程とを有する。これにより、下地膜としてRu等の第1の金属を含む第1金属含有膜を介在させて上記第2金属含有膜を効率的に形成する。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

貫通電極基板及びその製造方法、並びに貫通電極基板を用いた半導体装置

【課題】基板の表裏を導通する導通部における電気特性を向上した貫通電極基板及びそれを用いた半導体装置を提供すること。

【解決手段】本発明の貫通電極基板100は、表裏を貫通する貫通孔104を有する基板102と、貫通孔104内に充填される金属材料を含む導通部106と、を備え、導通部106の一端は、導通部106の他端より面積重み付けした平均結晶粒径が大きい金属材料を少なくとも含む。また、導通部106は、結晶粒径が13μm以上の金属材料を含む。

(もっと読む)

半導体装置の製造方法

【目的】キャップ成膜時に起因するlow−k膜の絶縁性劣化を低減する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に絶縁材料を用いたキャップ膜を形成する工程(S106)と、前記キャップ膜を形成した後に、前記キャップ膜を介して前記前記キャップ膜の下層のシリル化処理を行なう工程(S108)と、前記シリル化処理の後、エッチング法を用いて、前記キャップ膜上から前記絶縁膜内へと続く開口部を形成する工程(S114)と、前記開口部に導電性材料を堆積させる工程(S124)と、を備えたことを特徴とする。

(もっと読む)

81 - 100 / 437

[ Back to top ]