Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

2,121 - 2,140 / 2,960

成膜方法

【課題】 チャージアップダメージの発生を大幅に抑制することが可能なプラズマ処理方法を提供する。

【解決手段】 真空引き可能になされた処理容器22内に設けたプラズマ用電極38に、プラズマ発生用電源から所定の電力を供給してプラズマを生成し、前記処理容器内に収容されている被処理体に対して所定のプラズマ処理を施すようにしたプラズマ処理方法において、前記被処理体に発生するチャージアップ電圧を抑制するために前記プラズマ処理を開始する際に、前記プラズマ用電極へ供給する電力を徐々に増加するように構成する。

(もっと読む)

導体−誘電体構造およびこれを作成するための方法

【課題】導体−誘電体構造およびこれを作成するための方法を提供すること。

【解決手段】導体−誘電体相互接続構造は、パターン形成されたフィーチャをその内部に有する誘電体層を含む構造を用意し、パターン形成されたフィーチャ内の誘電体層の表面にめっきシード層を付着させ、パターン形成されたフィーチャ内のめっきシード層の表面に犠牲シード層を付着させ、犠牲シード層の厚さを逆めっきによって低減させ、パターン形成されたフィーチャ内の犠牲シード層の表面に導電性金属をめっきすることによって作成される。さらに、パターン形成されたフィーチャをその内部に有する誘電体層と、パターン形成されたフィーチャ内の誘電体層の表面のめっきシード層と、パターン形成されたフィーチャ内に位置する不連続な犠牲シード層とを含む構造も提供される。

(もっと読む)

半導体装置の製造方法

【課題】微細な配線構造を形成可能であると共に、製造コストの低い半導体装置の製造方法を提供する。

【解決手段】配線層11上の低誘電率材料からなる第1層間絶縁層13および第2層間絶縁層15のそれぞれを覆うSiO膜14,16を形成する。SiO膜14,16は、CVD法によりSiH4ガスとCO2ガスを用いて、ウェハを350℃〜500℃に加熱して形成する。このようにして形成されたSiO膜14,16は、実質的に窒素を含まないため、シリコン窒化膜等の反射防止膜18を形成する際にアンモニアガスや窒素ガス等の透過を抑制し、第1層間絶縁層13および第2層間絶縁層15に窒素に由来する塩基性物質の吸蔵を抑制する。その結果、レジストポイゾニングを抑制できる。さらに、SiO膜14,16は原料がガスのみであるので液体原料を使用するTEOS膜よりもCVD装置の汎用性が高まり、製造コストを低減できる。

(もっと読む)

半導体装置

【課題】従来、バリアメタル206を敷いてアロイスパイクによる拡散層の突き抜けを抑

えていた。すると、バリアメタル206の影響でコンタクト抵抗の上昇によりPウェル2

08の電位が上昇し、NMOS100の閾値変動等が発生する。そこで、アロイスパイク

等の現象の影響を抑え、かつPウェル208の電位を制御しうる半導体装置を提供する。

【解決手段】NMOS100の幅方向にソース205、P型拡散層301を交互に位置す

るように形成し、バリアメタル206を、Pウェル208上で接合を有するソース205

上には残し、接合を有さないP型拡散層301では除去し、両領域を短絡するようアルミ

電極207を形成する。接合が形成されているソース205はバリアメタル206により

アロイスパイクが抑制され、P型拡散層301ではバリアメタルが除去されているためコ

ンタクト抵抗を下げることができ、P型拡散層301の電位が安定化される。

(もっと読む)

包囲条件を除去するためのプラグの拡大頭部を形成する構成体及び方法

【課題】 相互接続層を形成する場合に侵食されることのないコンタクト開口を形成する技術を提供する。

【解決手段】 絶縁層(34)を貫通するコンタクト開口が真直な側壁部分(42)とお椀形状側壁部分(40)とを有するように形成される。お椀形状側壁部分は絶縁層の上部近くであり底部と比較して上部においてコンタクト開口の拡大直径部分を与えている。導電性物質(46)をコンタクト開口内に形成し下部の導電層(32)と電気的接触を形成する。この導電性物質は拡大頭部(52)を有するプラグ(47)を形成する。この拡大頭部は、存在する場合に、コンタクト開口内のバリア層(45)が爾後の異方性エッチングによってエッチングされることを防止する。従って、例えばアルミニウム等の電気的相互接続層(48)がコンタクトプラグの上側に形成される場合に、そのプラグはエッチストップとして作用しコンタクト開口内のバリア層がエッチングされることを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗特性が改善され、信頼性が向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、下部配線110、層間絶縁膜100、200、拡散防止膜120、240、上部配線230を備えている。層間絶縁膜200は、下部配線110上に形成され、下部配線110の上面が露出するビアホール230aを有する。拡散防止膜240は、ビアホール230aの両側壁に形成される。上部配線230は、ビアホール230aを埋め込み、下部配線110と直接接触する。下部配線110内にはビアホール230aの延びる方向に拡散防止膜120の成分を含む不純物領域130が形成される。

(もっと読む)

半導体素子のストレージノードコンタクトプラグの形成方法

【課題】ストレージノードコンタクト(SNC)プラグの開口面積を増大させ、ストレージノードとSNCプラグとのSACフェイルの発生を防止し、低価格の装備を採用できる半導体素子のSNCプラグの形成方法を提供すること。

【解決手段】ランディングプラグコンタクト35が形成された半導体基板31上に層間絶縁膜36、44を形成するステップと、層間絶縁膜36、44上にラインタイプのSNCマスク45を形成するステップと、SNCマスク45をエッチングマスクとして、層間絶縁膜44を部分エッチングして側壁が拡張された2次ホール46Bを形成するステップと、ホール46B下の層間絶縁膜44、36をエッチングして、コンタクト35の表面を露出させる3次ホール46Cを形成するステップと、ホール46B、46CからなるSNCホール46に埋め込まれるSNCプラグ48を形成するステップとを含む。

(もっと読む)

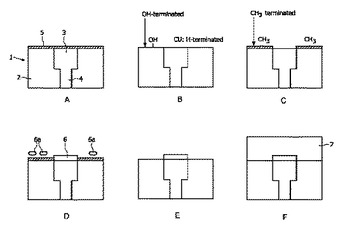

半導体ディバイスのための構造における第2材料内に埋設する第1材料の表面に層を形成する方法

本明細書には、半導体ディバイスのための相互接続構造における

誘電材料(2,100)に埋設した銅線(3,107)の表面にバリア層(6,110)を形成する方法を記載する。このバリア層(6,110)を、蒸着ステップにより銅線(3,107)表面上に選択的に堆積し、また誘電体(2,100)の表面は、蒸着ステップ中にバリア層の形成を抑止するように蒸着前に表面処理する。  (もっと読む)

(もっと読む)

半導体製造方法

【課題】半導体装置の層間膜容量、配線間容量の低減及び微細化を図るとともに、半導体製造工数の低減が可能な半導体製造方法を提供する。

【解決手段】第1のレジストによりヴィアパターン7を形成する工程と、少なくとも前記ヴィアパターン7の一部の周囲を充填するように、第1の層間膜6aを形成する工程と、前記ヴィアパターン7及び前記第1の層間膜6a上に、第2のレジストにより配線パターン8を形成する工程と、少なくとも前記配線パターン8の一部の周囲を充填するように、第2の層間膜6bを形成する工程と、前記配線パターン及び前記ヴィアパターンを選択的に除去して、デュアルダマシン配線溝を形成する工程と、前記デュアルダマシン配線溝を金属層により充填する工程を備える。

(もっと読む)

金属配線とその製造方法、薄膜トランジスタ、電気光学装置、及び電子機器

【課題】液相法を用いて形成され、さらに拡散による不都合を解消するとともに、平坦性をも有した金属配線とその製造方法、さらには拡散や平坦性の低下に起因する特性の低下を防止した薄膜トランジスタと、これを備えた電気光学装置、電子機器を提供する。

【解決手段】基板P上に液相法で形成された金属材料からなる主導電層66、67、81と、主導電層66、67、81上に液相法で形成されたキャップ層68a、82とを備えた金属配線34、35、80aである。キャップ層68a、82は、有機金属又は無機金属塩の溶液が主導電層66、67、81上に配され、焼成されたことによって形成されている。金属配線80aはボトムゲート型薄膜トランジスタ60のゲート電極となっている。

(もっと読む)

半導体装置

【課題】半導体装置のパッド下構造を、押し込み方向、引き剥がし方向、水平方向の力に対して耐性の強いものとする。

【解決手段】半導体装置は、基板上に形成された少なくとも1層の第1絶縁膜と、第1絶縁膜より上部の層に配置された複数のパッドと、を備える半導体チップを備える。半導体チップ上の複数のパッドは、半導体チップの所定のチップエッジ部分に平行に配列される。第1絶縁膜は、各パッドの下部に位置するパッド下部領域に補強パターンを備える。各パッド下領域おいて、第1絶縁膜中の補強パターンの占有率は、各パッド下部領域で認められる所定の範囲内であり、かつ、補強パターンの、所定のチップエッジ部分に対して垂直な方向における占有率は、所定のチップエッジ部分に対して水平な方向の占有率よりも大きいものとする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】マンガンの拡散を防止する層を形成することで、銅マンガン合金層からのマンガンの拡散を抑えて銅配線の低抵抗化を可能とする。

【解決手段】酸化シリコン系絶縁膜11に設けられた凹部12内面に形成された銅マンガン合金層15と該酸化シリコン系絶縁膜11とを反応させて形成されたマンガンシリケート層18と、前記凹部12を埋め込む銅もしくは銅を主体とした材料からなる導電層17とを備えた半導体装置1において、前記銅マンガン合金層15と前記導電層19との間にマンガンの拡散を防止する拡散防止層17を備えたことを特徴とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜をLow−k膜で構成し、低比誘電率を維持したままLow−k膜の密着性を向上させて膜剥がれ等を抑制できる、信頼性の高い半導体装置を提供することにある。

【解決手段】半導体基板と、前記半導体基板上方に形成され、表面に複数の配線からなる第1配線層が形成された第1絶縁膜と、前記第1配線層及び前記第1絶縁膜上に形成された第1キャップ層と、前記第1キャップ層上に形成され、表面に複数の配線からなる第2配線層が形成され、前記第2配線層間に前記第1キャップ層まで達する溝部が形成された第2絶縁膜と、前記溝部に埋め込まれた第3絶縁膜とを備え、前記第3絶縁膜の前記第1キャップ層に対する密着性が、前記第2絶縁膜と前記第1キャップ層との密着性よりも高い構成とするので、Low−k膜の密着性を向上させて、効果的に膜剥がれ等を防止することを可能にできる。

(もっと読む)

プラズマエッチング方法

【課題】ハードマスク膜に対するエッチング選択性が高く、ポリマーの付着やサイドエッチングを抑制可能で、かつポーラスLow−k膜へのダメージや表面荒れが抑制されたプラズマエッチング方法を提供する。

【解決手段】プラズマ処理装置の処理室内で、被エッチング膜102と、該被エッチング膜102より上層に形成されたポーラスLow−k104膜とを有する被処理体を、炭素とフッ素とから構成され、炭素数が2以下のフルオロカーボン化合物と、CO2とを含み、炭素とフッ素と水素とから構成されるハイドロフルオロカーボン化合物を含まない処理ガスを用いてプラズマエッチング処理する。

(もっと読む)

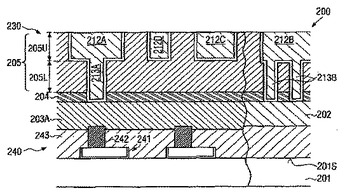

ダミービアの供給によりメタライゼーション層の密着性を向上させる技術

電気的に機能しない金属領域(212B、312B)の下方にダミービア(213B、313B)を供給することにより、後続のプロセスにおいて、金属が層間剥離する危険性が著しく低下する。更に、一実施形態では、形成されるメタライゼーション層(330)の機械的強度は、機能しないオーバーレイ金属領域(312B)のアンカーとしての役割を果たすダミー金属領域(303B)を供給することでさらに一層強化される。加えて、ダミービア(213B、313B)はさらに、電気的に機能する金属領域(212A、212C、212D、312A)と、領域(220A、320A)とともに供給され、これにより、機械的安定性とその電気的パフォーマンスも強化される。  (もっと読む)

(もっと読む)

半導体装置の製造装置及び製造方法

【課題】製造工程における処理の効果を高めた半導体装置の製造装置及び製造方法を提供する。

【解決手段】半導体装置の製造装置は、第1の気圧下で半導体基板に対して第1の処理を行う第1の処理室(10,12,14)と、前記第1の気圧よりも高い第2の気圧下で前記半導体基板に対して前記第1の処理の後処理を行う第2の処理室(20)と、外気から遮断され前記第1の処理室(10,12,14)と前記第2の処理室(20)との間に配置され前記第1の気圧又は前記第2の気圧に室内の圧力を調整可能な圧力調整室(30)と、前記第1の処理室(10,12,14)と前記圧力調整室(30)とを隔てる第1の開閉扉(40)と、前記第2の処理室(20)と前記圧力調整室(30)とを隔てる第2の開閉扉(50)と、前記第1の処理室、前記圧力調整室及び前記第2の処理室との間を前記半導体基板を搬送する搬送装置(60)とを備える。

(もっと読む)

半導体素子及びこの製造方法

【課題】バリア層によって金属間絶縁膜の誘電率が高くなるのを防止して信頼性が向上した半導体素子を提供する。

【解決手段】本発明による半導体素子は、ソース/ドレーン領域を有する半導体基板、前記半導体基板上に形成されたゲート電極、前記半導体基板上に形成されて,第1ダマシンパターンを有する第1のIMD、前記ダマシンパターン内に形成される第1バリア層、前記第1バリア層上に形成される第1金属配線、前記第1ダマシンパターン内に形成される第1メタルキャップ層、が含まれる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】空洞(Air−Gap)構造を有する多層のダマシン配線における目外れビアのメタル形成不良を防止する。

【解決手段】接続孔の形成領域に、選択的に除去可能な絶縁膜で犠牲膜ピラー42を形成した後に、隣接するダマシン配線間に空洞(Air−Gap)45を有する層間絶縁膜44を形成することで、ビアと空洞45を完全に分離する。

【効果】本発明によれば、信頼性の高いビア接続を有し、空洞による寄生容量の低減がなされた多層の埋込配線を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】配線や配線間を接続するプラグ等の内部に含まれているマンガンをその配線や接続プラグの上面に拡散させてマンガンシリケート膜を生成することで、従来のバリア膜よりも低誘電率なバリア膜の形成を可能とする。

【解決手段】絶縁膜11に設けられた凹部12の内部に形成された導電体14上面に、該導電体14上に形成された酸化シリコン系絶縁膜21との反応により生成されたマンガンシリケート膜22が形成されているものである。

(もっと読む)

半導体装置およびその製造方法

【課題】FUSIゲート電極に達するコンタクト部と、ソース・ドレイン層に達するコンタクト部とで深さが異なることに起因する不具合を解消した半導体装置およびその製造方法を提供する。

【解決手段】層間絶縁膜4を厚さ方向に貫通して2つのソース・ドレイン層34上層部のシリサイド層35およびFUSIゲート電極32にそれぞれ達する2つのFUSIコンタクト部41が設けられている。FUSIコンタクト部41は、層間絶縁膜4を貫通するコンタクト開口部CH1内に、完全にシリサイド化されたFUSIコンタクト層411を充填して構成されており、FUSIゲート電極32と同じ高さを有している。

(もっと読む)

2,121 - 2,140 / 2,960

[ Back to top ]