Fターム[5F033MM13]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803) | 配線の断面構造 (9,197) | 2種類以上の導電層よりなる配線 (8,898) | バリア層を含むもの (2,960)

Fターム[5F033MM13]に分類される特許

2,141 - 2,160 / 2,960

半導体装置および半導体装置の製造方法

【課題】マンガンの拡散を防止する層を形成することで、銅マンガン合金層からのマンガンの拡散を抑えて銅配線の低抵抗化を可能とする。

【解決手段】酸化シリコン系絶縁膜11に設けられた凹部12内面に形成された銅マンガン合金層15と該酸化シリコン系絶縁膜11とを反応させて形成されたマンガンシリケート層18と、前記凹部12を埋め込む銅もしくは銅を主体とした材料からなる導電層17とを備えた半導体装置1において、前記銅マンガン合金層15と前記導電層19との間にマンガンの拡散を防止する拡散防止層17を備えたことを特徴とするものである。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜をLow−k膜で構成し、低比誘電率を維持したままLow−k膜の密着性を向上させて膜剥がれ等を抑制できる、信頼性の高い半導体装置を提供することにある。

【解決手段】半導体基板と、前記半導体基板上方に形成され、表面に複数の配線からなる第1配線層が形成された第1絶縁膜と、前記第1配線層及び前記第1絶縁膜上に形成された第1キャップ層と、前記第1キャップ層上に形成され、表面に複数の配線からなる第2配線層が形成され、前記第2配線層間に前記第1キャップ層まで達する溝部が形成された第2絶縁膜と、前記溝部に埋め込まれた第3絶縁膜とを備え、前記第3絶縁膜の前記第1キャップ層に対する密着性が、前記第2絶縁膜と前記第1キャップ層との密着性よりも高い構成とするので、Low−k膜の密着性を向上させて、効果的に膜剥がれ等を防止することを可能にできる。

(もっと読む)

半導体装置の製造方法および半導体装置の製造に用いられる薬液

【課題】エッチングによりダメージを受けた絶縁膜の側壁の過剰なエッチングを抑制し、並びに、その側壁からの吸湿を抑制することができる半導体装置の製造方法およびその方法に使用される薬液を提供する。

【解決手段】半導体装置の製造方法は、下地材料20上に絶縁膜30を設け、絶縁膜上にマスク材料40を設け、マスク材料を利用して絶縁膜をエッチングし、絶縁膜のエッチングによって生成した金属残渣を除去する第1の処理と、エッチングによって形成された絶縁膜の側壁を疎水化する第2の処理と、絶縁膜のエッチングによって生成したシリコン残渣を除去する第3の処理と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】レジストポイゾニングを抑止して微細な配線構造を形成可能な半導体装置の製造方法を提供する。

【解決手段】配線層11上に、キャップ層12、第1層間絶縁膜13、エッチングストッパ層14、第2層間絶縁膜15、ハードマスク層16、ハードマスク層18を順次形成する。第1および/または第2層間絶縁膜13,15はlow−k材料からなる。次いでキャップ層12の表面を露出するビアホール19aを形成する。次いで、ビアホール19aに酸発生剤を含む樹脂、例えば化学増幅型レジスト材料からなる埋込み材21aを充填する。次いで、埋込み材21aにエネルギー線を照射して酸性物質を発生させ、第1および第2層間絶縁膜13,15に吸蔵されていた塩基性物質を埋込み材21aの酸性物質により中和させる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線容量を効果的に低減して、配線の信号遅延を効果的に防止できる半導体装置及びその製造方法を提供すること。

【解決手段】第3の絶縁膜105に、第2の配線層を形成するためのトレンチ116と、接続層を形成するための第1のビアホール117とを形成した後に、このトレンチと第1のビアホール117の内側面にバリア108層を形成する。このバリア層108が内側面に形成されたトレンチ116及び第1のビアホール117を介して、上記第2の絶縁膜104に、第1の配線層101に達する第2のビアホール117を形成する。また、第1の配線層101の表面に形成された酸化層119を除去する。第2のビアホール117を形成する際のエッチングや、酸化層119を除去するプラズマによって、第3の絶縁膜が大幅に改質されて誘電率が大幅に増大することが、バリア層108で防止される。

(もっと読む)

金属−窒化ケイ素、酸化ケイ素、又は酸窒化ケイ素のALD/CVD用のTi、Ta、Hf、Zr及び関連する金属のケイ素アミド

【課題】金属窒化ケイ素ベース膜、金属酸化ケイ素又は金属酸窒化ケイ素ベース膜を形成させるために好適な前駆体の提供。

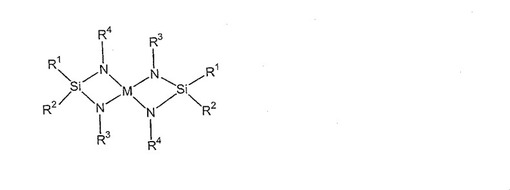

【解決手段】次の構造により表される有機金属錯体。

(式中、Mは、元素周期表の4族から選択される金属であり、そしてR1〜4は、同一又は異なって、ジアルキルアミド、ジフルオロアルキルアミド、水素、アルキル、アルコキシ、フルオロアルキル及びアルコキシ、脂環式、並びにアリールから成る群から選択されることができるが、但しR1及びR2が、ジアルキルアミド、ジフルオロアルキルアミド、アルコキシ、フルオロアルキル及びアルコキシである場合には、それらは連結して環を形成することができる。)。関連化合物もまた、開示されている。上記錯体を用いるCVD及びALD堆積法がまた、含まれる。

(もっと読む)

配線、これを含む薄膜トランジスタ基板、及びその製造方法

【課題】 配線、これを含む薄膜トランジスタ基板、及びその製造方法が開示される。

【解決手段】 本発明の一実施例による配線は、下部構造物上に形成されたバリア膜、前記バリア膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された中間膜、及び前記中間膜上に形成されたキャッピング膜を含むか、又は下部構造物上に形成されたバリア膜、前記バリア膜上に形成された第1中間膜、前記第1中間膜上に形成された銅又は銅合金を含む銅導電膜、前記銅導電膜上に形成された第2中間膜、及び前記第2中間膜上に形成されたキャッピング膜を含む。

(もっと読む)

自己整合銅キャッピング層の形成方法

銅相互接続線(14)上にキャッピング層を形成する方法。その方法は、相互接続線(14)およびそれが埋め込まれた誘電体層を覆うアルミニウム層(20)を供給する工程からなる。これは、堆積および化学的暴露によって達成され得る。ついで構造は、アニーリング、あるいは、例えば窒素原子を含む雰囲気下での、さらなる化学的暴露のような処理に供され、Alの銅線(14)への内部拡散および金属間化合物CuAlNの拡散バリヤを形成する窒化を生じさせる。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】基板上にトランジスタ等の半導体素子とセンサーとを作り込んで設ける場合に、同一工程で作製することにより得られる半導体装置およびその作製方法を提供することを目的とする。

【解決手段】同一基板上に、互いに接する第1の領域および第2の領域を有する第1の半導体膜と、チャネル領域とソースまたはドレイン領域として機能する第3の領域とを有する第2の半導体膜と、第1の半導体膜および第2の半導体膜を覆って設けられた絶縁膜と、絶縁膜上に設けられ且つ第1の領域と電気的に接続する第1の導電膜と、第2の領域と電気的に接続する第2の導電膜とを設け、第1の領域、第2の領域および第3の領域に不純物元素を第1の領域と第2の領域に含まれる不純物元素の濃度が異なるように導入する。

(もっと読む)

半導体装置の製造方法

【課題】金属配線の上層のサイドエッチングの発生を抑制することができる、半導体装置の製造方法を提供すること。

【解決手段】Ti/TiN層16およびBARC層17の不要な部分を除去するための上層メインエッチング工程では、エッチング条件が、Ti/TiN層16およびBARC層17のエッチングレートがAlCu層15のエッチングレートよりも大きくなるような条件とされる。そして、AlCu層15が露出したことが検出されると、上層メインエッチング工程が終了され、上層オーバエッチング工程が開始される。この上層オーバエッチング工程では、エッチング条件が、Ti/TiN層16のエッチングレートとAlCu層15のエッチングレートとがほぼ一致するような条件に変更される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】銅配線上に形成される銅バリア絶縁膜の膜種を選択して、銅配線上に形成されている銅バリア絶縁膜を下地の周囲に形成されている絶縁膜に対して選択的なエッチング除去を可能にする。

【解決手段】銅もしくは銅を主体とした導電性材料からなる配線(第1配線14)と、前記第1配線14上に形成されたバリア絶縁膜21と、前記第1配線14上に形成されたビアホール26とを備えた半導体装置1において、前記バリア絶縁膜21はアモルファスカーボンもしくはダイヤモンドライクカーボンからなり、前記ビアホール26底部の前記バリア絶縁膜21が選択的に除去されていることを特徴とする。

(もっと読む)

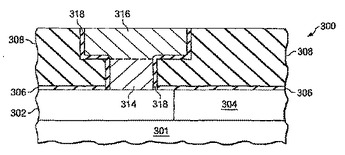

細孔シーリングライナーのデュアルダマシン方法及びデバイスへの統合

デバイスは、細孔シーリングライナーを有するダマシン層を使用し、半導体ボディを含んでいる。金属相互接続(302)からなる金属相互接続層が、半導体ボディ上に形成される。誘電層(308)が、金属相互接続層上に形成される。導電性トレンチフィーチャ(316)及び導電性バイアフィーチャ(314)が、誘電層内に形成される。細孔シーリングライナー(318)が、導電性バイアフィーチャの側壁に沿ってのみ、及び導電性トレンチフィーチャの側壁及び底面に沿って形成される。細孔シーリングライナーは、導電性バイアフィーチャの底面に沿っては実質的に存在しない。  (もっと読む)

(もっと読む)

デュアルダマシン工程を利用した低誘電率物質層内のコンタクト構造形成方法

【課題】デュアルダマシン工程を利用した低誘電率物質層内のコンタクト構造形成方法を提供する。

【解決手段】デュアルダマシン工程を利用したビア形成方法は、リセス部内に低誘電率物質層を覆うようにリセス部の全体側壁上に保護スペーサを保持しつつ、アッシング工程を利用し、低誘電率物質層内のリセス部から対象物質層を除去する。これよって、効果的なコンタクト構造形成方法を提供するデュアルダマシン工程を利用し、低誘電率物質層(low-k materials)内にコンタクト構造を形成する。

(もっと読む)

半導体装置の製造方法

【課題】自己整合コンタクトプラグを形成する層間膜に、窒化シリコン膜のエッチング速度に対するエッチング速度比が100以上となる材料を適用し、コンタクトプラグとビット配線のショートを防止する信頼性の高いコンタクトプラグの形成方法を提供することにある。

【解決手段】上面及び側面が窒化シリコン膜120,121で覆われたビット配線を形成した後、ビット配線を覆って全面に非晶質炭素膜からなる犠牲層間膜126を形成し、犠牲層間膜126および下層層間絶縁膜109を順次にエッチングしてコンタクトホール128,129を形成し、容量コンタクトプラグ113を形成する。その後犠牲層間膜126を除去して容量コンタクトプラグ113の柱を形成し、その上に第3層間絶縁膜を形成し、さらに第3層間絶縁膜を表面から一部除去し、容量コンタクトプラグ113の表面を露出させるようにした。

(もっと読む)

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

一時的なキャップ層を用いる、覆われた、基板を貫通するビアの製造

本発明は、第1の基板の面を反対側の第2の基板の面と電気的に、好ましくは熱的にも接続する少なくとも1つの覆われたビアを有する基板を製造する方法に関する。加工は、第1の基板の面上にトレンチを形成することと、熱処理工程において分解される一時的な犠牲キャップ層上の永久的な層でトレンチを覆うこととを含む。本発明の方法は、永久的な層の存在下であっても痕跡又は汚染を残すことなく犠牲キャップ層の分解生成物を除去する代わりの方法を提供する。このことは、本発明の第1の態様に従って、基板のトレンチにホールを有するオーバーコート層を施すことによって達成される。オーバーコート層におけるホールはキャップ層材料の分解生成物の除去のための空間を残す。本発明の第2の態様において、第2の基板の面から覆われたトレンチを開け、開口部を通じてキャップ層材料を除去することによって解決がもたらされる。本発明の両方の方法は、基板の開口部が一時的なキャップ層の除去の前に永久に覆われている状況においても一時的なキャップ層を使用するという共通の発想に基づくものである。  (もっと読む)

(もっと読む)

非導電性または半導電性の基板に導電性ブッシングを製作する方法

本発明は、特に電気的な用途に適している半導電性基板または非導電性基板に導電性のブッシングを製作する方法に関する。本方法は、前面が少なくとも1つの場所に導電性の接触個所(6)を有している半導電性基板または非導電性基板(13)にその裏面から少なくとも1つの切欠き(7)を設けて、切欠き(1)が前記基板の前面で、1つまたは複数の導電性の前記接触個所が存在していて当該接触個所で完全に覆われる1つまたは複数の場所の下で終わるようにし、次いで、前記基板のそれぞれの前記接触個所と裏側の表面(10,11,12)との間で複数または少なくとも1つの前記切欠き(7)を貫いて導電接続を成立させる導電性構造(9)を前記基板の裏面から塗布することを特徴としている。さらに本発明は、本発明の方法によって設定された形態を備える基板ないしコンポーネントも対象としている。 (もっと読む)

半導体装置の製造方法

【課題】バンプの表面の平坦化を図ることのできる技術を提供する。

【解決手段】最上層配線と同一層の導体膜からなるパッド7と電気的に接続するバリア層30を形成した後、バリア層30上に液体金属化合物を塗布し、さらに熱処理または化学反応処理によりこの液体金属化合物を単体金属膜に還元して平坦な表面形状を有するシード層31を形成する。その後、シード層31の平坦な表面形状をトレースして、シード層31上に平坦な表面形状を有するバンプ8をメッキ法により形成する。

(もっと読む)

触媒及び化学気相蒸着法を用いて銅配線及び薄膜を形成する方法

【課題】触媒を使用した銅CVD方法として、ピンチ−オフやボイドの発生なしにトレンチ、ビアホール及びコンタクトを充填して銅配線導電体を形成する方法を提供すること。

【解決手段】能動及び受動素子を配線連結するために、銅配線導電体を形成する方法が開示される。ここに開示された発明は、触媒と共に銅を配線導電体物質の原料とするCVD工程を含む。トレンチ、ビアホール、コンタクト、広い受動素子だけでなく電力素子と電力線のための大きいトレンチとホールを充填する配線方法がここに開示されて提供される。ここに提示された他の方法は、狭くて深いトレンチと小径で深いホールのような小さな陥没部を触媒を使用した銅CVDで充填する方法であり、湿式または乾式エッチバックまたは高温プラズマエッチバック工程により後続工程段階に備えて除去されるように扁平な最上部の表面に非常に薄い薄膜を形成する方法である。

(もっと読む)

層形成方法、層形成装置、基材処理装置、配線形成方法、および基板の配線構造

【課題】層形成に際して高真空および大きなチャンバを必要としない層形成方法および装置を提供する。

【解決手段】層形成装置は、0.01Paから常圧までの範囲における圧力下において固体または液体の有機金属材料を加熱し気化させることで該有機金属材料を含む原料ガスを生成する材料気化部108と、基材Wを保持する基材保持部100と、基材Wの表面を、材料気化部108により気化させた有機金属材料の分解温度よりも高い温度に加熱する基材加熱部104と、原料ガスからなる雰囲気を基材Wの表面上に局所的に形成する材料供給部109とを備える。材料供給部109は、基材の表面の少なくとも一部を原料ガス雰囲気に暴露させることで基材Wの表面に金属層または金属化合物層を形成する。

(もっと読む)

2,141 - 2,160 / 2,960

[ Back to top ]