Fターム[5F033NN07]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 介在層を有するもの (6,157) | バリア層を含むもの (2,805)

Fターム[5F033NN07]に分類される特許

1,721 - 1,740 / 2,805

半導体装置

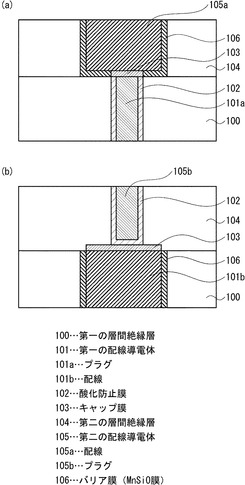

【課題】 銅と銅以外の異種材料を使用した配線とプラグ等の配線導電体間において、銅の拡散を効果的に防止することにより、信頼性を向上した半導体装置を提供することを目的とする。

【解決手段】 半導体基板上の第一の層間絶縁層100内に形成されたタングステンプラグ101aと、タングステンプラグ101a上に形成された導電性かつ薄膜のコバルト含有キャップ膜103と、第一の層間絶縁層100の上層層間絶縁層である第二の層間絶縁層104内において、タングステンプラグ101a上にキャップ膜103を介して形成された銅配線105aを備える。

(もっと読む)

金属配線構造用のルテニウム膜の形成方法

【課題】薄く且つ連続的なRu膜を形成する。

【解決手段】 反応室内で基板上にルテニウム(Ru)薄膜を堆積させる方法であって、(i)反応室内にルテニウム前駆体のガスを供給して、非環式ジエニルを含むルテニウム複合体であるルテニウム前駆体のガスを基板に吸着させる段階と、(ii)励起した還元ガスを反応室内に供給して、基板に吸着されたルテニウム前駆体を活性化させる段階と、(iii)段階(i)と(ii)を繰り返し、それにより基板上にルテニウム薄膜を形成する段階とを含む方法。

(もっと読む)

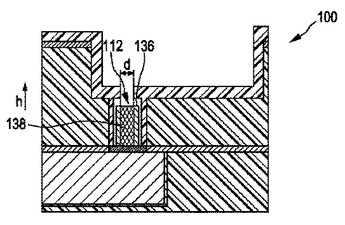

相互接続構造内におけるカーボンナノ構造成長の制御

基板上の相互接続構造が提供される。この相互接続構造は、基板レベルの上又は上方の少なくとも2つの相互接続レベルに導電性の相互接続素子を具える。本発明の相互接続構造では、少なくとも1つの導電性のビアが一つの相互接続レベルにおける第1の相互接続素子を異なる相互接続レベルにおける第2の相互接続素子に接続する。このビアは、第1の誘電体層のビア開口内を延びる導電性の円筒状カーボンナノ構造を含む導電性ビア材料を具える。少なくとも1つのカバー層部分がビア開口の横方向広がり内まで延在してビアアパーチャを規定し、このアパーチャはカーボンナノ構造がこのビアアパーチャを貫通するのを阻止するに十分なほど小さい。この構造によれば相互接続構造の製造中における高さ方向のカーボンナノ構造成長の制御が向上する。  (もっと読む)

(もっと読む)

低抵抗コンタクト構造体及びその製造方法

【課題】 半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供すること。

【解決手段】 本発明の実施形態は、半導体デバイスと後工程の相互接続体との間の誘電体材料層内にコンタクト構造体を製造する方法を提供する。この方法は、誘電体材料層内に少なくとも1つのコンタクト開口部を作成するステップと、化学気相堆積プロセスによって第1のTiN膜を形成するステップであって、第1のTiN膜はコンタクト開口部をライニングする(内側を覆う)ステップと、物理的気相堆積プロセスによって第2のTiN膜を形成するステップであって、第2のTiN膜は第1のTiN膜をライニングするステップとを含む。本発明の実施形態によって製造されるコンタクト構造体も提供される。

(もっと読む)

半導体装置

【課題】タンタルからなるバリアメタル膜がダメージを抑制もしくは低減された低比誘電率層間絶縁膜に接して設けられているとともに、Taバリアメタル膜およびこれに覆われた導電体の接続不良も抑制されている半導体装置を提供する。

【解決手段】半導体装置26は、比誘電率が3以下の低比誘電率層間絶縁膜8、バリアメタル膜21、導電体22を具備する。低比誘電率層間絶縁膜8には、開口部17,20が形成されている。バリアメタル膜21は、開口部17,20の内側を覆って設けられているとともに結晶構造が互いに異なるα−Taおよびβ−Taを含むタンタルの膜からなり、かつ、α−Taとβ−Taとの組成比が低比誘電率層間絶縁膜8に接する部分において1以上5以下となっている。導電体22は、開口部17,20に形成されたバリアメタル膜21上に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】最上層に銅の層を有するシールリングの酸化および腐食を防止しつつ、ダイシングの際の回路形成領域におけるクラック発生を防止する。

【解決手段】シリコン基板101上の層間絶縁膜109に、シールリング110の最上層となる銅の配線層114を形成し、その上面を覆うアルミ配線層141を形成する。そして層間絶縁膜109及びアルミ配線層141上にプラズマ窒化膜層121を形成し、ダイシング領域とシールリングとの間に、プラズマ窒化膜層121を貫通する開口部123を設ける。アルミ配線層141の幅は配線層114の幅よりも大きく形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ダマシン構造の多層配線およびCoWP等の導電性バリア膜を有する半導体装置において、従来よりも電気特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】下層配線12に至るビア孔17を開口する際、下層配線12表面に残存する導電性バリア膜13と下層配線12との間で形成される反応層14が除去される。よって、ビア17下面と下層配線12とが接合する界面において、導電性バリア膜13と下層配線12との間で形成される反応層14が存在しないため、ビア抵抗を十分に下げることができる。

(もっと読む)

半導体素子の製造装置及びこれを用いた半導体素子の製造方法

【課題】本発明は、半導体素子の製造装置及びこれを用いた半導体素子の製造方法を提供するためのものである。

【解決手段】半導体素子の製造装置は、基板を移送するトランスファーチャンバーと、トランスファーチャンバーに連結され、基板の上に珪化窒化チタニウム層を形成するための第1工程チャンバーと、トランスファーチャンバーに連結され、珪化窒化チタニウム層の上にタンタリウム層を形成するための第2工程チャンバーと、トランスファーチャンバーに連結され、タンタリウム層の上に銅シード層を形成するための第3工程チャンバーと、を含む。これによって、効率よく銅配線を形成することができる。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】繰り返し応力および衝撃力に対する耐性を向上し、より高い実装信頼性を備えることができる半導体装置を提供する。

【解決手段】電気信号を入出力するために半導体チップ101の表面上に設けられた導体部104と、導体部104を実装基板に接合するために、導体部104の表面上に形成された外部接続端子106とを備え、導体部104は、該導体部104の表面に、導体部104の表面の中央を貫通する貫通孔105が形成されており、外部接続端子106は貫通孔105に沿って形成されている。

(もっと読む)

半導体装置の製造方法

【課題】合金層(シード層)中の自己形成バリア膜の生成に寄与しない余剰なMnを除去することで、配線抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】まず、基板11上に設けられた層間絶縁膜15に配線溝16を形成する。次に、配線溝16の内壁を覆う状態で、CuMnからなる合金層17を形成する。次いで、合金層17が設けられた状態の基板11の表面に、Cuに対してMnを選択的に溶解する洗浄液を供給し、自己形成バリア膜の形成に寄与しない合金層17中のMnを、洗浄液に溶解させて選択的に除去する。続いて、熱処理を行い、合金層17中のMnを層間絶縁膜12、15の構成成分と反応させて、合金層17と層間絶縁膜12、15の界面に、Cuの拡散防止性を有するMn化合物からなる自己形成バリア膜を形成する。続いて、自己形成バリア膜が設けられた配線溝16にCuを主成分とする導電層を埋め込む。

(もっと読む)

バリア膜形成方法

【課題】バリア性に優れたバリア膜を提供する。

【解決手段】真空槽内に基板を搬入して(S1)、昇温させ(S2)、含窒素ガスと含高融点金属ガスのうち、一方のガスを導入し(S3)、該一方のガスを真空排気した後(S4)、他方のガスを導入し(S5)、該他方のガスを真空排気する(S6)。この工程を複数回繰り返して行うと(S9)、基板表面に吸着された一方のガスと、後から導入された他方のガスとの間でCVD反応が生じるので、コンタクトホール内にバリア膜がコンフォーマルに成長し、ステップカバレージのよいバリア膜を得ることができる。CVD反応を行う毎にパージガスを導入し(S7)、真空排気すると(S8)、基板や真空槽に吸着された副生成物ガスや未反応ガスがパージガスと交換されるので、より高純度なバリア膜を得ることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ領域にアルミニウムを露出させない。

【解決手段】下地10上にヒューズ領域13及び配線領域を設定し、下地のヒューズ領域上にヒューズ40を形成する。下地及びヒューズ上に第1絶縁膜を形成する。配線領域の第1絶縁膜に第1コンタクト用開口部を形成した後、導電材料で埋め込んで第1プラグを形成する。第1絶縁膜上に、第2絶縁膜を形成する。第2絶縁膜に、第1プラグを露出する第2コンタクト用開口部と、ヒューズ領域の第1絶縁膜を露出するストッパ用開口部を形成する。第2コンタクト用開口部を導電材料で埋め込んで第2プラグを形成するとともに、ストッパ用開口部を導電材料で埋め込んでストッパ膜55を形成する。第2プラグ及びストッパ膜を備える第2絶縁膜上に、導電膜パターン、層間絶縁膜を形成する。ヒューズ領域の層間絶縁膜をエッチングにより除去して、ストッパ膜を露出する。ストッパ膜をエッチングにより除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】冗長回路による救済率の向上及び半導体装置の不良の低下を同時に実現する半導体装置及び当該半導体装置の製造方法を提供する。

【解決手段】基板101上の絶縁膜106に形成されたメタル配線109及びフューズ配線111と、前記絶縁膜106の上方に形成された第1のPAD配線下絶縁膜202と、前記第1のPAD配線下絶縁膜202上に形成された第2のPAD配線下絶縁膜203と、前記第1のPAD配線下絶縁膜202及び第2のPAD配線下絶縁膜203の前記メタル配線109の上方の領域に形成されたPAD配線402と、前記第1のPAD配線下絶縁膜202及び前記第2のPAD配線下絶縁膜のうち当該第1のPAD配線下絶縁膜202の一部が前記フューズ配線111の上方の領域に残存するように形成された開口部701を備え、前記第2のPAD配線下絶縁膜203は前記第1のPAD配線下絶縁膜202に含まれる元素と異なる元素を含む。

(もっと読む)

成膜方法

【課題】 低温のプロセス温度によるタングステン膜の形成工程を用いることで、バリヤ層として十分な膜厚を得るために従来行われた熱CVDによるTiN膜の形成工程を省略することが可能な成膜方法を提供する。

【解決手段】 真空引き可能な処理容器内にて被処理体Wの表面に所定の膜を形成する方法において、前記被処理体の表面にチタン膜32を形成するチタン膜形成工程と、前記チタン膜の表面を窒化して窒化膜34を形成する窒化工程と、前記被処理体の表面に、還元ガスとタングステン含有ガスとを交互に間欠的に1回、或いは複数回繰り返し供給しつつ比較的低温でタングステン膜36を形成するタングステン膜形成工程と、を有する。これにより、バリヤ層として十分に機能するタングステン膜を形成する。

(もっと読む)

垂直型ウェハ間相互接続を設けるための金属充填貫通ビア構造体

【課題】 垂直型ウェハ間相互接続を設けるための金属充填貫通ビア構造体を提供する。

【解決手段】 垂直型ウェハ間相互接続構造体を設けるのに有用な貫通ビア接続を作成する方法、並びに、この方法によって形成される垂直型相互接続構造体が提供される。本発明の方法は、垂直型接続のために金属スタッドのみを使用し、それゆえに、金属スタッドによってアルファ線は発生されない。本発明の方法は挿入ステップ、加熱ステップ、薄層化ステップ及び裏面加工を含む。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、コンタクトホール底部表面に残留するハロゲン化物を確実に除去し、界面抵抗の上昇を抑制して接触抵抗の安定化および配線信頼性の向上化を得られる半導体装置の製造方法を提供する。

【解決手段】シリコン基板1上に層間絶縁膜3を形成する工程と、層間絶縁膜に対し有機物系マスクRを用いてハロゲンを含むエッチングガスによりドライエッチングし、層間絶縁膜の所定部位にコンタクトホールhを形成する工程と、前記有機物系マスク材を剥離除去する工程と、前記コンタクトホールを含む層間絶縁膜上に、OHまたはHを含むレジスト8を塗布したうえで酸素プラズマによりアッシングする工程と、前記コンタクトホール内に導電材を埋め込む工程とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】多孔質化された層間絶縁膜を用い、機械的強度の低下および上層または下層との密着性の低下が抑制された半導体装置およびその製造方法を提供する。

【解決手段】基板上に設けられ、ポロジェンAを分解除去してなる多孔質化された第1絶縁膜8と、第1絶縁膜8上に設けられた第2絶縁膜9と、第2絶縁膜9および第1絶縁膜8に下層の配線6に達する状態で設けられた導電層パターン15’とを有し、第1絶縁膜8は、ポロジェンAが残存した状態の非多孔質領域8Aを有することを特徴とする半導体装置およびその製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置に吸湿された水分により生成される腐食生成物による隣り合う再配線間の電気的なリークを抑制して半導体装置の耐湿寿命の向上を図る手段を提供する。

【解決手段】半導体基板と、半導体基板に形成された内部回路に電気的に接続する電極パッドと、電極パッドに達するスルーホールが形成された絶縁膜と、電極パッドに電気的に接続し、絶縁膜上に延在する再配線とを備えた半導体装置において、再配線の周囲の絶縁膜に、この再配線に隣接した凹溝を設ける。

(もっと読む)

半導体装置の製造方法

【課題】機械的強度が高く、かつ誘電率が低く安定した絶縁膜を有する半導体装置の製造方法を提供する。

【解決手段】シリコンに炭化水素基を結合させたSiOC系材料からなる多孔質の第1層間絶縁膜5を基板1上に成膜する工程と、第1層間絶縁膜5に電子線EBを照射することにより第1層間絶縁膜5の機械的強度を高める工程とを行う半導体装置の製造方法において、電子線EBを照射した後に、第1層間絶縁膜5を酸素雰囲気中においてアニール処理を行い、Si−H結合をSi−O−Si結合に置き換える。

(もっと読む)

半導体装置の製造方法およびプラズマ処理装置

【課題】絶縁膜に凹部を形成する際のエッチングレートの面内傾向を調整して、凹部の形状のばらつきを低減する。

【解決手段】半導体装置100の製造方法は、半導体ウェハ上に第1の層間絶縁膜108を形成し、第1の層間絶縁膜108上に第2のエッチング阻止膜110を形成し、第2のエッチング阻止膜110を貫通して複数の凹部を第1の層間絶縁膜108に選択的に形成する工程を含む。ここで、第2のエッチング阻止膜110は、半導体ウェハの位置に応じて厚さが異なるように形成される。

(もっと読む)

1,721 - 1,740 / 2,805

[ Back to top ]