Fターム[5F033PP06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065)

Fターム[5F033PP06]の下位に属するFターム

選択CVD (170)

LPCVD(減圧CVD) (135)

光CVD (23)

MOCVD(有機金属CVD) (177)

プラズマCVD (289)

Fターム[5F033PP06]に分類される特許

61 - 80 / 2,271

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

半導体装置およびその製造方法

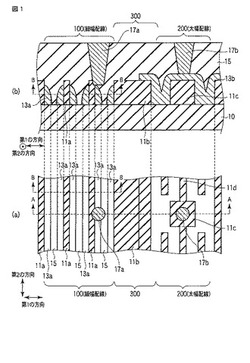

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

相互接続構造体及びその形成方法

【課題】 相互接続ラインを形成するための新規な方法を提供する。

【解決手段】 細線相互接続部(60)は基体(10)の表面内又はその上に形成された半導体回路(42)の上に位置する第1の誘電体層(12)内に設けられる。パシベーション層(18)は誘電体層の上に付着され、第2の厚い誘電体層(20)はパシベーション層の表面上に形成される。厚くて幅広い相互接続ラインは第2の厚い誘電体層内に形成される。第1の誘電体層はまた、基体の表面上に付着されたパシベーション層の表面上に幅広くて厚い相互接続ネットワークを形成するように、省略することができる。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

半導体装置

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

金属付着物の除去方法、基板処理装置、および記録媒体

【課題】有機化合物ガスによる基板処理を清浄に行うことが可能となる金属付着物の除去方法および基板処理装置を提供する。

【解決手段】金属付着物の除去方法は、金属層が形成された被処理基板を処理する処理空間を内部に有する処理容器の内部に付着した金属付着物を昇華させるように、前記処理容器内部の温度と、前記処理空間の圧力とを、制御する。

(もっと読む)

タングステン膜の成膜方法

【課題】工程が煩雑になることなく、埋め込み部分のボイドやシームを解消することができるタングステン膜の成膜方法を提供すること。

【解決手段】処理容器内において、ホールを有する基板にCVDによりタングステン膜を成膜してホール内にタングステンの埋め込み部を形成する工程と、同じ処理容器内にエッチングガスとしてClF3ガスまたはF2ガスを供給して埋め込み部の上部をエッチングし、開口を形成する工程と、開口が形成された埋め込み部を有する基板に対して同じ処理容器内において、CVDによりタングステン膜を成膜する工程とを有する。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

成膜装置及び成膜方法

【課題】 タングステン膜を成膜する際に半導体ウェーハがエッチングされることを抑制する成膜装置及び成膜方法を提供することである。

【解決手段】 実施形態に係る成膜装置は、半導体ウェーハを載置するためのステージと、前記ステージ上に載置される半導体ウェーハの周縁部を覆うように配置されるエッジカット部を備え、前記半導体ウェーハ上にタングステン膜を成膜する。前記エッジカット部は、前記半導体ウェーハの周縁部と接触可能に設けられた第1のエッジカット部と、前記第1のエッジカット部に接続され、前記半導体ウェーハと実質的に垂直な方向に上下動可能な接続部と、前記接続部に接続され、前記接続部の上下動により前記半導体ウェーハの内側面に当接するように配置された第2のエッジカット部と、を備える。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

61 - 80 / 2,271

[ Back to top ]