Fターム[5F033PP06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065)

Fターム[5F033PP06]の下位に属するFターム

選択CVD (170)

LPCVD(減圧CVD) (135)

光CVD (23)

MOCVD(有機金属CVD) (177)

プラズマCVD (289)

Fターム[5F033PP06]に分類される特許

81 - 100 / 2,271

半導体装置及びその製造方法

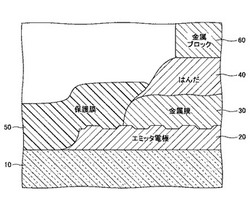

【課題】本発明は、保護膜の境界面での膜厚を厚くし、はんだが金属膜の下方に侵入し難い半導体装置を提供することを目的とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

金属エッチング用組成物、および金属エッチング用組成物を用いた半導体装置の製造方法

【課題】基板に含まれる珪素系材料に対してダメージを与えることなく、常温で高速に長時間安定してタングステン系金属を除去することができるエッチング用組成物を提供する。

【解決手段】本発明の金属エッチング用組成物は、過硫酸塩の添加量が8〜30質量%、塩基性化合物の添加量が1〜15質量%、となるように配合された、フッ素含有化合物を含まない25℃でのpHが8以上の水溶液であることを特徴とする。過酸化水素をさらに添加することによりタングステン系金属とチタン系金属の積層膜あるいは合金膜の除去に適用することができる。他方、過酸化水素を無添加とすることにより、チタン系金属に優先してタングステン系金属を選択的に除去することができる。

(もっと読む)

半導体装置の製造方法

【課題】高温化下でも安定な高信頼性を有する配線を容易に精度良く形成する方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上方に窒化チタンからなる第1の絶縁層を形成し、第1の絶縁層に複数の溝を形成し、溝の底面及び側壁下部を覆う部分が溝の側壁上部を覆う部分よりも厚くなるように、溝の底面及び側壁を覆うバリアメタルを形成し、溝のバリアメタル上に金属膜を埋め込み、複数の配線を形成し、第1の絶縁層を除去して、隣り合う複数の配線の間に配線に接するような空隙を形成し、複数の配線の上面に、金属又は酸化物からなるキャップ膜を形成し、複数の配線の上面及び側壁を覆うようにシリコンナイトライドカーバイド膜又は窒化ボロン膜からなる拡散防止膜を形成し、複数の配線の上面を覆い、且つ、複数の配線間に空隙が形成されるように、第2の絶縁層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体装置の製造方法

【課題】 厚い絶縁樹脂層のウェハレベルCSPで、第1電極(チップパッド)と外部電極(バンプ)との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】 次の各工程を含む半導体装置の製造方法、(1)絶縁樹脂層を半導体ウェハの上に形成し、(2)開口径が(D1)となるよう絶縁樹脂層の一部を除去し半導体ウェハ上の第1電極を露出し、(3)フィルム状レジストを半導体ウェハの全面に、第1電極とレジストとの間が中空構造となるよう貼付け、(4)レジストをパターニングし、再配線層を絶縁樹脂層の上に形成し、レジストパターンを除去し、めっきした部分以外のシード層を除去し、(5)再配線層の上に再配線保護層を形成し、(6)再配線保護層の開口径(D2)が、D2>D1となるように再配線保護層の一部を除去して第1電極と、第2電極を露出し、(7)第1電極及び第2電極の上にめっき層を形成し、(8)めっき層を溶融して外部電極を形成する。

(もっと読む)

強誘電体キャパシタ

【課題】還元性雰囲気による特性劣化を抑制することができる構造の強誘電体キャパシタを提供する。

【解決手段】強誘電体キャパシタ積層構造8は、強誘電体膜3と、強誘電体膜の一方表面に接する下部電極2と、強誘電体膜3の他方表面に接する上部電極4とを含む。上部電極4および下部電極2のうちのうちの少なくともいずれか一方が、酸化物導電体層と金属層とを交互に積層した積層電極構造を有している。この積層電極構造は、酸化物導電体層および金属層のうちの少なくともいずれか一方を2層以上含む。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】配線レイアウトや配線構造の複雑化や大幅な変更を伴うことなく、積層配線間に生じるクロストークノイズを低減する。

【解決手段】配線103上に絶縁膜104及び106を挟んで配線108が形成されている。配線103と配線108とは平面視において少なくとも部分的にオーバーラップしている。少なくとも配線103と配線108とのオーバーラップ部分の前記絶縁膜中に導電性シールド層105が形成されている。

(もっと読む)

半導体基板内の埋込ボイドを検出するための方法

【課題】半導体基板内又は基板上に形成された構造内の埋込ボイドを検出するための方法を提供する。

【解決手段】構造を形成するための少なくとも1つの処理ステップを実施する工程と、基板の質量M1を測定する工程と、熱処理を実施する工程と、基板の質量M2を測定する工程と、前記実施した熱処理の前後で測定した基板の質量の差を計算する工程と、前記質量の差を所定値と比較することにより、前記構造内の埋込ボイドの存在を推測する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

貫通電極を備えた配線基板とその製造方法

【課題】深孔相互間の距離を狭くする事ができ、深孔を微細化しても周囲の配線基板から及ぼされる応力の増加が防止でき、信頼性が保たれ、プロセス全体を低コストできる配線基板とその製造方法を提供する。

【解決手段】基体の主表面からその反対側裏面の両面に貫通する複数の貫通孔を備え、それらの孔が実質的に金属で埋められて貫通電極とされており、それらの内の少なくとも2以上の電極が電気的に並列に接続されている配線基板の製造方法であって、それらの2以上の孔を形成する場合に、それらの2以上の孔を含む領域より大きいサイズのマスクパターンを利用してそれらの2以上の孔を陽極酸化法を含む自己組織的穴明けプロセスにより所定の深さ以上の孔を形成した後に裏面から基体を削って、孔を裏面に露出させて貫通孔とする事を特徴とする配線基板の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

81 - 100 / 2,271

[ Back to top ]