Fターム[5F033PP06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065)

Fターム[5F033PP06]の下位に属するFターム

選択CVD (170)

LPCVD(減圧CVD) (135)

光CVD (23)

MOCVD(有機金属CVD) (177)

プラズマCVD (289)

Fターム[5F033PP06]に分類される特許

121 - 140 / 2,271

半導体集積回路装置及びその製造方法

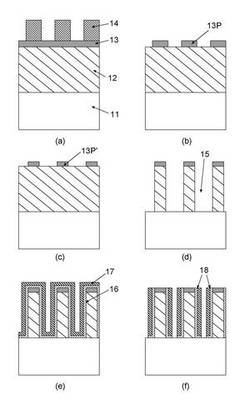

【課題】配線幅若しくは配線間隔の縮小に伴い、加工限界の制約を受けるために微細な配線形成が困難になりつつある。

【解決手段】絶縁層(第1の絶縁層12及び第2の絶縁層13)に溝15を形成し、導体膜(バリア膜16及び金属膜17)を溝15を埋設しない膜厚で形成し、続いて導体膜をエッチバックすることで溝15の側壁にサイドウォール状の配線18を形成することで、配線幅は導体膜の膜厚で制御できるために加工限界の制約を受けず、配線抵抗は配線高さを高くすることにより所定の配線抵抗を維持することができる。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグ形成時に位置ずれが発生しても水分や不純物が溜まる窪みが発生することがなく、微細化しても長期間にわたる信頼性を確保できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1の絶縁膜121の上に形成された強誘電体キャパシタ131と、強誘電体キャパシタ131を覆う第2の絶縁膜311及びエッチングストッパ膜312と、エッチングストッパ膜312の上面からトランジスタTの不純物領域に到達する第1のコンタクトホール内に導電体材料を充填して形成された第1のプラグ313と、エッチングストッパ膜の上に形成された第3の絶縁膜314と、第3の絶縁膜314の上面から第1のプラグに到達する第2のコンタクトホール内に導電体材料を充填して形成された第2のプラグ315とを有する。

(もっと読む)

Cu配線の形成方法および成膜システム

【課題】Cuめっきを用いることなくPVDのみでトレンチまたはホールCuを埋め込んでCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202の全面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上にPVDによりCuがマイグレーションする条件でトレンチ203内に第1のCu膜206を形成する工程と、第1のCu膜206の上に、第1のCu膜206よりも大きな成膜速度でPVDにより第2のCu膜207を形成する工程と、CMPにより全面を研磨する工程とを有する。

(もっと読む)

Cu膜の形成方法

【課題】バリアメタル膜とCu膜との密着性を向上する。

【解決手段】基板上に、スパッタ法によりバリアメタル膜としてTi膜又はTa膜を形成し、このバリアメタル膜上にスパッタ法により窒化物膜を形成し、この窒化物膜の上にCVD法によりCu膜を形成した後、100〜400℃でアニール処理を行う。このようにCu膜を形成することにより、バリアメタル膜とCu膜との密着性が向上する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】デュアルダマシン法を用いて層間絶縁膜内にCu配線を形成する際、硬度が低い層間絶縁膜および硬度が高い層間絶縁膜のそれぞれに形成されたビアホール内に配線材料を良好に埋め込むことができるようにする。

【解決手段】第2層間絶縁膜17には、配線溝30aとビアホール28aとが形成されている。また、ビアホール28aの開口部には、第2層間絶縁膜17を斜め下方に後退(リセス)させることによって、テーパ状の断面形状を有するリセス部31が形成されている。これにより、ビアホール28aの開口部の直径は、開口部よりも下方の領域の直径に比べて大きくなり、ビアホール28aの直径が微細な場合であっても、ビアホール28aの内部に配線材料を良好に埋め込むことができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

成膜方法およびCu配線の形成方法

【課題】被処理基板を加熱してトレンチやホールの間口部のオーバーハングを抑制しつつ金属膜を成膜するとともに、成膜後に速やかに被処理基板の温度を低下させることができる成膜方法を提供すること。

【解決手段】載置台を低温に保持して、載置台上に被処理基板を吸着させずに載置する工程と、プラズマ生成ガスのプラズマを生成し、載置台に高周波バイアスを印加した状態で、被処理基板にプラズマ生成ガスのイオンを引きこんで被処理基板を予備加熱する工程と、ターゲットに電圧を印加して金属粒子を放出させ、プラズマ生成ガスのイオンとともにイオン化した金属イオンを被処理基板に引きこんで金属膜を形成する工程と、被処理基板を低温に保持された載置台に吸着させ、載置台と被処理基板との間に伝熱ガスを供給して被処理基板を冷却する工程とを有する。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】樹脂基板上に設けたボトムゲート型薄膜トランジスタにおいて、製造プロセスを簡略化することにより、高品質で低コストの薄膜トランジスタとその製造方法及び画像表示装置を提供することを目的とする。

【解決手段】ボトムゲート型の薄膜トランジスタは、樹脂基板と、樹脂基板の同一面上に設けられたゲート電極と絶縁性密着層と、ゲート電極と絶縁性密着層との上に設けられたゲート絶縁層とを、少なくとも備える。また、ゲート電極は、金属を含む。また、絶縁性密着層は、ゲート電極に含まれる金属のオキシ水酸化物を含むことを特徴とする。また、金属は、Alを含む金属であり、ゲート電極の膜厚は、10nm以上100nm以下である。

(もっと読む)

自己整合シリサイドの形成方法、半導体デバイスの製造方法、および半導体構造物

【課題】製造工程の増大を抑制し、コンタクト抵抗および界面抵抗の増大を防止する。

【解決手段】実施形態において、シリコン層は、ゲートラストスキームを用いた機能的ゲート電極の製造後に、形成される。初期的な半導体構造物は、半導体基板上に形成された少なくとも一つの不純物領域、不純物領域の上に形成された犠牲膜、犠牲膜の上に形成された絶縁層、絶縁層の上に形成された絶縁層を備える。ビアは、初期の半導体構造物の絶縁層へ、および、コンタクト開口部が絶縁層に形成されるように絶縁層の厚さを通り抜けて、パターン化される。次に、絶縁層の下にある犠牲膜は、絶縁層の下に空隙を残して除去される。次に、金属シリサイド前駆体は、空隙スペースに配置され、金属シリサイド前駆体は、アニールプロセスを通じてシリサイド層に変換される。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトと素子領域間にかかる電界を緩和し絶縁破壊を防ぐ。

【解決手段】実施形態の半導体装置は、基板上第1方向に延伸し並列し高さが同じ第1〜4分離、第1、2分離間の低い第1領域、高さが等しい第2、3分離間の第2領域、第3、4分離間の第3領域、第1領域上面、第1分離の第2分離に対向した側面および上面の一部、第2分離の第1分離に対向した側面および上面の一部に接する第1電極15−1、その第2方向で第3領域上面、第3分離の第4分離に対向した側面および上面の一部、第4分離の第3分離に対向した側面および上面の一部に接する第2電極15−2を有す。半導体装置は、第1電極の第2方向とは異なる方向に位置し第2領域上面、第2分離の第3分離に対向した側面および上面の一部、第3分離の第2分離に対向した側面および上面の一部に接する第3電極を有す。

(もっと読む)

半導体装置及びその製造方法

【課題】微細なパターンを含む半導体装置の信頼性を向上する。

【解決手段】本実施形態の半導体装置は、素子形成領域100内の半導体素子と、素子形成領域100内から引き出し領域150内に延在する複数の配線WLと、引き出し領域150内の配線WLに接続されるコンタクト部39と、を具備し、配線WLは、n番(nは1以上の整数)の側壁膜のパターンに対応する(n+1)番目の側壁膜のパターンに基づいて形成され、配線WLの配線幅WW又は素子形成領域150内の配線間隔WDに対応する第1の寸法は、リソグラフィの解像度の限界寸法より小さく、露光波長がλ、レンズの開口数がNA、プロセスパラメータがk1で示される場合、第1の寸法は、(k1/2n)×(λ/NA)以下であり、引き出し領域内で互いに隣接する配線WLの間隔WC2に対応する第2の寸法は第1の寸法より大きい。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上する。

【解決手段】一つの実施形態によれば、半導体装置は、電極、メッキ膜、半田、及びコネクタが設けられる。電極は、半導体チップ表面に設けられた第一の電極部と、第一の電極部上に設けられた絶縁膜の開口部を覆うように設けられ、第一の電極部に接続された突起状の第二の電極部とから構成される。メッキ膜は、第二の電極部上に設けられる。半田は、絶縁膜及びメッキ膜上に設けられる。コネクタは、一端の第一の構成部が半田上に設けられ、他端の第二の構造部が端子に接続され、電極と電極端子の間を接続する。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】結晶欠陥が可及的に少なく、従来よりも抵抗率の低い高質のグラフェンを備えた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板の上方に設けられた配線とを具備する。前記助触媒層のうち前記触媒層と接触している部分は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向しているか、または、前記助触媒層のうち前記触媒層と接触している部分は、アモルファス構造もしくは微結晶構造を有する。前記触媒層は、面心立方構造もしくは六方最密構造を有し、かつ、前記面心立方構造の(111)面もしくは前記六方最密構造の(002)面が前記半導体基板の表面と平行になるように配向する。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

素子付き基板、赤外線センサー、および貫通電極形成方法

【課題】マイグレーションの問題を生じることなく、微細でアスペクトの高く絶縁特性に優れた絶縁膜を備えた貫通電極を有する素子付き基板、赤外線センサーおよび貫通電極形成方法を提供する。

【解決手段】予め、素子回路形成前のベース基板にビアホールを形成し、前記ベース基板の素子回路形成面と前記ビアホールの内面に熱酸化により絶縁膜を形成する熱酸化を行なう。前記熱酸化工程後に前記ビアホール形成部に導電部を有する素子回路を形成した後、前記素子回路形成工程後に前記ビアホールに導電体を埋め込み形成するようにしている。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

121 - 140 / 2,271

[ Back to top ]