Fターム[5F033PP06]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | CVD(化学的気相成長法) (3,065)

Fターム[5F033PP06]の下位に属するFターム

選択CVD (170)

LPCVD(減圧CVD) (135)

光CVD (23)

MOCVD(有機金属CVD) (177)

プラズマCVD (289)

Fターム[5F033PP06]に分類される特許

161 - 180 / 2,271

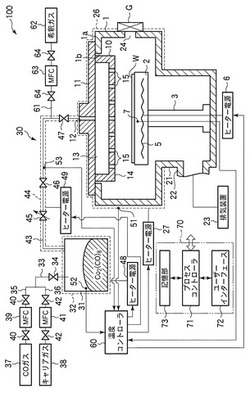

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

Cu配線の形成方法およびCu膜の成膜方法、ならびに成膜システム

【課題】微細なトレンチまたはホール等の凹部にボイドを発生させずに確実にCuを埋め込むことができ、かつ低抵抗のCu配線を形成すること。

【解決手段】ウエハWに形成されたトレンチ203を有する層間絶縁膜202において、トレンチ203の表面にバリア膜204を形成する工程と、バリア膜204の上にRu膜205を形成する工程と、Ru膜205の上に、加熱しつつ、PVDによりCuがマイグレーションするようにCu膜206を形成してトレンチ203を埋める工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

銅の光子誘起除去

【課題】基板から銅含有層の少なくとも一部を除去する方法を提供する。

【解決手段】第1反応チャンバ中で、銅含有表面層4の少なくとも一部を、ハロゲン化銅表面層5に変える工程と、第2反応チャンバ中で、光子含有雰囲気6に晒して、ハロゲン化銅表面層5の少なくとも一部を除去して、揮発性のハロゲン化銅生成物8の形成を始める工程とを含む。光子含有雰囲気6に晒す間に、この方法は、更に、第2反応チャンバから揮発性のハロゲン化銅生成物8を除去し、第2反応チャンバ中で揮発性のハロゲン化銅生成物8の飽和を避ける工程を含む。本発明の具体例にかかる方法は、銅含有層のパターニングに用いられる。例えば、本発明の具体例にかかる方法は、半導体デバイス中に銅含有相互接続構造を形成するのに使用される。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

金属層の結晶粒径及び粒径分布評価方法並びにそれを用いた半導体集積回路装置の製造方法

【課題】非破壊かつオンラインで金属層の結晶粒径及び粒径分布を評価する方法を実現する。

【解決手段】結晶組織を有し特定の面方位においてX線に対して回折ピークを持つ金属層にX線を照射して得られる回折ピークを入手するステップA、回折ピークに基づいて面積平均コラム長及び体積平均コラム長を求めるステップB、面積平均コラム長及び体積平均コラム長から結晶粒径の対数正規分布を求めるステップCを具備する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

導電性素子およびその製造方法、配線素子、情報入力装置、表示装置、ならびに電子機器

【課題】精細かつ高スループットの導電性素子を提供する。

【解決手段】導電性素子は、第1の波面と第2の波面とを有する基体と、第1の波面上に形成された、2層以上の層が積層された積層膜とを備える。積層膜が、導電パターン部を形成する。第1の波面および第2の波面が、0≦(Am1/λm1)<(Am2/λm2)≦1.8(但し、Am1:第1の波面の振動の平均幅、Am2:第2の波面の振動の平均幅、λm1:第1の波面の平均波長、λm2:第2の波面の平均波長)の関係を満たす。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能と信頼性を向上させる。

【解決手段】nチャネル型MISFETQn1,Qn2を覆うように半導体基板1上に引張応力膜としての窒化シリコン膜5を形成する。窒化シリコン膜5は窒化シリコン膜5a,5b,5cの積層膜である。窒化シリコン膜5a,5bの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分よりも小さく、窒化シリコン膜5a,5bは、成膜後に紫外線照射処理を行って引張応力を増大させる。窒化シリコン膜5a,5b,5cの膜厚の合計は、サイドウォールスペーサSW1とサイドウォールスペーサSW2との間の間隔の半分以上であり、窒化シリコン膜5cに対しては紫外線照射処理を行わない。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】論理回路の動作特性に優れた半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、多層配線層と、第1能動素子3a、容量素子19および周辺回路を有する記憶回路200と、第2能動素子3bを有する論理回路100と、記憶回路領域200に形成されており、能動素子3aと容量素子19とを電気的に接続する容量コンタクト13cと、論理回路領域100に形成されており、能動素子3bと第1配線8aとを電気的に接続する接続コンタクト13aと、を備え、第1配線8aは、容量素子19が埋め込まれた配線層のうち最下層の配線層の層間絶縁膜7aに位置しており、接続コンタクト13aは、容量コンタクト13cと同一層に設けられており、第1配線8aと接続コンタクト13aは、デュアルダマシン構造を有している。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

材料を付着させる方法

【課題】改良された付着プロセスを提供すること。

【解決手段】ビームを使用して、自発的反応の開始をサポートする条件を提供するように準備された表面の領域における前駆体ガスの自発的付着によって、材料を、所望のパターンに付着させる。いったん反応が開始されると、ビームが存在しなくなっても、反応が開始された表面の領域において反応は継続する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の品質及び製造歩留まりを向上させる。

【解決手段】半導体装置の製造方法は、SOQウェハ等の貼り合せウェハに複数の半導体チップ部を形成する工程と、絶縁膜を含む下部層(611,621)とメタル配線(メタル層)を含む上部層(612,622)とを有する配線層(61,62)を形成するプロセスを複数回行うことによって、複数の半導体チップ部上に多層配線構造(6)を形成する工程とを有し、ダミーチップ部上に複数重ねられた配線層(61,62)は、製品チップ部上における配線層と同じ形状(パターン)を持つ第1の配線層(61又は62)と、第1の配線層と異なる形状を持つ第2の配線層(62又は61)とを含み、ダミーチップ部上に複数重ねられた配線層のいずれかにおける下部層(611又は621)は、貫通メタル配線を持たない絶縁膜である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を製造する。また、スループットを向上させ、製造コストを低減する。

【解決手段】開口部OA1および絶縁膜(21、23)上に銅のCuシード層27を形成する工程と、Cuシード層上に、フォトレジスト膜を形成する工程と、Cuシード層上に、メッキ成長により銅膜31aを形成する工程と、銅膜上に、Ni膜31bを形成する工程と、により、再配線31を形成する。この後、再配線31上の開口部(OA2、パッド領域)にAu膜33bを形成した後、フォトレジスト膜を除去し、Ni膜31bに不動態化処理を施す。この後、再配線31の形成領域以外のCuシード層27をエッチングする。かかる工程によれば、Ni膜31bの表面に不動態化膜35が形成され、上記エッチングによるNi膜31bの膜減りを低減できる。また、膜減りを考慮したNi膜の厚膜化による基板の歪みによる不具合を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

161 - 180 / 2,271

[ Back to top ]