Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

281 - 300 / 898

超低静電容量配線のためのエアギャップを備える半導体装置の製造

【課題】本発明は、固体構造、特に半導体構造内部に一つ乃至複数のエアギャップを形成して金属線の如き電気部品間の誘電的カップリングを減じる方法に関する。そのような方法によって、集積回路やパッケージの如き半導体構造内の誘電的カップリングを減じようとした前述の従来の試みに関連する一つ乃至複数の欠点を克服することができる。

【解決手段】本発明の一つの局面によれば、半導体構造内にエアギャップを形成する方法は、(i)半導体構造内の閉鎖された内部空間を占めるための犠牲材料としてノルボルネン型ポリマーを利用し、(ii)該犠牲材料を一つ以上のガス状分解物へと分解(好ましくは熱処理によって自己分解)し、(iii)該内部空間に隣接する固体層の少なくとも一つを通じて上記ガス状分解物の少なくとも一つを排除する、工程からなる。

(もっと読む)

配線構造及び表示装置

【課題】 接続不良の発生や配線層へのダメージの付与を防止することができ、歩留まり良く信頼性の高い接続状態を実現することが可能な配線構造及び表示装置を提供する。

【解決手段】 基板上に形成された配線の幅広部分(配線部22)において、配線上に形成された絶縁膜23に設けられたコンタクトホールを介して外部接続用の接続パッド(例えばOLBパッド4)との電気的接続が図られてなる配線構造である。配線を覆う絶縁膜23が塗布方式により形成された絶縁膜23であり、幅広の配線部22においては、周辺領域にのみコンタクトホール26が形成されている。あるいは、幅広の配線部22の周辺領域に形成されたコンタクトホール26の開口寸法が、内部領域に形成されたコンタクトホール28,29の開口寸法よりも小となるように形成してもよい。

(もっと読む)

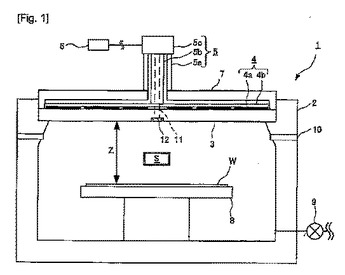

シリコン酸化膜の成膜方法、シリコン酸化膜、半導体装置および半導体装置の製造方法

プラズマ処理装置1のチャンバ2内に、シリコン化合物ガス、酸化性ガス、および希ガスを供給する。マイクロ波をチャンバ2内に供給し、マイクロ波により生成されたプラズマで、被処理基板上にシリコン酸化膜を形成する。希ガスの分圧比は、シリコン化合物ガスと酸化性ガスと希ガスを併せたトータルガス圧の10%以上の割合であって、シリコン化合物ガスと酸化性ガスの有効流量比(酸化性ガス/シリコン化合物ガス)は、3以上11以下とする。  (もっと読む)

(もっと読む)

金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFT

【課題】生産性が向上し、かつ寸法精度が良い金属配線の製造方法、TFTの製造方法、及びそれを用いて製造されたTFTを提供すること。

【解決手段】本発明にかかる金属配線の製造方法では、まず、主成分金属に、主成分金属より酸化物の生成エネルギーが低い添加金属が添加された第2の金属膜30を成膜する。そして、第2の金属膜30を酸化させて金属酸化物を形成し、第2の金属膜30の表面に酸化層32を形成する。次に、酸化層32上にフォトレジスト31を形成して、第1のドライエッチング条件により、酸化層32をエッチングする。そして、第1のドライエッチング条件の場合と比較して、主成分金属の金属酸化物に対する選択比が高い第2のドライエッチング条件により、下層の第2の金属膜30をエッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置表面に堆積された犠牲層を短時間に除去することができ、製造歩留りの向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート電極1、ドレイン電極2およびソース電極3を有する電界効果トランジスタ4と、ゲート電極1、ドレイン電極2およびソース電極3を被覆し、半導体基板4A上に設けられた中空保護膜5とを備え、中空保護膜5は、第1のキャップ層7と、第1のキャップ層7上に配置された第2のキャップ層10と、ドレイン電極2およびソース電極3の上方の第1のキャップ層7の位置に形成された複数の開口部12と、開口部12を第2のキャップ層10により封止する封止部12Aとを有し、開口部12を介して酸素プラズマを供給して犠牲層6をアッシング除去する半導体装置およびその製造方法。

(もっと読む)

ドライエッチング処理装置及びドライエッチング方法

【課題】エッチング溝の幅を一様に形成することができるドライエッチング処理装置及びドライエッチング方法を提供する。

【解決手段】バイアス用高周波電源52は、処理容器10内に導入されたエッチングガス(例えば、HBr)をマイクロ波導入装置200で励起して発生させたプラズマ中のイオン及び活性種を半導体ウェハWの方向へ加速させるためのバイアス電圧(例えば、200V以下)を半導体ウェハWに印加する。バイアス電圧の絶対値を200V以下にすることにより、シリコン基板に到達するプラズマ中のイオン(例えば、Br+ )のエネルギーを小さくし、Si−Siの共有結合が切断されて活性粒子(例えば、SiBr3 、SiBr2 、SiBr等)が生成されることを抑制する。

(もっと読む)

酸化層の形成方法

本発明は、半導体基板(1)上に酸化層(9)を形成する方法を提供する。この方法は、例えば3次元構造を含む、少なくとも1つの孔(5)を含むような半導体基板(1)を得る工程と、酸性の電解質溶液中で基板を陽極酸化することにより、例えば3次元構造を含む半導体基板(1)上に酸化層(9)を形成する工程と、を含む。  (もっと読む)

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】コンタクトおよび配線形成時の合わせマージンがゼロであり、集積度を大幅に向上し、パターンレイアウトの自由度の拡大を可能とする薄膜半導体素子及びその製造方法を提供する。

【解決手段】透明絶縁性基板10上に形成され、第1導電型の不純物を含むソース領域及びドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極18、前記ソース領域又はドレイン領域の表面に形成された高融点金属と半導体との化合物からなる層、前記島状半導体層及びゲート電極を覆う層間絶縁膜29、及び前記ソース領域又はドレイン領域に接続された局所配線28を具備し、前記局所配線28は、前記ソース領域又はドレイン領域の表面に形成された前記化合物層と高融点金属層との2層構造、及び前記ソース領域又はドレイン領域の外側に形成された前記高融点金属層の延長からなることを特徴とする。

(もっと読む)

基板構造及びその形成方法

【課題】薄膜特性及び接着性が改善が可能な基板構造形成方法及びこれを用いて形成された基板構造を提供する

【解決手段】基板構造を形成する方法は、基板10をエッチングして垂直面51を有するエッチング部50を形成する段階と、基板10の全面上にまたは基板10に部分的に拡散物質層60を形成する段階と、拡散物質層60を熱処理して、一部が上記エッチング部50の表面の下へと拡散したシード層60’を形成する段階、及びシード層60’上に金属層70を形成する段階とを含む。上記方法によれば、シード層60’によって基板10のエッチング部50の表面特性が改善されることもあるので、エッチング部50の垂直面51に接着性に優れ且つ均一な厚さの金属層70を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置の製造方法および半導体装置を提供すること。

【解決手段】シリコン基板1上に第1アモルファスカーボン膜24を形成する工程と、第1アモルファスカーボン膜24上にBPSG膜13を形成する工程と、BPSG膜13上に第2アモルファスカーボン膜16を形成する工程と、第2アモルファスカーボン膜16をパターニングし、第2アモルファスカーボン膜16をハードマスクとしてBPSG膜13を第1アモルファスカーボン膜24が露出するまでエッチングする工程と、露出した第1アモルファスカーボン膜24および第2アモルファスカーボン膜16をアッシングする工程とを備える。第1アモルファスカーボン膜24がエッチングストッパ層として作用する。よってシリコン基板1がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

パッドと半導体装置の製造方法

【課題】パッドと半導体装置の製造方法において、パッドの配置密度を向上させると共に、電気的試験で使用されるプローブによってパシベーション膜が欠損するのを防止する手段の提供。

【解決手段】開口面以外がパシベーション膜40、41で覆われたパッド37bにおいて、半導体装置に設けられた三角形状又は台形状の第1の金属膜37xと、第1の金属膜37x上であって、パッド37bの開口面の一部分に開口41aの側面と接するように形成された第2の金属膜37yとを備えたパッドとする。

(もっと読む)

基板へのビアの形成方法

【課題】基板の反りを低減できる基板へのビアの形成方法を提供する。

【解決手段】貫通孔形成工程の後で基板20aの一表面側に各貫通孔22が閉塞されないように金属薄膜26を形成した後、基板20aの上記一表面側に各貫通孔22および各貫通孔22の周部の金属薄膜26を露出させる複数の開口部61aを有するレジスト層61を形成してから、基板20aの上記一表面側に各貫通孔22を閉塞する複数の島状の導体部27を電気めっきにより形成し、その後で基板20aの上記他表面側に対向配置した上記陽極と基板20aの上記一表面側において各貫通孔22を閉塞している導体部27からなる陰極との間に通電してそれぞれビア24となる複数の金属部を各導体部27における貫通孔22側の露出表面から基板20aの厚み方向に沿って析出させ、その後、レジスト層61および当該レジスト層61下の金属薄膜26を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】アナログデバイスを有する半導体装置のホール形成工程において、プラズマダメージに弱いアナログトランジスタのゲート絶縁膜に加えられるプラズマダメージを抑制できる半導体装置を提供する。

【解決手段】 本発明に係る半導体装置は、アナログ部及びデジタル部それぞれにトランジスタを有し、シリコン基板上に形成された前記アナログ部及び前記デジタル部それぞれのゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極上に形成された層間絶縁膜と、前記層間絶縁膜に形成された前記アナログ部のゲート電極上に位置するコンタクトホール9と、前記層間絶縁膜に形成された前記デジタル部のゲート電極上に位置するコンタクトホール9aと、を具備し、コンタクトホール9の径をコンタクトホール9aの径より小さくすることを特徴とする。

(もっと読む)

パターン形成方法

【課題】疎密に配置された複数のパターンを正確に形成できるパターン形成方法を提供する。

【解決手段】基板14上に第1絶縁膜15を形成し、第1絶縁膜15上に疎密に配置された第1開口パターン31a〜31dを有する第1マスク材31を形成し、第1マスク材31を用いて第1絶縁膜15をエッチングして第1開口パターン31a〜31dを転写する工程と、第1マスク材31を除去し、第1開口パターン15a〜15dの上面を塞いで第1絶縁膜15上に、第1絶縁膜15と異なる材質の第2絶縁膜32を形成する工程と、第2絶縁膜32上に、第1開口パターン15a〜15dと対向する第2開口パターン36a〜36dを有する第2マスク材36を形成し、第2マスク材36を用いて第2絶縁膜32をエッチングし、第2マスク材36を用いて第1絶縁膜15を予め定められた深さまでエッチングする工程と、を具備する。

(もっと読む)

高耐圧半導体デバイス、及び高耐圧半導体デバイスの製造方法

【課題】多層配線形成時のプラズマダメージによるVt変動を利用してVtを制御した高耐圧半導体デバイス、及びその製造方法を提供する。

【解決手段】同一のシリコン基板上に、350Å以上のゲート絶縁膜20、40を有する複数のMOSトランジスタ10、30を備え、ゲート電極12、32が前記ゲート絶縁膜20、40と接している部分の面積Sgと、前記ゲート電極20、40側から見たときに前記ゲート電極20、40上に形成されたコンタクト14、34の総開口面積Scと、の面積比が異なるMOSトランジスタ10、30を有することを特徴とする高耐圧半導体デバイス。

(もっと読む)

半導体製造装置

【課題】配線回路パターンを形成するエッチングにおいて、加工変換差のバラツキを抑制すると共に、ウエハを載置する下部電極の温度を短時間で切り替え可能にする。

【解決手段】本発明の半導体製造装置は、反応室2と、半導体基板5を載置する下部電極4と、反応室2内に下部電極4と対向するように配設された上部電極3とを備え、2つの電極3、4間に高周波電力を供給してプラズマを発生させるように構成されたものであって、反応室2の外側に、発光した光を反応室2の透明な室壁2aを通して上部電極3の周辺部に照射して加熱する発光加熱装置6を配設したものである。

(もっと読む)

半導体装置及びその製造方法

【課題】ドライエッチング時のゲート絶縁膜へのプラズマチャージを抑制した半導体装置

及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、シリコン基板1上に形成されたゲート絶縁膜3

と、ゲート絶縁膜上に形成されたゲート電極12と、ゲート電極上に形成された第1の層

間絶縁膜5と、ゲート電極上のコンタクトホール8と、シリコン基板上に位置するダミー

コンタクトホール8aと、コンタクトホール内、ダミーコンタクトホール内及び第1の層

間絶縁膜上に形成されたAl配線7及びダミーAl配線7aと、第1の層間絶縁膜上、A

l配線及びダミーAl配線上に形成された第2の層間絶縁膜6と、ダミーAl配線の上方

に位置する凹部16と、Al配線上のviaホール9と、凹部下に位置し且つダミーAl

配線上に位置するダミーviaホール9aと、を具備することを特徴とする半導体装置。

(もっと読む)

サブクオーターミクロン適用のための、メタライゼーションに先立つ予備洗浄方法

【課題】半導体基板上のサブミクロン構造について、メタライゼーションに先立つ予備洗浄を提供する。

【解決手段】この方法は、酸素、CF4/O2の混合物またはHe/NF3の混合物のような反応性ガスのプラズマからのラジカルを用いてサブミクロン構造を洗浄することを含み、このプラズマは、好ましくは遠隔プラズマ源により発生され、ラジカルは基板が配置されるチャンバーに供給される。サブミクロン構造内に残留する自然酸化物は、好ましくは、第二の工程において水素を含むプラズマからのラジカルで還元される。第一のまたは両方の洗浄工程に続いて、当該構造は、利用可能なメタライゼーション技術によって金属で充填することができる。これは、典型的には、アルミニウム、銅またはタングステンの蒸着に先立って、露出した誘電体表面にバリア/ライナー層を蒸着することを含む。この予備洗浄およびメタライゼーション工程は、入手可能な一貫処理プラットホーム上で行うことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ウエハレベルCSPにおいて、傾斜面を有する樹脂ポストが存在する場合であっても、樹脂ポスト近辺に微細な再配線を設計どおりに高密度に形成することができ、チップの小型化及び端子数の増加に対応することが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、少なくとも一面に電極3を備えた基板2上の所定位置に、面状をなす第一頂部4aを備えた突起状の第一樹脂ポスト4を形成する工程αと、前記第一樹脂ポストの第一頂部上に、該第一頂部の一部を少なくとも露出させるように、該第一頂部よりも小さい面状をなす第二頂部5aを備えた突起状の第二樹脂ポスト5を形成する工程βと、を少なくとも備えたことを特徴とする。

(もっと読む)

281 - 300 / 898

[ Back to top ]