Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

261 - 280 / 898

基板、特に半導体ウェハの加工

【課題】切削速度、アライメント時間及び歩留りを改善しスループットを高める。

【解決手段】基板の第1の面側から、基板の全深さには満たない所定の深さまで、紫外または可視放射レーザによって溝を掘る。次に、第1の面の反対側である第2の面側から、前記溝が貫通するように基板の材料を除去する。この材料の除去は、例えば、ラッピング及び研磨、化学的エッチング、プラズマエッチングまたはレーザアブレーションによって行う。

(もっと読む)

半導体装置の製造方法

【課題】パッド領域上での堆積物の生成を抑制することのできる、半導体装置の製造方法を提供する。

【解決手段】パッド領域を有する配線層群を形成するステップと、前記配線層群が被覆されるように、絶縁性のカバー層を形成するステップと、前記パッド領域が露出するように、前記カバー層をプラズマエッチングにより除去するステップとを具備し、前記パッド領域は、アルミニウムにより形成され、前記プラズマエッチングにより除去するステップは、炭素ラジカル及びフッ素ラジカルを発生させるCF系ガスを用いて、前記パッド領域を露出させるステップと、前記露出させるステップの後に、塩素ラジカル又は塩素イオンを発生させるCl2系ガスを用いて、前記パッド領域の表面に生成した堆積物を除去するステップとを備える。

(もっと読む)

半導体装置

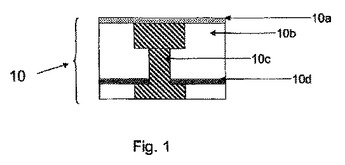

【課題】破壊検査をしなくても、形成された貫通孔に係る良否の状態を推定することができ、貫通電極の品質が保証された半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板2の一方の面2aに配された絶縁層3と、前記絶縁層上に配された導電層3と、前記半導体基板の他方の面2bから前記導電層の少なくとも一部が露呈するように前記半導体基板内に配された第一貫通孔6と、前記半導体基板の他方の面から前記絶縁層の少なくとも一部が露呈するように前記半導体基板内に配された第二貫通孔7と、を少なくとも備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 選択性トップバリアを用いた配線におけるリークを抑制することができ、配線の信頼性の向上をはかる。

【解決手段】 埋め込み配線を有する半導体装置の製造方法であって、配線間絶縁膜102上に該絶縁膜102とは材料の異なる犠牲膜103を形成した後、犠牲膜103及び配線間絶縁膜102を選択的にエッチングして配線用溝105を形成し、次いで配線用溝105内にCuを主成分とする導電膜107を埋め込み形成し、次いで導電膜107の上面に選択的にトップバリア層108を形成し、次いで犠牲膜103を除去することによりメタル残渣108aを除去する。

(もっと読む)

デュアルダマシンビア充填用組成物

デュアルダマシンプロセスに使用される組成物が開示される。  (もっと読む)

(もっと読む)

カーボンナノチューブベースの水平相互接続アーキテクチャ

【課題】本発明は、少なくとも二つのボンディングパッド間に水平方向の電気接続を確立することを可能にする装置に関する。

【解決手段】本装置はボンディングパッドの垂直壁を接続する水平なカーボンナノチューブを備え、ボンディングパッドは少なくとも二つの物質を積層させることによって形成されていて、その一つはナノチューブ成長に触媒作用をもたらし、他の一つはナノチューブ成長に触媒作用をもたらす物質の層間のスペーサとして機能する。

(もっと読む)

半導体装置およびその製造方法

【課題】TFTに接続された各配線を形成する際のプラズマエッチング工程においてチャージアップに起因するプラズマダメージが生じることを防止する。

【解決手段】TFT10のソース領域13sに接続されたソース配線17s、TFT10のドレイン領域13dに接続されたドレイン配線17d、およびTFT10に対して電気的に接続されない配線18を共通のプラズマエッチング工程によって形成する際、ソース配線17sとドレイン配線17dとの間隔を、ソース配線17sと配線18との間隔およびドレイン配線17dと配線18との間隔よりも狭くする。

(もっと読む)

相互接続構造体およびその形成方法(エレクトロマイグレーション耐性強化のための相互接続構造体)

【課題】 ビア開口の下部分を多層ライナで内側を覆うことにより強化したエレクトロマイグレーション耐性を有する相互接続構造体を提供する。

【解決手段】 多層ライナは、誘電体材料のパターン付けされた表面から外側に、拡散障壁、マルチ材料層、及び金属含有ハード・マスクを含む。マルチ材料層は、下層の誘電体キャッピング層からの残留物からなる第1材料層と、下層の金属キャッピング層からの残留物からなる第2材料層とを含む。本発明はまた、誘電体材料内に形成されたビア開口の下部分内に多層ライナを含む相互接続構造体を形成する方法を提供する。

(もっと読む)

パターン形成キャップを用いるエアギャップ形成と一体化

【課題】 膜をパターン形成する方法及びこれらの得られた構造を提供する。

【解決手段】 実施形態において、基板、例えば、ダマシン層の上にアモルファス炭素マスクを形成する。アモルファス炭素マスクの上にスペーサ層を堆積させ、スペーサ層をエッチングして、スペーサを形成するとともにアモルファス炭素マスクをさらす。アモルファス炭素マスクを選択的にスペーサまで除去して、基板層をさらす。ギャップ充填層がスペーサの周りに堆積されて、基板層を覆うがスペーサをさらす。スペーサを除去して、選択的に基板の上にギャップ充填マスクを形成する。ギャップ充填マスクのパターンは、一実施態様においては、ダマシン層に転写されて、IMDの少なくとも一部を除去するとともにエアギャップを形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チップ裏面に貫通電極および裏面配線を形成すると、貫通電極の一部である裏面配線パッドおよび裏面配線によって、チップ裏面に凸部が形成される。これが原因で、チップ吸着時に空気のリークが起こりチップ吸着力の低下が起きる。

【解決手段】裏面配線パッド4dおよび裏面配線4eを形成する領域に、あらかじめ凹部100を形成する。この凹部100内部に裏面配線パッド4dおよび裏面配線4eを設ける。これにより、裏面配線パッド4dおよび裏面配線4e厚さのため生じる凸部によって、チップ1C裏面の平坦性が確保され、チップ1Cを取り扱う際の吸着力の低下が起きない。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極構造を有する半導体装置において、半導体基板と裏面配線との間に形成される絶縁膜の信頼性を向上させることにより、高品質の半導体装置を提供する。

【解決手段】

その表面に表面電極が形成された半導体基板の裏面にシリコン酸化膜とシリコン窒化膜とからなる積層絶縁膜を形成する。半導体基板の裏面側から積層絶縁膜および半導体基板をエッチングして表面電極に達する貫通孔を形成する。貫通孔の側壁および底面と積層絶縁膜を覆う絶縁膜を形成した後、この絶縁膜を部分的にエッチングして貫通孔の底面において表面電極を露出させるとともに貫通孔側壁の絶縁膜を残す。その後、貫通孔の内部を充たし且つ積層絶縁膜を覆う導電膜を形成して貫通孔内部に表面電極に接続された貫通電極を形成するとともに、積層絶縁膜上に裏面配線を形成する。

(もっと読む)

半導体装置の製造装置及びその製造方法

【課題】Al合金膜のシリコン残渣が除去できて、製造工程の簡素化、製造コストが低減される半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法はシリコン基板1上にシリコンを含有するAl合金膜3を形成する工程と、Al合金膜3上にレジストパターン4を設ける工程と、レジストパターン4をマスクとしてAl合金膜3をエッチングする工程と、エッチ後洗浄する工程と、2流体ノズル6によってシリコン残渣5を除去する工程とを備える。

(もっと読む)

半導体装置

【課題】 容量低減とビア加工マージンの確保を効率的に達成する。

【解決手段】 複数の配線層を有する半導体装置であって、所定領域を有する第1配線層26と、第1配線層の上層に位置する第2配線層47と、第1配線層と第2配線層との間に設けられる層間絶縁膜36と、層間絶縁膜と第1配線層の配線との間に設けられるバリア絶縁膜(29,31)とを有し、所定領域における配線上部のバリア絶縁膜の厚さは、所定領域以外の領域における配線上部のバリア絶縁膜の厚さよりも厚く、所定領域においては隣接する配線間にエアギャップ35が形成され、所定領域以外においては隣接する配線間にエアギャップが形成されない。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、絶縁膜のホール内に形成される導電性プラグ等の導電性材料のコンタクト抵抗が基板面内でばらつくのを防止すること。

【解決手段】シリコン基板30の上方に第1の層間絶縁膜45を形成する工程と、第1の層間絶縁膜45の上方に強誘電体キャパシタQを形成する工程と、強誘電体キャパシタQの上方に、水素バリア絶縁膜55、57、62と第2の層間絶縁膜58とを有する積層膜を形成する工程と、エッチングにより積層膜にホール58b、58cを形成する工程と、ホール58b、58c内に金属配線(導電性材料)69を埋め込む工程とを有し、ホール58b、58cを形成する工程において、水素バリア絶縁膜55、57、62のエッチングを、第2の層間絶縁膜58のエッチングとは異なるエッチング手法で行う半導体装置の製造方法による。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理後も十分に低い電気抵抗率を示し、かつ直接接続された透明画素電極とのコンタクト抵抗が十分に低減されると共に、耐食性および耐熱性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Niを0.05〜0.5原子%、Geを0.4〜1.5原子%、および希土類元素群から選ばれる少なくとも1種の元素を合計で0.05〜0.3原子%含有すると共に、NiおよびGeの合計量が1.7原子%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率ゲート誘電膜を用いるpチャネルFETをゲート先作りプロセスにより形成すると閾値が大きくなる。

【解決手段】High-Kゲート誘電膜104の側面と接触するようにHigh-K誘電膜102を形成した後、酸素雰囲気中でアニールする。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、エッチング生成物を直接観察することなくその有無を判断すること。

【解決手段】シリコン基板1の上方に、第1の導電膜19、強誘電体膜20、及び第2の導電膜21を形成する工程と、第2の導電膜21をパターニングして上部電極21aにする工程と、強誘電体膜20をパターニングしてキャパシタ誘電体膜20aにする工程と、レジストパターン30をマスクにして、該レジストパターン30の側面を後退させながら、第1の導電膜19をエッチングし、下部電極19aを形成する工程と、上部電極20aの上面のうち、レジストパターン30の後退を反映して他の領域よりも高位となった段差面21xの幅を測定する工程と、段差面21xの幅C1に基づいて、キャパシタ誘電体膜20aの側面に付着したエッチング生成物の有無を判断する工程とを有する半導体装置の製造方法による。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗率を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ耐食性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、該Al合金膜は、Coを0.05〜0.5原子%、およびGeを0.2〜1.0原子%含み、かつAl合金膜中のCo量とGe量が下記式(1)を満たすことを特徴とする表示装置用Al合金膜。

[Ge]≧−0.25×[Co]+0.2 …(1)

(式(1)中、[Ge]はAl合金膜中のGe量(原子%)、[Co]はAl合金膜中のCo量(原子%)を示す)

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、簡便な手法で半導体基板の端面と裏面側の周縁部とをクリーニングすること。

【解決手段】シリコン基板50の縁部を保持する工程と、シリコン基板50の裏面Aの周縁部Rにブラシ12を摺接させることにより、シリコン基板50の裏面Aに付着している堆積物を除去する工程とを有し、上記の堆積物を除去する工程において、ブラシ12の一部をシリコン基板50の裏面Aからはみ出させる半導体装置の製造方法による。

(もっと読む)

配線構造及び表示装置

【課題】 接続不良の発生や配線層へのダメージの付与を防止することができ、歩留まり良く信頼性の高い接続状態を実現することが可能な配線構造及び表示装置を提供する。

【解決手段】 基板上に形成された配線の幅広部分(配線部22)において、配線上に形成された絶縁膜23に設けられたコンタクトホールを介して外部接続用の接続パッド(例えばOLBパッド4)との電気的接続が図られてなる配線構造である。配線を覆う絶縁膜23が塗布方式により形成された絶縁膜23であり、幅広の配線部22においては、周辺領域にのみコンタクトホール26が形成されている。あるいは、幅広の配線部22の周辺領域に形成されたコンタクトホール26の開口寸法が、内部領域に形成されたコンタクトホール28,29の開口寸法よりも小となるように形成してもよい。

(もっと読む)

261 - 280 / 898

[ Back to top ]