Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

181 - 200 / 898

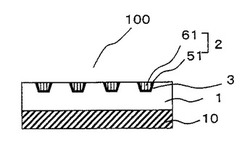

複合体、複合体の製造方法及び半導体装置

【課題】複合体の樹脂層に形成された高密着、高信頼性、高周波対応の微細配線やビアを有する複合体、複合体の製造方法及び半導体装置を提供する。

【解決手段】樹脂層1と導体層2とを含む第1の複合体100であって、前記樹脂層1の表面に最大幅が1μm以上、10μm以下の溝3と当該溝3内部に導体層2を有し、当該導体層2と接する前記樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下である、及び/又は、前記樹脂層1に直径が1μm以上、25μm以下のビア孔と当該ビア孔内部に導体層2を有し、前記ビア孔内部の樹脂層1の表面の算術平均粗さ(Ra)が0.05μm以上、0.45μm以下であることを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアと配線の間に位置ずれが生じても、エアギャップとビアが繋がることを抑制できるようにする。

【解決手段】配線162は第1絶縁層120に埋め込まれており、上面が第1絶縁層120の上面より高い。エアギャップ128は、配線162と第1絶縁層120の間に位置している。第2絶縁層200は、少なくとも第1絶縁層120上及びエアギャップ128上に形成されている。本図に示す例では、第2絶縁層200は配線162を被覆していない。エッチングストッパー膜210は、少なくとも第2絶縁層200上に形成されている。本図に示す例では、エッチングストッパー膜210は、第2絶縁層200上及び配線162上に形成されている。第3絶縁層220はエッチングストッパー膜210上に形成されている。ビア262は第3絶縁層220に埋め込まれており、配線162に接続している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線間容量の低い半導体装置を安定的に形成する。

【解決手段】配線1間に、仕切層5aで仕切られた複数の空洞の溝2を形成し、その後、それらの溝2を覆うように、配線1及び仕切層5aの上側に絶縁膜を形成する。配線1間に仕切層5aを設けることにより、絶縁膜形成に用いる絶縁膜原料3aの溝2内への進入が抑えられ、溝2内の絶縁膜形成が抑えられるようになる。それにより、配線1間の容量が低く、また、容量のばらつきが抑えられた半導体装置が形成可能になる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

成膜方法および半導体装置の製造方法

【課題】誘電率が低くかつエッチング耐性に優れた窒化シリコン系絶縁膜を形成する。

【解決手段】基材上にシラン系ガス(DCS)、窒化性ガス(NH3)及びホウ素含有ガス(BCl3)を、N2パージを逐次行いながらこの順で供給してホウ素含有窒化シリコン層を形成する工程と、このホウ素含有窒化シリコン層に、プラズマにより活性化された窒化性ガス(活性化NH3)を供給する工程とを含み、これらの工程をこの順で繰り返し行う成膜方法。

(もっと読む)

薄膜トランジスタの製造方法及び表示装置の製造方法

【課題】レジスト組成物を用いたマスクパターンを用いることなくTFT及びそれを用いた表示装置を製造することを目的とする。

【解決手段】ロールツーロール方式により加工処理を行う表示装置の製造方法であって、組成物の吐出口が一軸方向に複数個配列した第1の液滴吐出手段により、可撓性を有する基板上に開口部を有する絶縁性樹脂膜を形成し、組成物の吐出口が一軸方向に複数個配列した第2の液滴吐出手段により、開口部にゲート電極を形成し、プラズマの噴出口が一軸方向に複数個配列したノズル体を備えた被膜形成手段により、ゲート電極および絶縁性樹脂膜上にゲート絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法

【課題】プラズマ雰囲気の周囲に存在する銅による影響を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上方に絶縁膜18〜21を形成する工程と、絶縁膜18〜21上にレジスト膜24を形成する工程と、レジスト膜24の上方にマスク膜25を形成する工程と、マスク膜25の上方にレジストパターン27を形成する工程と、レジストパターン27をマスクにしてマスク膜25をエッチングする工程と、酸素ガスとハイドロフロロカーボンガスの混合ガスを導入し、30mTorr以上の圧力の雰囲気内で、マスク膜25から露出する領域のレジスト膜24をエッチングする工程とを有する。

(もっと読む)

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

電界効果トランジスタ

【課題】従来の光学素子に電界効果トランジスタを適用するとき、PN接合部の光リークを抑えるために、トランジスタの周囲に遮光領域を設定する必要が有り、回路面積が大きくなるという課題があった。また、反射光に対して遮光性が十分でないという問題があった。

【解決手段】本発明の電界効果トランジスタは、ゲート電極上に、PN接合部に平面的に重なるように遮光部材を有する。この遮光部材により、PN接合部を遮光することができる。また、電界効果トランジスタ面積が増大しないため、回路の面積を小さく設定できる。

(もっと読む)

半導体装置の製造方法

【課題】多孔質絶縁膜を疎水化する半導体装置の製造方法を提供する。

【解決手段】基板3に多孔質絶縁膜2を形成する工程(S101)と、多孔質絶縁膜2が形成された基板3をチャンバー1内に配置する工程(S102)と、基板3が配置されたチャンバー1内にシロキサンを投入するとともに基板3を第一の温度に昇温する工程(S103)と、投入されたシロキサンが付着した基板3を第一の温度よりも高い第二の温度に昇温する工程(S104)と、を含む。S103では、チャンバー1内の圧力を1kPa以下とする。また、第一の温度は、チャンバー1内の圧力がシロキサンの飽和蒸気圧となる温度以上であり、かつ、多孔質絶縁膜2とシロキサンとが重合反応を開始する温度以下である。

(もっと読む)

半導体装置の製造方法

【課題】洗浄処理での腐食を抑えた高性能で高品質の半導体装置を提供する。

【解決手段】例えば、LCOSデバイスにおける画素電極90を形成する際、画素電極90の材料となる層に、間口の開口幅A1に対して底部の開口幅A2が狭い溝91を形成して、個々の画素電極90を形成した後、洗浄処理を行う。溝91の間口を広くすることで、洗浄処理時の液の滞留が抑えられ、画素電極90の腐食が抑えられるようになる。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板の側面下端のエッジ部を保護し、且つ、装置全体を薄型化する。

【解決手段】 シリコン基板1の側面に形成された円弧状に凹んだ傾斜面13にはアモルファスシリコンやポリイミド系樹脂等からなる側部保護膜14が設けられている。これにより、シリコン基板1の側面下端のエッジ部1aを保護することができる。この場合、側部保護膜14の下端部下面はシリコン基板1の下面と面一となっているので、シリコン基板1の下面に樹脂保護膜を形成する場合と比較して、薄型化することができる。

(もっと読む)

基板処理方法および基板処理装置

【課題】Cu表面の酸化銅の除去および層間絶縁膜に付着したCu含有物残渣の除去を効率良く確実に行うことができる基板処理方法を提供すること。

【解決手段】基板上のCu配線構造におけるCu表面の酸化銅膜および層間絶縁膜に付着したCu含有物残渣を有機酸含有ガスを用いて除去するにあたり、基板温度が相対的に低温の第1の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給してCu含有物残渣のエッチング除去を行う第1工程と、基板温度が前記第1の温度よりも高温の第2の温度になるように基板を加熱しつつ基板に有機酸ガスを含む処理ガスを供給して前記Cu表面の酸化銅膜を還元を主体とする反応により除去する第2工程とを行う。

(もっと読む)

プラズマエッチング方法、プラズマエッチング装置および記憶媒体

【課題】高速電子による有機膜の改質効果を十分に発揮することができるプラズマエッチング方法を提供すること。

【解決手段】プラズマエッチングによりエッチング対象膜にホールを形成するにあたり、プラズマ生成用高周波電力印加ユニットをオンにして処理容器内にプラズマを生成する第1条件と、プラズマ生成用高周波電力印加ユニットをオフにして処理容器内のプラズマを消滅させる第2条件とを交互に繰り返し、第1の直流電源から、第1条件の期間よりも第2条件の期間のほうが印加電圧の絶対値が大きくなるように負の直流電圧を印加する。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、固体撮像装置の駆動方法、及び電子機器

【課題】固体撮像装置が形成されるチップ面積の縮小化が図られ、チップ単体のコストの低減が図られた固体撮像装置を提供する。また、その固体撮像装置を用いることにより、小型化が図られた電子機器を提供する。

【解決手段】本発明の固体撮像装置は、光電変換部PDが形成された第1の基板80と、電荷蓄積容量部61及び複数のMOSトランジスタが形成された第2の基板81が張り合わされた構成とされている。また、第1の基板80と、第2の基板81にはそれぞれ接続電極(26,27,56,57)が形成されており、第1の基板80と第2の基板81は、接続電極により電気的に接続されている。これにより、グローバルシャッタ機能を有する固体撮像装置をより小さい面積に形成することが可能となる。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上とホール内に形成したカーボンナノチューブを絶縁膜に損傷を与えることなく絶縁膜上から除去すること。

【解決手段】配線15a上方に絶縁膜17、18を形成し、絶縁膜17、18をパターニングして配線15aに達するホール17aを形成し、ホール17a内と絶縁膜17、18上面にカーボンナノチューブ22を形成し、カーボンナノチューブ22の層の上に第2絶縁膜23を形成し、第2絶縁膜23をエッチングすることによりカーボンナノチューブ22を露出するとともに、カーボンナノチューブ22の層の凹部に第2絶縁膜23を残し、カーボンナノチューブ22をエッチングしてカーボンナノチューブ22の上端の位置を揃え、さらにカーボンナノチューブ22上の第2絶縁膜23をエッチングし、カーボンナノチューブ22をエッチングして絶縁膜17上面から除去するとともにホール17a内に残す工程を含む。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子機器

【課題】端子間の接合性に優れ高い信頼性を備えたものにするとともに、端子の狭ピッチ化も容易に対応できる半導体装置、半導体装置の製造方法、及び電子機器を提供する。

【解決手段】本発明の半導体装置1は、半導体基板10と、半導体基板10に形成された貫通孔7内に設けられるとともに、半導体基板10の能動面10Aと反対側の裏面10Bに部分的に突出する貫通電極5と、を有し、貫通電極5は、樹脂コア9と、樹脂コア9の少なくとも一部を覆う導電膜15と、を有し、貫通孔7は、内壁面7aの少なくとも一部が能動面10A側に向かって貫通孔7の内径を狭めるテーパー形状となっている。

(もっと読む)

半導体装置

【課題】金属配線と金属酸化物を有する層を形成する際、電蝕といわれる腐食の発生をおさえることにより、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的とする。

【解決手段】配線は、耐酸化性金属からなる第1の層と、その上に形成されたアルミニウムもしくはアルミニウムを主成分とする第2の層と、その上に形成された耐酸化性金属からなる第3の層からなる3層構造とし、前記配線と電気的に接続する金属酸化物を有する層を有する。また、第2の層の上面及び下面は第1及び第3の層と接し、側面は酸素とアルミニウムを含む酸化層と接する。

(もっと読む)

181 - 200 / 898

[ Back to top ]