Fターム[5F033RR25]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 有機SOG膜(有機物質) (606)

Fターム[5F033RR25]に分類される特許

21 - 40 / 606

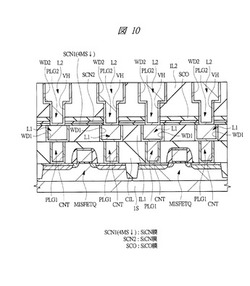

半導体装置およびその製造方法

【課題】半導体装置を構成する配線の信頼性向上を図る。

【解決手段】テトラメチルシランガスの流量を通常条件よりも下げて形成したSiCN膜SCN1(4MS↓)と、このSiCN膜SCN1(4MS↓)上に形成され、通常のテトラメチルシランガスの流量で形成したSiCN膜SCN2と、このSiCN膜SCN2上に形成されたSiCO膜SCOからバリア絶縁膜を構成する。これにより、耐透水性の向上と低誘電率化をバランス良く実現することができる。

(もっと読む)

半導体装置の製造方法

【課題】本実施形態は、耐熱性に乏しいMTJ素子等の素子の劣化を避けつつ、良好な半導体装置を形成することができる半導体装置の製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に複数の素子を形成し、複数の素子の間を埋め込むようにシリコン化合物膜を形成し、マイクロ波を照射することにより、シリコン化合物膜を酸化シリコン膜に改質する。

(もっと読む)

表面被覆方法、並びに半導体装置、及び実装回路基板

【課題】配線及び絶縁膜へダメージを与えることなく、絶縁膜上の導電性の不純物によるめっきの異常成長を抑制することができる表面被覆方法、並びに該方法を用いて製造される半導体装置、及び実装回路基板の提供。

【解決手段】水溶性樹脂、有機溶剤、及び水を含有する表面被覆材料を、表面に露出した絶縁膜及び表面に露出したパターニングされた金属配線を有する積層体の少なくとも前記絶縁膜の表面を覆うように塗布し、前記絶縁膜の表面に被膜を形成する表面被覆方法である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の容量の増大が実現される半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に形成されており、配線および絶縁層により構成された配線層が複数積層された多層配線層と、平面視において、半導体基板1内の記憶回路領域に形成されており、多層配線層内に設けられた凹部40内に埋め込まれた少なくとも1以上の容量素子19および周辺回路を有する記憶回路200と、平面視において、半導体基板1内の記憶回路領域とは異なる領域である論理回路領域に形成された論理回路100と、当該凹部40内において、下部電極14、容量絶縁膜15、及び上部電極16から構成される前記容量素子19上に積層している上部接続配線18と、容量素子19が埋め込まれている配線層のうち最上層に設けられた論理回路100を構成する配線8bの上面に接するように設けられたキャップ層6cと、を備え、上部接続配線18の上面30とキャップ膜6cの上面34とが、同一面を構成している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実効誘電率が低く、かつ信頼性の高いバリア絶縁膜を有する半導体装置を提供することができる。

【解決手段】半導体装置100は、層間絶縁膜10と、層間絶縁膜10中に設けられた配線20と、層間絶縁膜10上および配線20上に設けられたSiN膜30と、を備え、FTIRによって測定したSiN膜30のSi−N結合のピーク位置が845cm−1以上860cm−1以下である。これにより、配線金属の拡散を防ぐためのバリア絶縁膜である窒化シリコン膜において、リーク電流を抑制することができる

(もっと読む)

半導体装置の製造方法

【課題】SOD法によって形成するシリコン酸化膜に、ボイドが発生することを抑制する。

【解決手段】基板、基板表面に形成された溝状領域G、及び溝状領域Gに埋設されたシリコン酸化膜8を有する半導体装置の製造方法であって、溝状領域Gを含む基板の表面を覆うライナー膜6を形成するライナー膜形成工程と、ライナー膜6の表面を水洗する水洗工程と、水洗後の残留水分を除去する水分除去工程と、基板表面にポリシラザン溶液をスピンコートにより塗布する塗布工程と、アニールによりポリシラザン溶液をシリコン酸化膜8に改質する改質工程とを備える。

(もっと読む)

半導体装置

【課題】機械的強度が比較的弱い材料を層間絶縁膜の材料として用いる場合であっても、集積度が高く、信頼性の高い半導体装置を提供する。

【解決手段】支持基板10と、支持基板上に形成され、絶縁層26,28,38,44,50,56,62,68を介して複数の配線36,42,48,54,60,66を積層して成る多層配線構造と、多層配線構造上に形成された電極パッド78と、多層配線構造を貫いて支持基板に達し、電極パッドを支持する構造物76であって、断面が十字形又はY字形である構造物とを有している。この構造物により電極パッドが支持されているため、ボンディングを行った際に電極パッドの下方に存在する構成要素に大きなストレスが加わるのを防止することができ、多層配線構造の一部に、機械的強度が比較的弱い層間絶縁膜を用いた場合であっても、微細な配線パターンの変形や断線等、トランジスタの破壊等を防止することができる。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

半導体装置

【課題】 製造が容易でかつ絶縁性に優れ、平坦な上面(表面)を持つパッシベーション構造を備えた配線構造を、低コストかつ短リードタイムで形成する、半導体装置を提供する。また、配線抵抗が小さくボンディング耐性が高い配線構造を提供する。

【解決手段】 所望の素子領域の形成された基板表面に形成された配線層と、前記配線層表面を覆う層間絶縁膜と、前記層間絶縁膜表面全体を覆うように形成された窒化シリコン膜と、前記窒化シリコン膜の上層に形成された最上層メタルとしての金層からなるメタル配線層と、前記窒化シリコン膜と前記メタル配線層との間に形成されたバリア層と、前記メタル配線層上に形成されたポリイミドからなる平坦化絶縁膜とを含み、前記バリア層と前記配線層は、前記窒化シリコン膜と前記層間絶縁膜に形成されたスルーホールを通じて接続されており、前記平坦化絶縁膜が一部領域で除去せしめられ、前記メタル配線層にボンディングがなされていることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間の容量低減を実現するとともに、ミスアライメント・ビアを対策する。

【解決手段】配線上及び配線間のスペース領域に絶縁膜74を形成し、隣接配線間隔が狭い配線の上面を露出するスルーホールの周辺領域の絶縁膜74をリザーバーとして残して、周辺領域以外の絶縁膜74を除去し、絶縁膜74が除去された配線間のスペース領域に空隙を残しつつ、配線上に絶縁膜77を形成する。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

銅技術相互接続構造を使用する集積回路デバイス用のアルミニウム・パッド電力バスおよび信号ルーティング技術

【課題】電力バス相互接続構造の工程数を低減して製造できる半導体装置の製造方法を提供する。

【解決手段】第1のパッシベーション・スタック149を、導電性ランナ132、134および誘電体層162の上に形成する。開口を、通常のリソグラフィ技術および誘電エッチング技術によって、第1のパッシベーション・スタックを貫通して画定し形成する。露出された表面上に導電性バリア層166を形成する。アルミニウム層をブランケット堆積して、開口を充填する。パターニング、エッチング工程によって、開口内に、アルミニウム・パッド170を形成する。開口内に、ランナ134と導電性接触する導電性バイア172を形成する。アルミニウム・パッドを形成するために用いられるのと同じパターニング、エッチング工程において、アルミニウム層内に電力バス174も形成する。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

電子部品の製造方法及び電解めっき装置

【課題】シード膜の溶解を抑制し、電解めっき後のめっき膜の未析や欠陥の発生を低減する方法を提供する。

【解決手段】実施形態の電子部品の製造方法は、シード膜形成工程S110とめっき工程S114とを備えたことを特徴とする。かかるシード膜形成工程S110では、基体上にシード膜を形成する。そして、かかるめっき工程S114では、窒素ガスでバブリングされているめっき液が供給されためっき槽中の前記めっき液に前記シード膜を浸漬させ、前記シード膜をカソードとして電解めっきを行なう。

(もっと読む)

半導体装置

【課題】MEMSキャパシタとその制御用集積回路を反りの抑えられた1枚の基板上に有する半導体装置を提供する。

【解決手段】貫通孔を含む貫通孔領域を有する基板と、前記基板の上方のMEMSキャパシタと、前記MEMSキャパシタの下方の前記MEMSキャパシタの制御用集積回路とを有する半導体装置を提供する。前記制御用集積回路は、前記基板上のトランジスタを含む。前記MEMSキャパシタの真下の前記基板上の領域と前記貫通孔領域とは、少なくとも一部において重なる。

(もっと読む)

絶縁パターン形成方法及びダマシンプロセス用絶縁パターン形成材料

【課題】 煩雑なエッチング工程等を施すことなく、簡便に多層構造が形成できる、絶縁パターン形成方法及び樹脂組成物を提供すること。

【解決手段】 〔I〕基板上に有機パターンを形成する工程と、

〔II〕前記有機パターンのパターン間に絶縁材料を埋め込む工程と、

〔III〕前記有機パターンを除去し、前記絶縁材料からなる反転パターンを得る工程と、

〔IV〕得られた反転パターンを硬化させる工程と、

を有することを特徴とする、絶縁パターン形成方法と、ダマシンプロセス用絶縁パターン形成材料を提供する。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

21 - 40 / 606

[ Back to top ]