Fターム[5F033RR25]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | 有機SOG膜(有機物質) (606)

Fターム[5F033RR25]に分類される特許

81 - 100 / 606

半導体装置の製造方法

【課題】製造過程の絶縁膜の剥離や飛散を抑制して半導体装置を歩留まり良く製造する。

【解決手段】ウェーハの上方に下地となる第1絶縁膜を介して第2絶縁膜を形成し(ステップS1,S2)、熱処理を行った後(ステップS3,S4)、その熱処理後の第2絶縁膜の一部を選択的に除去する(ステップS5)。熱処理の間、第1絶縁膜を第2絶縁膜で覆い、熱処理時の第1絶縁膜の剥離及び飛散を抑制する。

(もっと読む)

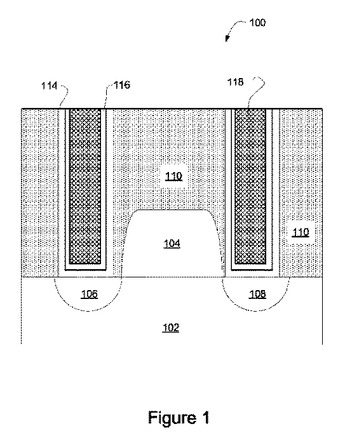

半導体装置の製造方法

【課題】デポ物を充分除去することを可能とし、かつシリサイド層表面を酸化することが無い洗浄工程を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置100の製造方法は、Niを含むシリサイド層104の上面に形成された絶縁層をドライエッチングして、Niを含むシリサイド層104を露出させる工程と、Niを含むシリサイド層104を還元性を有する還元水で洗浄する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】配線パターンの形状に異常を生じず且つサイズの小さい多層配線構造の半導体装置を提供する。

【解決手段】層間絶縁膜を挟んで互いに対向して形成された上下の配線路の一方の配線幅を大、他方の配線幅を小とし、且つ、同一の配線層において互いに隣接する配線路の配線幅を大小交互に形成する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上とホール内に形成したカーボンナノチューブを絶縁膜に損傷を与えることなく絶縁膜上から除去すること。

【解決手段】配線15a上方に絶縁膜17、18を形成し、絶縁膜17、18をパターニングして配線15aに達するホール17aを形成し、ホール17a内と絶縁膜17、18上面にカーボンナノチューブ22を形成し、カーボンナノチューブ22の層の上に第2絶縁膜23を形成し、第2絶縁膜23をエッチングすることによりカーボンナノチューブ22を露出するとともに、カーボンナノチューブ22の層の凹部に第2絶縁膜23を残し、カーボンナノチューブ22をエッチングしてカーボンナノチューブ22の上端の位置を揃え、さらにカーボンナノチューブ22上の第2絶縁膜23をエッチングし、カーボンナノチューブ22をエッチングして絶縁膜17上面から除去するとともにホール17a内に残す工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率が小さい層間絶縁膜に形成された配線の配線密集部に生じるエロージョンを抑制して、比誘電率が小さい層間絶縁膜の露出を防止できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたELK膜12と、該ELK膜12の上に形成されたSiN膜13と、ELK膜12及びSiN膜13に形成され、実質的に同一の高さに配置された複数の配線16とを有している。複数の配線16は、単位面積当たりの配線占有率である第1の配線面積率を持つ配線非密集部Aと、第1の配線面積率よりも高い第2の配線面積率を持つ配線密集部Bとを有し、SiN膜13における配線密集部Bの上面の高さは、SiN膜13における配線非密集部Aの上面の高さよりも低い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】、配線層とその下層のプラグ層との配線抵抗を抑えながら下層のプラグの埋め込み性を向上させることが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、Cu配線10と、Cu配線10の下層側でCu配線10と接触して接続されるCuプラグ20と、Cuプラグ20の底面側及び側面側に配置された、Cuに対してバリア性を有するBM膜240と、Cu配線10とCuプラグ20との内Cuプラグ20側に選択的に、かつCuプラグ20とBM膜240との間に介在するように配置された、BM膜240よりも前記導電性材料に対して濡れ性が高いRu膜242と、Cu配線10とCuプラグ20とが接触する箇所を少なくとも除くCu配線10の底面側と、Cu配線10の側面側とに配置された、Cuに対してバリア性を有するBM膜244と、を備えたことを特徴とする。

(もっと読む)

組成物

【課題】本発明は、上記問題点を解決するため、半導体素デバイスなどにおける層間絶縁膜として使用するのに適し、適当な均一な厚さを有する膜の形成可能で、かつ誘電率、ヤング率等の特性に優れた膜を製造することができる膜形成用組成物、およびその膜形成組成物より得られる絶縁膜を提供することを目的とする。

【解決手段】加熱、光照射、放射線照射またはそれらの組み合わせにより、その一部が脱離して揮発性成分を生じ、残部に不飽和基を生成する官能基を有する化合物(X)を含有する組成物。

(もっと読む)

エレクトロマイグレーション耐性を有するビア・ライン相互接続体

【課題】 エレクトロマイグレーション耐性を有するビア・ライン間相互接続構造体及びその製造方法を提供する。

【解決手段】 導電性ビアの上層金属ライナと、下方の金属ラインの下層金属ライナとの間に、ライナ・ライナ間接触を形成する。ライナ・ライナ間接触は、急激なエレクトロマイグレーションによる故障を抑制し、金属相互接続構造体のエレクトロマイグレーション耐性を強化する。少なくとも1つの誘電体材料部分は、上層金属ライナと下層金属ライナの間の直接接触を保証するように配置された複数の誘電体材料部分を含むことができる。代替的に、少なくとも1つの誘電体材料部分は、リソグラフィ・オーバーレイ変動の許容範囲内でライナ・ライナ間直接接触が形成されるのを保証するのに十分な、導電性ビア領域との横方向の重なりを有する領域の単一の誘電体部分を含むことができる。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

発光装置の作製方法

【課題】平坦性の向上により、TFTの移動度を向上させ、TFTのオフ電流を低減する

。

【解決手段】基板上に非晶質構造の半導体膜を形成する工程と、前記半導体膜上に結晶化

を促進する金属元素を添加する工程と、加熱処理を行って、前記半導体膜を結晶構造の半

導体膜とする工程と、前記結晶構造の半導体膜に第1のレーザー光を照射する工程と、前

記結晶構造の半導体膜に第2のレーザー光を照射する工程とを有する。レーザー光を照射

する工程を2回設けることにより、結晶構造の半導体膜の平坦化を向上させることができ

る。その結果、TFTの移動度を向上させ、TFTのオフ電流を低減させることができる

。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の寄生容量を低減させて、配線の微細化させた半導体装置を効率よく製造できる方法を提供する。

【解決手段】有機材料からなる低誘電率絶縁膜3を形成した後、電子ビームを照射して低誘電率絶縁膜3の表面側にメチル基の濃度が相対的に低く、親水性を有する改質層31を形成する。さらに、エッチングによって低誘電率絶縁膜3に配線やコンタクトホールなどの溝パターン6を形成し、Cuからなるめっき層10を析出させる。CMP法による研磨で改質層31の少なくとも一部を研磨し、Cuからなる配線や導電性プラグといった導電性パターン11を形成する。

(もっと読む)

半導体構造、半導体構造を形成する方法、および半導体デバイスを操作する方法(信号忠実度および電気的分離が強化されたSOI無線周波スイッチ)

【課題】SOI(セミコンダクタ・オン・インシュレータ)基板内の底部半導体層からの半導体デバイスについて強化された信号分離を可能とする半導体構造、これを製造する方法、およびこれを操作する方法を提供する。

【解決手段】底部半導体層10と反対の導電性タイプを有するドープ接点領域18は底部半導体層10内の埋め込み絶縁体層20の下に設ける。少なくとも1つの導電ビア構造47,77は、相互接続レベル金属ライン94から、中間工程(MOL)誘電体層80、最上部半導体層30内の浅いトレンチ分離構造33、および埋め込み絶縁体層20を通り、ドープ接点領域18まで延びる構造とする。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

半導体構造、半導体構造の形成方法、半導体装置の動作方法(高周波の高調波を減少するためのSOIRFスイッチ)

【課題】SOI基板における容量結合を減少した集積回路を提供する。

【解決手段】底部半導体層と同じ導電型のドーパントを含む第1のドープされた半導体領域18及び反対導電型のドーパントを含む第2のドープされた半導体領域28がSOI基板の埋め込み絶縁層20の直下に形成される。第1のドープされた半導体領域18及び第2のドープされた半導体領域28は、共にグランド電位に接続されるか、又は底部半導体層への少数キャリアの順方向バイアス注入に基づく過剰な電流を生じるには不十分は電圧、即ち、0.6V乃至0.8Vを越えない電位差を保って底部半導体層に対して順方向バイアスされる。上部半導体の半導体装置内の電気信号により誘起される電荷層内の電荷は第1及び第2のドープされた半導体領域に接続されている電気的コンタクトを介して引き出され、これにより半導体装置内の高調波信号を減少させる。

(もっと読む)

銅配線、半導体装置および銅配線形成方法

【課題】拡散バリア層と銅配線本体との密着性を大幅に改善することができるようにする。

【解決手段】この発明は、絶縁層に銅からなる配線本体を備えてなる銅配線において、上記絶縁層と、上記絶縁層に対向して設けられた拡散バリア層と、上記拡散バリア層上に形成された、銅(Cu)からなる配線本体と、を備え、上記拡散バリア層は、マンガン(Mn)に対する酸素(O)の組成比率(比率y/x)を2未満とするマンガン酸化物(組成式:MnxOy(比率y/x<2))を含むマンガン酸化物層を有する、ことを特徴としている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

研磨方法

【課題】 二酸化珪素を主体とする層間絶縁膜とlow−k膜を、共に高速に研磨でき、更には、研磨傷が少なくできる研磨方法を提供する。

【解決手段】 表面に凹部及び凸部を有する層間絶縁膜と、この層間絶縁膜を被覆するバリア層と、前記凹部を充填し、バリア層を被覆する導電性物質層とを有する基板の研磨方法において、導電性物質層を研磨して前記凸部のバリア層を露出させる第1の化学機械研磨工程の後に、基板をショア硬度(Dスケール)で40以上のハードタイプパッド上に押圧した状態で、CMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、バリア層と凹部の導電性物質層と層間絶縁膜とを研磨し、更にショア硬度(Dスケール)で40未満のソフトタイプパッド上に押圧した状態で、上述のCMP用研磨液と同一組成のCMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、導電性物質層と層間絶縁膜を研磨する第2の化学機械研磨工程を行う研磨方法。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】ワード線間に空隙を有する不揮発性半導体記憶装置で、従来に比してワード線間の容量の増大を抑えることができる不揮発性半導体記憶装置を提供する。

【解決手段】シリコン基板1上にゲート絶縁膜11、多結晶シリコン膜12、電極間絶縁膜13および多結晶シリコン膜14が順に積層された積層ゲート構造MGと、積層ゲート構造MGの下部のチャネル領域を挟んで形成されるソース/ドレイン領域と、を有するメモリセルトランジスタが複数隣接して配置され、隣接する積層ゲート構造MG間に空隙AG1,AG2ができるように連続したシリコン酸化膜がメモリセルトランジスタ上に形成され、電極間絶縁膜13の形成位置よりも高い位置での基板面に平行な空隙AG1,AG2の開口面積が、その位置よりも低い位置での基板面に平行な空隙AG1,AG2の開口面積よりも狭くなるように、積層ゲート構造MGの側面にシリコン酸化膜20,21が形成される。

(もっと読む)

ローカルインタコネクトを備えた半導体装置

【課題】ローカルインタコネクトを備えた半導体装置を提供する。

【解決手段】ローカルインタコネクトを備えた半導体装置であって、基板上に配置され、実質的に同一線上にある第1ゲート線構造と第2ゲート線構造、前記第1ゲート線構造の両側の前記基板に形成された第1対ソース/ドレイン領域と前記第2ゲート線構造の両側の前記基板に形成された第2対ソース/ドレイン領域、及び前記第1ゲート線構造と前記第2ゲート線構造の両側の前記基板上に配置され、それらが前記第1対ソース/ドレイン領域のうちの1つと前記第2対ソース/ドレイン領域のうちの1つに接続された一対の導電線を含む半導体装置。

(もっと読む)

81 - 100 / 606

[ Back to top ]