Fターム[5F033VV00]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506)

Fターム[5F033VV00]の下位に属するFターム

ダミー配線 (594)

シールド (219)

電源線 (325)

接地線 (304)

ゲート電極配線 (2,049)

ボンディングパッド、バンプ電極 (1,972)

受動素子 (1,084)

ヒューズ、アンチヒューズ (176)

検査、試験 (365)

マイクロマシン (48)

TFT用 (1,331)

メモリ用 (1,353)

ゲートアレイ用 (13)

Fターム[5F033VV00]に分類される特許

61 - 80 / 673

光電変換装置、撮像システム及びその製造方法

【課題】 フローティングディフュージョン部の容量の増大を抑制することが可能な光電変換装置を提供する。

【解決手段】 光電変換素子と、フローティングディフュージョン部と、転送トランジスタと、増幅トランジスタとが配された半導体基板と、第1の配線層と、第2の配線層とを含む複数の配線層と、を有する光電変換装置において、転送トランジスタのゲート電極と、前記第2の配線層とがスタックコンタクト構造で接続されている。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】基板を貫通するトレンチによって複数の部分領域に分割されてなる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法であって、部分領域の側壁に導電層を形成するメリットだけを享受して、該導電層の形成に伴う悪影響を排除することのできる領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ce,Cea〜Ced,Cek,Celに分割され、前記複数の部分領域のうち、一部の部分領域Cea〜Cedの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、トレンチ31aに絶縁体31bが埋め込まれてなる領域分割基板A20とする。

(もっと読む)

連結導体及びこれを用いた半導体装置

【課題】トレンチゲートを有する半導体装置に関して、ゲートの取り出し抵抗の低減を図り、動作速度の高速化をはかる。

【解決手段】この半導体装置は、リードフレーム30のリード端子30Rの一端に連結導体15を介して電気的に接続されている。この連結導体は、Cu箔で構成され、本体部15Mと、リード端子30Rに当接し、リード端子30Rに接続されるリード接続部15Rと、トレンチMOSFET(チップ)のソースパッドに当接するフィンガー部15Fと、フィンガー部15Fの先端を空間部で一体化する連結部15Bとで構成されている。この連結導体を用いることで、第1の外部取り出し電極を構成するソース電極35s間に第2の外部取り出し電極としてのゲートパッド35gが伸張して形成されている場合にも、低抵抗で信頼性の高い実装が実現される。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

半導体装置

【課題】プロセス加工性と信頼性に優れた半導体装置を提供する。

【解決手段】必要な回路が形成された半導体表面に、エポキシ樹脂、エポキシ樹脂硬化剤及び平均一次粒子径1μm以下の有機フィラーの成分を含む樹脂組成からなる絶縁層を1層又は複数層備え、かつ同一層内及び層間接続の配線導体として銅を用いた回路3を任意の箇所に形成してなる半導体装置。

(もっと読む)

熱型検出器、熱型検出装置及び電子機器

【課題】 熱型検出素子を基体から熱分離する空洞部の深さを規定するスペーサー部材を配線構造として兼用し、かつ、その配線構造により、確実に熱分離できる空洞部の深さを確保することができる熱型検出器、熱型検出装置及び電子機器を提供すること。

【解決手段】 熱型検出器は、基体100と、基体100より突出するスペーサー部材104と、スペーサー部材104に支持される支持部材210と、支持部材に支持される熱型検出素子220と、基体内に配置されて熱型検出素子と接続される検出回路510,520と、熱型検出素子と検出回路とを接続する配線部と、を有する。配線部は、基体内に配置された少なくとも一層の第1導電層LIA,LIBと、スペーサー部材内に配置された少なくとも一層の第2導電層LIC,LIDと、支持部材に支持された第3導電層214,238と、第1,第2及び第3導電層の隣接層同士を接続する複数のプラグHLA〜HLDとを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】孤立パターンに銅の化合物が析出するのを抑制する半導体装置の製造方法と、半導体装置とを提供する。

【解決手段】半導体装置では、素子・基板層ESLの低誘電率膜LOW1、ファイン層FLの極低誘電率膜ELK1等およびセミグローバル層SGLの低誘電率膜LOW2等のそれぞれの開口部に形成されるアライメントマークAMおよび重ね合わせ検査マークKMが、半導体基板SUBに形成された所定の導電型の不純物領域IRに電気的に接続されて、アライメントマークAMおよび重ね合わせ検査マークKMが接地電位に固定されている。

(もっと読む)

配線パターン及びその製造方法並びに半導体装置

【課題】配線パターンを覆う絶縁層をできる限り薄くする。

【解決手段】配線パターン1は、第一の一対の端子3,4及び該第一の一対の端子3,4間を接続する複数の第一の引き回し部5を有する第一の配線2と、第二の一対の端子7,8及び該第二の一対の端子7,8間を接続する少なくとも一つの第二の引き回し部9を有する第二の配線6とを含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置

【課題】規格により規定された速度による信号の転送を実現し、半導体装置やそれを内蔵した電子機器の誤動作を防止する。

【解決手段】第1の半導体素子101の導体配線層106に、パッケージ基板100の信号端子103と第2の半導体素子102の信号端子117とを接続する信号線導体113aと、パッケージ基板100の電源端子104と第2の半導体素子102の電源端子118とを接続する電源導体114とを、信号線導体113aが導体配線層106において、信号線導体113aとの間に水平方向に一定の間隔をあけて隣接する電源導体114に挟まれるように形成する。

(もっと読む)

半導体装置の製造方法、及び固体撮像装置の製造方法

【課題】 精度よく開口を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の絶縁膜となる部材と、第1の絶縁膜となる部材と異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜となる部材と異なる材料の第4の絶縁膜となる部材とがこの順に積層された半導体基板の上に、複数の絶縁膜の開口を形成するための開口を有するマスクを形成する工程と、第3の絶縁膜となる部材のマスクの開口に対応する部分と第4の絶縁膜となる部材のマスクの開口に対応する部分を連続して除去する第1の工程と、第1の工程を行った後に、第2の絶縁膜となる部材のマスクの開口と対応する部分を除去する第2の工程と、を有する。

(もっと読む)

半導体装置

【課題】銅ヒューズに起因する故障または特性悪化を抑制または防止できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、銅ヒューズ4と、半導体基板1と銅ヒューズ4との間に配置された銅膜からなるシール膜7,8と、銅ヒューズ4よりも上の層に形成された銅以外の金属材料膜からなり、銅ヒューズ4の両端にそれぞれに接続された最上層配線501,502と、シール膜7,8に結合され、銅ヒューズ4の周囲を取り囲む筒状に形成された銅シールリング6とを含む。

(もっと読む)

半導体装置

【課題】封止される被対象物に段差部を備えているが、封止部を設けた際に該段差部に起因したボイドの発生が抑制され、ひいては優れた耐食性を備える半導体装置と、その製造方法を提供する。

【解決手段】本発明に係る半導体装置1は、導電性を有する剛体からなる基板2と、該基板の少なくとも一方の面に絶縁部3を介して配された導電部5と、該絶縁部及び該導電部を覆うように配された感光性樹脂からなるフィルム6と、を備えている。前記基板2は、一方の面に開口する凹部及び/又は貫通孔2aを備え、該凹部及び/又は該貫通孔はその内部が略全域にわたって、前記フィルム6により充填されている形態をなす。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、光電変換膜が半導体基板上に積層された積層型の半導体装置に関する。

【解決手段】半導体基板と、半導体基板上に形成され、交互に積層された層間絶縁膜と配線層とからなる多層配線層と、多層配線層内において、半導体基板の周縁に沿って環状に形成されたシールリングとを備え、シールリングは、各配線層に形成された環状のシール配線と、各層間絶縁膜に少なくとも1つ形成された環状のシールビアとが積層された構造であり、シールビアを介して積層方向に隣接する少なくとも1組のシール配線では、下方のシール配線の外周面の位置が、上方のシール配線の外周面の位置よりも外側にあることを特徴とする半導体装置。

(もっと読む)

固体撮像素子、固体撮像素子の製造方法、及び電子機器

【課題】センサ基板と回路基板とを電極間で張り合わせてなる構成において電極間の接合面積を確保することが可能な3次元構造の固体撮像素子を提供する。

【解決手段】光電変換部21が配列形成されたセンサ基板2と、光電変換部21を駆動する回路が形成されセンサ基板2に対して積層された回路基板7と、センサ基板2における回路基板7側の界面に引き出されたセンサ側電極45と、回路基板7におけるセンサ基板2側の界面に引き出された回路側電極65とを備え、センサ側電極45と回路側電極65とは、凹型電極に凸型電極を嵌め合わせた状態で接合されていることを特徴とする固体撮像素子1である。

(もっと読む)

半導体装置およびその製造方法

【課題】 表面側から特性試験が行える縦型の半導体装置を提供する。

【解決手段】 半導体装置10では、半導体基板11は第1の面と、第1の面に対向する第2の面を有している。半導体素子12は半導体基板11のダイシングライン14、15で囲まれた矩形状格子に形成されるとともに、第1の面に形成された第1電極26と、第2の面に形成された第2電極28とを有している。電流は第1電極26と第2電極28の間に流れる。貫通電極16は半導体基板11のダイシングライン14、15で囲まれていない領域に形成されるとともに、一端が第1の面上に延在し、他端が第2電極28と電気的に接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】パッドと当該パッドの下地との密着性の向上および信頼性の向上を図ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1の一表面側に熱酸化膜1bとシリコン窒化膜32と層間絶縁膜50とパッシベーション膜60との積層構造を有する半導体装置であって、熱酸化膜1b上にパッド80を形成してある。半導体装置の製造方法では、半導体基板1の上記一表面側に熱酸化膜1bと熱酸化膜1bの表面の一部を覆うシリコン窒化膜32とを有する基本構造を形成してから、半導体基板1の上記一表面側に層間絶縁膜50を形成する。基本構造の形成にあたっては、シリコン窒化膜32のうち熱酸化膜1bにおけるパッド80の形成予定領域に形成した部分を除去する。層間絶縁膜の形成後であってパッド80の形成前に層間絶縁膜50のうち熱酸化膜1bにおけるパッド80の形成予定領域上に形成されている部分を除去する。

(もっと読む)

半導体チップ及び半導体装置

【課題】フリップチップ接続時における腹打ち現象を防止し、プローブテスト時のダメージに対する耐性を低下させることなく、配線のレイアウトの自由度を向上させる。

【解決手段】半導体チップは、外部素子と接続するパッド部15,25が形成されると共に、電源/GND配線16として利用されるパッドメタル層12と、パッドメタル層12と回路領域とを接続する複数の配線層13と、フリップチップ接続面5の周辺部に設けられプローブテストに利用される周辺パッド部15を含み、パッドメタル層12と少なくとも1つの配線層13とからなる積層構造を有する周辺パッド層18と、フリップチップ接続面5の周辺部より内側に設けられプローブテストに利用されない内部パッド部25を含み、パッドメタル層12のみからなる単層構造を有する内部パッド層28とを備える。

(もっと読む)

半導体ウェハ及び半導体装置

【課題】ウェハを個々のチップに分割する際のダイシングによってチップ側面に生じるクラックがチップ領域内に伝播することを防止し、それにより半導体装置の品質を向上させることを目的とする。

【解決手段】少なくとも2つのシールリング121、122に凹凸を形成し、シールリング121、122間で隣り合う凹凸の突出方向を逆向きにすると共に、突出先端部を近接させることにより、ダイシング等により発生したチップ領域120方向への外力をスムーズにチップ外周部へと逃がすことができるため、半導体ウェハ101を個々のチップに分割する際のダイシングによってチップ側面に生じるクラックがチップ領域120内に伝播することを防止し、それにより半導体装置の品質を向上させることができる。

(もっと読む)

半導体装置

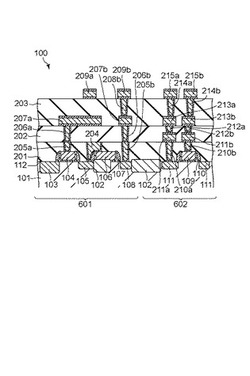

【課題】安定した特性のヒューズ素子を有する半導体装置を提供する。

【解決手段】半導体装置100は、基板10と、基板10の上方に形成され、空洞部20を画成する被覆構造体30と、空洞部20に収容されたヒューズ素子40a,40b,40cと、を含み、被覆構造体30は、導電層を有し、ヒューズ素子40a,40b,40cの材質は、導電層の材質と同じである。

(もっと読む)

61 - 80 / 673

[ Back to top ]