Fターム[5F033VV00]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506)

Fターム[5F033VV00]の下位に属するFターム

ダミー配線 (594)

シールド (219)

電源線 (325)

接地線 (304)

ゲート電極配線 (2,049)

ボンディングパッド、バンプ電極 (1,972)

受動素子 (1,084)

ヒューズ、アンチヒューズ (176)

検査、試験 (365)

マイクロマシン (48)

TFT用 (1,331)

メモリ用 (1,353)

ゲートアレイ用 (13)

Fターム[5F033VV00]に分類される特許

101 - 120 / 673

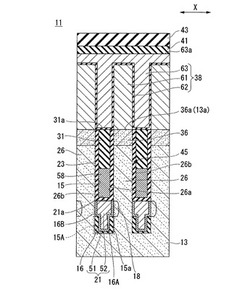

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の検査効率を向上させる。

【解決手段】複数の接続パッド12が設けられた半導体デバイスウエハ10と、半導体デバイスウエハ10の接続パッド12が設けられた面を被覆するとともに、接続パッド12を露出させる開口14aが設けられた絶縁膜14Aと、開口14aから露出された接続パッド12及び絶縁膜14Aの上部に設けられた配線15Aと、を備える半導体装置である。配線15Aは、無電解めっき用シード層16Aと、無電解めっき用シード層16Aを核とする無電解めっきにより形成される配線層19Aと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

成膜付半導体素子、及びその製造方法

【課題】半導体素子を破壊することを防止しつつ半導体素子の金属膜に対し安価に成膜できるとともに容易に厚膜化できる成膜付半導体素子の製造方法を提供すること。

【解決手段】シリコン層11に重ねてアルミ膜12を有する半導体素子10に対しコールドスプレー装置30によって成膜する成膜付半導体素子の製造方法は、第1工程と、第2工程とを有する。第1工程では、コールドスプレー装置30が、アルミ膜12の厚さV1より小さい粒径R1の第1銅粉末41を噴射することにより、アルミ膜12の表面に下地層21を形成する。第2工程では、コールドスプレー装置30が、第1銅粉末の粒径R1より大きく且つ下地層21の表面からアルミ膜12とシリコン層11との境界面までの寸法V2より小さい粒径R2の第2銅粉末42を噴射することにより下地層21に重ねて厚膜層22を形成する。

(もっと読む)

半導体装置

【課題】配線上に配列されて形成されている複数のビアの少なくとも一部が冗長ビアでも、目ズレによる複数の冗長ビアの全滅を防止できる半導体装置を提供する。

【解決手段】半導体装置は、線形の配線4上に配列されて形成されている複数のビア5(5a-5c)を有し、複数のビア5の少なくとも一部が冗長ビア5として形成されており、ビア5の少なくとも一部が配線4の中心線から変位した位置に形成されている。従って、フォトレジストパターニング時に配線4とビア5に目ズレが発生した場合でも、少なくとも冗長ビア5の一つは目ズレの影響が少なく形成できる。

(もっと読む)

半導体装置、半導体装置のレイアウト方法、及びプログラム

【課題】半導体装置において、プロービング領域にて発生したクラック部から侵入した水分をシールリングでブロックし、シールリングより半導体装置の内側に配置されているボンディング領域の下に配線やトランジスタを配置できるようにする。

【解決手段】半導体装置の外縁寄りに配置したプロービング用パッド領域の内側にシールリングを配置し、その内側にボンディング用パッド領域を配置する。なお、プロービング用パッド領域とボンディング用パッド領域は、兼用パッド領域をシールリングで分割したものでも良い。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミング素子からのトリミング時の気化ガスの圧力によりトリミング素子の下部の層間絶縁膜にクラックが入るのを防止する。

【解決手段】層間絶縁膜2上にトリミング素子Tを形成する。トリミング素子Tの上を層間絶縁膜3aで被覆する。トリミング素子Tの斜め上方領域の層間絶縁膜3a上にクラック誘導体Gを形成する。トリミング素子T及びクラック誘導体Gはレーザー光の照射領域に配置される。レーザー光を照射すると、トリミング素子Tの周辺及びクラック誘導体Gの周辺の層間絶縁膜3a等に重畳して広く延在する高温領域6が形成され、該高温化した層間絶縁膜3a等の剛性が低下する。その結果、トリミング素子Tの上辺のコーナー部に気化ガスの圧力がかかりやすくなり、トリミング素子Tの下辺のコーナー部にかかる気化ガスの圧力が小さくなるので、トリミング素子Tの下側の層間絶縁膜2のクラック5発生を防止できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】多層配線層の層間における剥離の有無を簡便な手法で検出できるようにする。

【解決手段】第1電極412は多層配線層20に形成されている。第2電極422は、絶縁膜22の一部を介して第1電極412と対向している。第1電極パッド430は第1電極412に接続している。第2電極パッド432は第2電極422に接続している。そして少なくとも2層以上の絶縁膜22のそれぞれが、第1電極412及び第2電極422に挟まれている。そして第1電極412及び第2電極422により、センサ40の少なくとも一部が形成されている。センサ40は、多層配線層20の層間における剥離の有無を検出するために用いられる。

(もっと読む)

半導体装置

【課題】 動作不良を抑制するのに適する半導体装置を提供すること。

【解決手段】 半導体チップ1と、半導体チップ1に積層された第1電極パッド21と、方向xに延びる第1の縁49aと、方向yに延びる第2の縁とに規定された矩形状を呈する中間層4と、半導体チップ1とともに中間層4を挟むように配置された複数のバンプ5と、を備え、複数のバンプ5のいずれか一つは、複数のバンプ5のうち、方向xの一端且つ方向yの一端に配置され並びに第1電極パッド21に導通する第1バンプ51であり、複数のバンプ5のいずれか一つは、第1電極パッド21に導通する第2バンプ52である。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】Cuを主要な成分とする再配線に設けられた外部接続用Auパッドの剥離を抑制する。

【解決手段】Cu膜15aの上部にNi膜15bを積層した2層膜からなる再配線15の表面には、ワイヤが接続されるパッド18が形成されている。パッド18は、Ni膜19aの上部にAu膜19bを積層した2層膜からなり、再配線15の上面および側面を覆うように一体形成されている。これにより、再配線15とパッド18の接触面積が大きくなるので、パッド18が再配線15から剥がれ難くなる。

(もっと読む)

半導体装置及びその製造方法

【課題】実装基板に信頼性よく実装できる多層構造の再配線を備えた半導体装置を提供する。

【解決手段】バンプ電極18を備えた半導体基板10aと、半導体基板10aの上に形成され、バンプ電極18の横方向に配置された第1絶縁層20と、第1絶縁層20の上に形成され、バンプ電極18に接続された第1配線層30と、第1配線層30の上に形成された第2絶縁層22と、第2絶縁層22に形成され、第1配線層30に到達するビアホールVHと、第2絶縁層22の上に形成され、ビアホールVHに形成されたビア導体40を介して第1配線層30に接続される第2配線層32と、第2配線層32に接続された外部接続端子34とを含み、第2絶縁層22の弾性率は第1絶縁層20の弾性率より低く設定されている。

(もっと読む)

半導体装置及びその製造方法

【課題】low−k膜のワイヤーボンディング時の荷重による変形やクラッキングの発生を回避し、半導体装置の信頼性の低下を抑制することが可能な半導体装置とその製造方法を提供する。

【解決手段】半導体装置において、基板上に形成された絶縁層と、絶縁層上に形成された複数の層間絶縁膜と、層間絶縁膜中にそれぞれ形成される複数の配線層及びビアからなる多層配線と、複数の配線層のうち最下層の配線層より基板側に形成されたメタルパッドと、メタルパッドの一部の領域上の絶縁層及び層間絶縁膜が除去されて形成された開口部と、メタルパッド上に、複数の層間絶縁膜を貫通し、開口部を取り囲むように設けられるパッドリングと、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、製造コストの増加を抑制可能な半導体装置を提供する。

【解決手段】半導体装置1は、半導体基板部10、誘電体膜22、再配線24、上部電極25、絶縁膜26、及び外部接続端子28を有する。半導体基板部10は、回路が形成され、回路にそれぞれ接続される下部電極15、上部電極パッド16、接続パッド17、18を上面に有する。誘電体膜22は、下部電極15を被い、上部電極パッド16、接続パッド17、18の上面に達する開口部を有する。再配線24は、一部の接続パッド17、18に電気的に接続される。上部電極25は、誘電体膜22を介して下部電極15の上面に対向して配置され、上部電極パッド16に接続され、再配線24を含む。絶縁膜26は、誘電体膜22、再配線24、及び上部電極25を被う。外部接続端子28は、絶縁膜26を貫通し再配線24に接続され、絶縁膜26の上面から露出する。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チップ面積及びコストを増大させることなく、熱抵抗を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置100は、半導体層1aと配線層1bとを有する半導体基板1と、半導体層1aの中央部に半導体層1aの表面から所定の深さまで形成された活性領域3と、活性領域3及び活性領域3の周辺の配線層1bに形成され、半導体層1aと電気的に接続された接続用電極4と、半導体層1aから発生する熱を放熱する放熱部とを備え、放熱部は、半導体層1aの裏面から活性領域3の近傍まで凹状に形成された少なくとも1の第1の孔5に充填された放熱体7を有する。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜などの積層構造を低背化しつつ、アライメント用のマークが容易に形成された半導体装置、およびその製造方法を提供する。

【解決手段】半導体基板SUBに形成された光電変換素子PTOと、マーク部のストッパ膜AL1と、ストッパ膜AL1上および光電変換素子PTO上に形成された第1の層間絶縁膜II2と、第1の金属配線AL2と、第2の層間絶縁膜II3とを備える。層間絶縁膜II2、II3を貫通してストッパ膜AL1に達するスルーホールDTHが形成され、スルーホールDTH内の導電層DTの上面に第1の凹部CAVが形成される。第1の凹部CAVの上面の第2の金属配線AL3に、アライメントマークとなる第2の凹部MKを備える。

(もっと読む)

反射型液晶表示装置及びその製造方法

【課題】反射型液晶表示装置において、回路素子へ到達する入射光の量を低減するための技術を提供する。

【解決手段】回路素子に電気的に接続された、第1金属層112の上に、開口部127及び第1スルーホール126を有するようにパターニングされた第1絶縁層113を形成し、第1絶縁層に、開口部127に埋め込まれた金属部114及び第1スルーホール126に埋め込まれた第1プラグ115を形成した後、第2絶縁層116を形成する。第2絶縁層116の上に、開口部を有するようにパターニングされた第2金属層117を形成し、第2金属層の上に第3絶縁層119を形成した後、第2金属層117の開口部を通り且つ第1プラグ115の上面を露出させる第2スルーホール120を、第2絶縁層116及び第3絶縁層119に形成し、第2スルーホール120に埋め込まれた第2プラグ121と、第2プラグに接続された反射電極122とを形成する。

(もっと読む)

101 - 120 / 673

[ Back to top ]