Fターム[5F033VV00]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506)

Fターム[5F033VV00]の下位に属するFターム

ダミー配線 (594)

シールド (219)

電源線 (325)

接地線 (304)

ゲート電極配線 (2,049)

ボンディングパッド、バンプ電極 (1,972)

受動素子 (1,084)

ヒューズ、アンチヒューズ (176)

検査、試験 (365)

マイクロマシン (48)

TFT用 (1,331)

メモリ用 (1,353)

ゲートアレイ用 (13)

Fターム[5F033VV00]に分類される特許

21 - 40 / 673

半導体装置

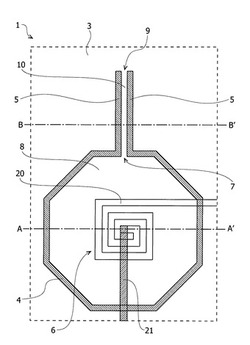

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

半導体装置および基板

【課題】アライメントマークを用いて形成される半導体装置であり、ダイシングおよびクラックに起因する半導体チップの品質低下を抑制し、半導体チップの微細化を容易にすることが可能な構成を有する半導体装置および基板を提供する。

【解決手段】主表面を有する半導体基板と、半導体基板の一方の主表面上に形成された多層構造回路ICと、多層構造回路ICのうち最上層と同一の層に形成される、平面視において多層構造回路を取り囲むように配置される保護壁GRと、最上層と同一の層に形成される位置合わせマークM2Bとを備える。上記位置合わせマークM2Bは少なくとも一部において保護壁GRと接するように形成される。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置

【課題】半導体チップのバンプ電極と実装基板の配線との接続信頼性を向上できる技術を提供する。特に、バンプ電極下の最上層配線層に配線を配置しても、バンプ電極の平坦性を確保してバンプ電極とガラス基板に形成されている配線との接続信頼性を向上できる技術を提供する。

【解決手段】バンプ電極BP1の非重複領域Y直下にある最上層配線層に電源配線や信号配線からなる配線L1と、ダミーパターンDPを形成する。ダミーパターンDPは、配線L1間のスペースを埋めるように配置され、配線L1とスペースによって最上層配線層に生じる凹凸を緩和する。さらに、最上層配線層を覆うように形成される表面保護膜に対してCMP法による平坦化処理を実施する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

(もっと読む)

半導体装置およびその製造方法

【課題】前記半導体装置をスクライブ工程により切り離す際に、クラックが歪みを蓄積した保護膜を伝播して半導体装置内部に侵入するのを抑制し、半導体装置の製造歩留まりを向上させる。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記保護溝部の底面の一部及び前記保護溝部の内側の側壁面に連続して形成された保護膜と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン基板表面に到達する深い溝部であっても、所望の保護溝部形成を安定して行うことができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、活性素子が形成された素子領域を有する基板と、前記基板上に形成され、多層配線構造を含む積層体と、前記積層体中に、前記素子領域を囲んで連続的に延在する耐湿リングと、前記積層体中、前記耐湿リングの外側に、前記耐湿リングに沿って連続的に、前記基板の表面に達して形成された保護溝部と、前記積層体上に形成され、前記保護溝部の外縁に沿って延在する第1のマスクパターンと、前記積層体上に形成され、前記保護溝部の内縁に沿って延在する第2の金属マスクパターンと、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体ダイ上にフィーチャをめっきするためのヒューズバス

【課題】半導体ダイ上に相互接続部又はボンドパッドなどのフィーチャ構造を電気めっきする方法を提供する。

【解決手段】方法は半導体基板の上方に複数のヒューズ(208)を形成する工程と、半導体基板の上方の複数の相互接続層(400〜408)と、該複数の相互接続層の上面の複数の相互接続パッド(502)とを形成する工程と、を含む。シールリング(202)が、半導体基板(302)と、前記複数の相互接続パッド(502)と、前記複数のヒューズ(208,320)とに形成された能動回路を包囲する。各ヒューズ(208,320)は、対応する相互接続パッド(502)とシールリング(202)とに電気的に接続される。各ヒューズ(208)が導通状態にあるとき、該ヒューズは対応する相互接続パッド(502)をシールリング(202)に電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】トリミングヒューズの上の絶縁膜が、トリミングヒューズの機能を高めるために適正な状態を維持することが可能な半導体装置を提供する。

【解決手段】表面を有する絶縁膜III上のヒューズ配線F1と、ヒューズ配線F1上の層間絶縁層II1,II2,PIと、層間絶縁層II1,II2,PIの内部に位置する、ヒューズ配線F1と平面視において重ならない領域に形成された電極部PDとを備える。上記ヒューズ配線F1の真上のうち少なくとも一部の第1の領域において、層間絶縁層II1,II2,PIの厚みが、第1の領域以外の第2の領域における層間絶縁層II1,II2,PIの厚みより薄くなるようにトリミング開口部LTCが形成される。トリミング開口部LTCの内側において側壁および底面の少なくとも一部を覆うアルミニウム薄膜部SALを備える。アルミニウム薄膜部SALは、側壁の少なくとも一部から、底面より上側において上記表面に沿う方向に連なる。

(もっと読む)

ボンディングパッド構造を有する裏面照射型センサーとその製造方法

【課題】ボンディングパッド構造を有する裏面照射型センサーとその製造方法を提供する。

【解決手段】本発明は半導体構造を提供する。半導体構造は、正面と背面を有する装置基板;装置基板の正面上に設置される相互接続構造;および、相互接続構造に接続されるボンディングパッドを含む。ボンディングパッドは、誘電材料層中の凹部領域;凹部領域間に挿入される誘電材料層の誘電体メサ; および、凹部領域中と誘電体メサ上に設置される金属層を含む。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体装置

【課題】配線におけるエレクトロマイグレーション耐性を向上させる。

【解決手段】ソース領域42、ソース領域44およびドレイン領域46を有するP型MOSFET40と、ソース領域52、ソース領域54およびドレイン領域56を有し、かつP型MOSFET40と隣接するN型MOSFET50と、ドレイン領域46およびドレイン領域56に接続するドレイン電極と、ドレイン電極と接続し、かつドレイン電極上に設けられた複数のビア10と、を備え、P型MOSFET40とN型MOSFET50は、インバータ回路を構成しており、ドレイン電極は、ビア10を介しては、インバータ回路の出力信号配線30と接続し、他には接続していない。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

半導体装置

【課題】ダイシング時の衝撃を逃がして、半導体装置の歩留まりを向上させる。

【解決手段】半導体装置100は、シリコン層4上に形成された多層配線構造3内で、平面視において素子形成領域50の外周に形成されたシールリング6と、シールリング6のさらに外周に形成されたダミーメタル構造30a〜ダミーメタル構造30iを含む。ダミーメタル配線24は、内周側に形成されたものほど上層に配置される。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の厚い応力緩和層を有するウェハレベルCSPと称される半導体装置において、第1電極と外部電極との接続不良が発生しにくい半導体装置の製造方法を提供する。

【解決手段】(1)応力緩和層を半導体ウェハの上に形成する工程、(2)応力緩和層の一部を除去した開口部を形成し、半導体ウェハ上の第1電極を露出する工程、(3)第1電極と接続し、開口部を充填するポスト部を形成する工程、(4)外部電極とポスト部を接続するための再配線層を応力緩和層の上に形成する工程、(5)再配線層の上に再配線保護層を形成する工程、(6)再配線保護層の一部を除去して、外部電極を形成するための第2電極を露出する工程、(7)第2電極上に外部電極を形成する工程を含む半導体装置の製造方法。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体パッケージ

【課題】再配線形成前のウエハテストを適切に実施する。

【解決手段】半導体チップ1は、周辺電極パッド30内又はV/G配線20において周辺電極パッド30に相対的に近い位置にある第1の再配線接続部61と、V/G配線20において周辺電極パッド30から相対的に遠い位置にあり、再配線60の形成前における電位が第1の再配線接続部61よりも小さい第2の再配線接続部62とが、再配線60により接続されたものである。半導体チップ1は、第2の再配線接続部62、V/G配線20上の第2の再配線接続部62の近傍で再配線60の形成前における電位が第1の再配線接続部61よりも小さい部分、又は、V/G配線20から第2の再配線接続部62の近傍に引き出され、再配線60の形成前における電位が第1の再配線接続部61よりも小さい導電部に、ウエハテスト用の検査部80を備えている。

(もっと読む)

イメージセンサ構造体、イメージセンサの製造方法およびイメージセンサ

【課題】イメージセンサのカラーフィルターの膜厚のばらつきを低減する。

【解決手段】イメージセンサ構造体は、シリコン基板51上に配列で形成された複数のイメージセンサと、複数のイメージセンサをダイシングして分離するときに切断される、隣り合うイメージセンサの間のスクライブラインと、から構成される。複数のイメージセンサのそれぞれは、シリコン基板51上に形成された拡散層52から構成される複数の光電変換素子と、複数の光電変換素子を囲んで、イメージセンサそれぞれの外周に沿って導体で形成されたガード配線81と、を備える。そして、スクライブライン部53に、ガード配線81と同一のプロセスで同層に形成されたダミー配線82が形成される。

(もっと読む)

21 - 40 / 673

[ Back to top ]