Fターム[5F033WW04]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 濃度 (735)

Fターム[5F033WW04]に分類される特許

121 - 140 / 735

半導体装置の製造方法および半導体装置

【課題】ダマシン配線形成時に、シード膜を配線用溝の側壁に確実に形成する。

【解決手段】下地絶縁膜1の上にプラズマシリコン窒化膜2、プラズマTEOS酸化膜3を形成する。プラズマTEOS酸化膜3は、高周波電源および低周波電源を用いる2周波励起プラズマCVD装置により、膜密度が上部に行くほど小さくなるように形成される。配線用溝をRIE法により形成した後、ウェットエッチングで膜密度が小さい部分を速くエッチングすることでテーパ形状の配線用溝3aを形成する。スパッタでバリアメタル膜4を形成する際に配線用溝3aの側壁にも確実に形成でき、銅膜5のメッキをボイドなしに形成できる。

(もっと読む)

半導体デバイスの層内または層間誘電体としての超低誘電率材料

【課題】約2.6以下の誘電率を有する超低誘電率材料およびその作製する方法を提供すること。

【解決手段】Si原子、C原子、O原子およびH原子を含み、共有結合3次元ネットワーク構造を有し、2.6以下の誘電率を有する、熱的に安定な超低誘電率膜を提供する。この誘電率膜は、さらに、共有結合環状ネットワークを有することもできる。共有結合3次元ネットワーク構造は、Si−O共有結合、Si−C共有結合、Si−H共有結合、C−H共有結合およびC−C共有結合を含み、必要ならFおよびNを含むこともできる。この膜では、必要ならSi原子の一部をGe原子で置換することもできる。この誘電率膜は、1.3マイクロメートル以下の厚さを有し、毎秒10−10メートル以下の水中での亀裂成長速度を有する。さらに、BEOL絶縁体、キャップまたはハード・マスク層として本発明の誘電膜を含むバック・エンド・オブ・ライン(BEOL)相互接続構造も提供する。

(もっと読む)

リソグラフィー用洗浄液及び配線形成方法

【課題】タングステンに対する腐食抑制機能に優れ、かつ、レジスト膜等の除去性能にも優れたリソグラフィー用洗浄液、及びこのリソグラフィー用洗浄液を用いた配線形成方法を提供する。

【解決手段】本発明に係るリソグラフィー用洗浄液は、4級アンモニウム水酸化物と、水溶性有機溶剤と、水と、無機塩基と、下記一般式(1)で表される防食剤とを含有する。

(式中、R1は炭素数1〜17のアルキル基又はアリール基を示し、R2は炭素数1〜13のアルキル基を示す。)

(もっと読む)

表示装置

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、上記腐食防止用塗料の塗布や剥離といった更なる工程を設けることなく、ピンホール腐食を防止することのできる表示装置を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を備えた表示装置であって、前記Al合金膜が、Niおよび/またはCoを0.15原子%以下(0原子%を含まない)、Geを0.2原子%以上2.0原子%以下、およびLa、Gd、NdおよびYよりなる群から選択される1種以上の元素を0.05原子%以上1.0原子%以下含有し、かつ、前記Al合金膜の表面において観察される腐食孔のアスペクト比(腐食深さ/腐食直径)が0.12以下であることを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】動作速度が低下することを抑制することができる半導体装置を提供する。

【解決手段】半導体装置は、MOSトランジスタ9を有するシリコン基板5と、シリコン基板5上に形成され、配線および絶縁膜により構成された配線層が複数積層された多層配線層と、多層配線層内に埋め込まれた、下部電極(下部電極膜91)、容量絶縁膜92、および上部電極(上部電極膜93)を有しており、メモリ素子を構成する容量素子90と、を備え、容量素子90とMOSトランジスタ9との間にダマシン形状の銅配線(第2層配線25)が少なくとも1層以上形成され、1つの配線(第2層配線25)の上面と容量素子90の下面とが略同一平面上にあり、容量素子90上に銅配線(プレート線配線99)が少なくとも1層以上形成されている。

(もっと読む)

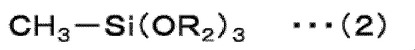

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

エッチング液組成物

【課題】インジウム系金属膜、アルミニウム系金属膜、及びチタニウム系又はモリブデン系金属膜からなる三重膜用エッチング液組成物を提供すること。

【解決手段】本発明のエッチング液組成物は、組成物の総重量に対して、鉄化合物0.1重量%〜10重量%、硝酸0.1重量%〜10重量%、含フッ素化合物0.01重量%〜5重量%、及び水残部を含むことを特徴とする。

(もっと読む)

エッチング液組成物

【課題】インジウム系金属膜、アルミニウム−ランタニウム系合金膜及びチタニウム系金属膜からなる三重膜用エッチング液組成物を提供すること。

【解決手段】本発明のエッチング液組成物は、組成物の総重量に対して、過酸化水素1重量%〜15重量%、無機酸0.1重量%〜10重量%、含フッ素化合物0.01重量%〜5重量%、及び水残部を含むことを特徴とする、

(もっと読む)

相互接続用自己整合バリアおよびキャッピング層

集積回路に使用する銅線のための集積回路用相互接続構造およびこれを作る方法が提供される。Mn、Cr、またはV含有層が、線からの銅の拡散に対しバリアを形成し、それにより、絶縁体の早期絶縁破壊を防ぎ、銅によるトランジスタの劣化を保護する。また、Mn、Cr、またはV含有層は、銅と絶縁体の間の強い接着を促進し、その結果、製造と使用中のデバイスの機械的健全性を保ち、さらに、デバイスの使用中の銅のエレクトロマイグレーションによる故障を防ぎ、また、環境からの酸素または水による銅の腐食を防ぐ。このような集積回路の形成に関しては、本発明の特定の実施形態により、Mn、Cr、V、またはCoを銅表面上に選択的に堆積させ、一方で、絶縁体表面上のMn、Cr、V、またはCoの堆積を減らす、または防ぎさえもする方法が提供される。また、Mn、Cr、またはV含有前駆物質およびヨウ素または臭素含有前駆物質を使った銅の触媒堆積も提供される。 (もっと読む)

塗布型シリカ系被膜形成用組成物、この塗布型シリカ系被膜形成用組成物を用いたシリカ系被膜、及びそれを用いた半導体装置

【課題】 シリカ系被膜樹脂が、高濃度でも保管安定性に優れ、得られるシリカ系被膜の機械強度が高く、基材との密着力が確保し易いシリカ系被膜形成用組成物を提供する。

【解決手段】 (A)下記一般式(1)及び(2)にて表されるアルコキシシラン、

【化1】

【化2】

[R1、R2は炭素数1〜3の有機基を示し、同一でも異なっていてもよい。]

(B)非プロトン性有機溶媒、(C)炭素数3〜6の一価のアルコール、(D)酸触媒とを、必須成分とし、前記(C)成分の添加質量が、前記(A)成分の加水分解・重縮合反応を経て得られるシリカ樹脂質量の2〜3倍である、塗布型シリカ系被膜形成用組成物。

(もっと読む)

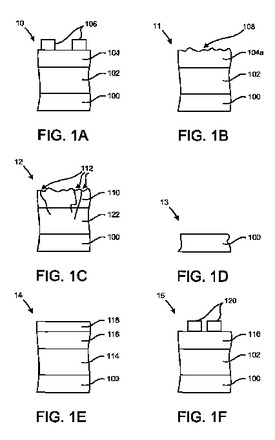

有機珪素化合物とヒドロキシル形成化合物との反応による液状シリカ層の形成

【課題】サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層、浅いトレンチ分離誘電体層等として使用するための低誘電率を有する酸化珪素層を均一に堆積するための方法と装置とを提供する。

【解決手段】約400℃未満の基板温度での有機珪素化合物とヒドロキシル形成化合物との反応によって低比誘電体率を有する酸化珪素層を堆積する。これらの低誘電率薄膜は、残留炭素を含んでおり、サブミクロン素子におけるギャップ充填層、プリメタル誘電体層、インターメタル誘電体層および浅いトレンチ分離誘電体層のために有用である。堆積に先立って水あるいは有機化合物からヒドロキシル化合物を調製することができる。酸化珪素層は、約3.0未満の誘電率を有するギャップ充填層を与えるために有機珪素化合物から生成されたライナー層の上に約40℃未満の基板温度で堆積されることが好ましい。

(もっと読む)

基板上のシリコン含有反射防止コーティング層の再加工方法

半導体デバイス製造においてシリコン含有反射防止コーティング(SiARC)層を有する膜構造を再加工する方法が供される。当該方法は、上にSiARC層を有する膜積層体を含む基板、及び、前記SiARC層上に形成されるレジストパターンを供する工程を有する。当該方法はさらに、前記SiARC層から前記レジストパターンを除去する工程、前記SiARC層を、オゾン(O3)気体を含む処理気体に曝露することで、前記SiARC層を改質する工程、希釈フッ化水素(DHF)液体によって前記の改質されたSiARC層を処理する工程、及び、遠心力により、前記基板から前記の改質されたSiARC層を除去する工程を有する。  (もっと読む)

(もっと読む)

回路基板の貫通電極の形成方法

【課題】基板上の微細な貫通孔へ貫通電極となる金属を充填する方法であって、基板への熱的影響を軽減することができ、且つ、効率的な製造を可能とする方法を提供する。

【解決手段】本発明は、貫通孔を有する基板の貫通孔に導電性金属を充填する貫通電極の形成方法であって、所定の純度及び粒径の金属粉と有機溶剤とからなる金属ペーストを用いるものである。このとき、金属ペーストに周波数60Hz〜100kHzの機械的振動を印加しながら基板に塗布し、金属ペーストの塗布と同時、又は、金属ペーストの塗布後に貫通孔を他端側から減圧して金属ペーストを貫通孔内に吸引し、その後金属ペーストを焼結して貫通電極とする。この金属ペーストの塗布は、機械的振動が印加されたブレードを基板と非接触な状態で移動させることが好ましい。

(もっと読む)

薄膜トランジスタ

【課題】信頼性が高く、耐酸化性に優れる薄膜トランジスタを提供すること。

【解決手段】基板2上に、ゲート電極3、ゲート絶縁層4、半導体層5、ソース電極6およびドレイン電極7を形成してなる薄膜トランジスタであって、アルカリ可溶性フェノール樹脂(A)と感放射線化合物(B)とを含有する感放射線性樹脂組成物からなる保護膜8が、前記ゲート絶縁層4、前記半導体層5、前記ソース電極お6よび前記ドレイン電極7に接触して形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

電極コンタクト構造、自己走査型発光素子アレイ

【課題】オーミック接触を実現する電極コンタクト構造を提供する。

【解決手段】電極コンタクト構造は、エピタキシャル層100と、エピタキシャル層100上に形成されたコンタクトメタル電極120と、コンタクトホールを有する層間絶縁膜140と、コンタクトメタル電極120上に形成された第1のAl配線160と、第1のAl配線160上に形成された拡散障壁層180と、拡散障壁層180上に形成された第2のAl配線200を有する。電極コンタクト構造は、自己走査型発光素子アレイのカソード電極やゲート電極の構造として用いられる。

(もっと読む)

銅薄膜製造方法および銅薄膜

【課題】 金属の微粒子の分散体を用いて絶縁基板上に低体積抵抗率の導電層を得ることができる、金属薄膜の形成方法を提供する。

【解決手段】 銅粒子表面のCu(I)とCu(II)の比が100対0〜30対70モル比の範囲にある銅粒子の分散体からなる塗膜に過熱水蒸気による加熱処理を施す工程を含む、銅薄膜の製造方法およびこの方法で製造された銅薄膜。前記塗膜は銅粒子分散体を絶縁性基板に塗布または印刷されたものであることが好ましい。

(もっと読む)

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

半導体装置

【課題】同一の半導体基板上に容量素子を備えたメモリ回路部と論理回路部を有する半導体集積回路装置において、論理回路部のみからなる半導体集積回路装置と完全互換の配線設計パラメーターを確保し、かつ微細化が進んでもセル容量を確保する。

【解決手段】容量素子を備えたメモリ回路部と論理回路部を同一の半導体基板上に有する半導体集積回路装置において、論理回路部に形成される多層配線を絶縁分離する層間絶縁膜の少なくとも複数の配線層にまたがる領域に該容量素子を埋め込むことで、該容量素子の接続に必要な配線をすべて論理回路部の多層配線で構成することにより、論理回路部の設計パラメーターを、該メモリ回路部を有しない半導体集積回路装置と完全に同一とする。また多層配線の複数層に渡るように該容量素子を配置させることで該容量素子の高さを確保し、スケーリングが進んでも必要な容量値を確保する。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたBa酸化物及びSr酸化物の少なくとも一方を含有するCu合金下地層を有し、該Cu合金下地層と絶縁膜1との界面にBaSi酸化物及びSrSi酸化物の少なくとも一方が偏析している。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

121 - 140 / 735

[ Back to top ]