Fターム[5F033WW04]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 濃度 (735)

Fターム[5F033WW04]に分類される特許

141 - 160 / 735

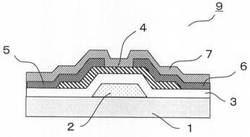

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、半導体層と例えばソース電極やドレイン電極を構成するAl系膜とを安定して直接接続させることが可能であるとともに、ウェットプロセスで用いる電解質液中で、半導体層とAl系膜との間でガルバニック腐食が生じにくく、Al系膜の剥離を抑制することのできる配線構造を提供する。

【解決手段】基板1の上に、基板1側から順に、薄膜トランジスタの半導体層4と、半導体層4と直接接続するAl合金膜6と、を備えた配線構造であって、半導体層4は酸化物半導体からなり、Al合金膜6は、Niおよび/またはCoを含む。

(もっと読む)

配線構造およびその製造方法、並びに配線構造を備えた表示装置

【課題】基板側から順に、Al合金膜と、当該Al合金膜と直接接続する薄膜トランジスタの酸化物半導体層と、を有し、TiやMoなどの高融点金属を省略してAl合金膜を酸化物半導体層と直接接続しても低コンタクト抵抗を実現できる新規な表示装置用Al合金膜を有する配線構造を提供する。

【解決手段】上記配線構造において、半導体層は酸化物半導体からなり、Al合金膜は、Niおよび/またはCoを含むものである。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたCa酸化物を含有するCu合金下地層4aを有し、該Cu合金下地層4aと絶縁膜1との界面にCaSi酸化物が偏析している。

(もっと読む)

多孔質膜の前駆体組成物、多孔質膜及びその作製方法、並びに半導体装置

【課題】多孔質層間絶縁膜作製の際の多層化工程数を削減することができる前駆体組成物、この前駆体組成物を用いて得られた多孔質膜及びその作製方法、並びにこの多孔質膜を利用した半導体装置の提供。

【解決手段】式:Si(OR1)4の化合物(A)及び式:Ra(Si)(OR2)4−aの化合物(B)(上記式中、R1は1価の有機基を表し、Rは水素原子、又は1価の有機基を表し、R2は1価の有機基を表し、aは1〜3の整数であり、R、R1及びR2は同一であっても異なっていてもよい。)から選ばれた少なくとも1種の化合物と、250℃以上で熱分解する熱分解性有機化合物(D)と、90〜200℃の温度範囲内で熱分解し、そしてこの熱分解によりアミン類を発生する化合物であって、この熱分解温度以下では、この化合物の水溶液又はこの水溶液とアルコールとの混合溶液のpHが6.5〜8の範囲内に入る化合物(E)を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1上に複数のロジック用pチャネル型MISFETQp1と、複数のロジック用nチャネル型MISFETQn1と、複数のメモリ用pチャネル型MISFETQp2と、複数のメモリ用nチャネル型MISFETQn2とが混載されている。複数のロジック用pチャネル型MISFETQp1のうちの少なくとも一部は、シリコンゲルマニウムで構成されたソース・ドレイン領域を有し、複数のロジック用nチャネル型MISFETQn1の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。複数のメモリ用pチャネル型MISFETQp2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有し、複数のメモリ用nチャネル型MISFETQn2の全ては、それぞれシリコンで構成されたソース・ドレイン領域を有している。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

反射電極、および反射電極を備えた表示デバイス

【課題】高い反射率および低い接触抵抗を有しており、しかも、ヒロックなどの欠陥を生じることのない耐熱性にも優れた反射電極を提供する。

【解決手段】基板1上に形成される表示デバイス用の反射電極2であって、前記反射電極は、0.05〜2原子%のNi及び/又はCo、並びに0.1〜2原子%のNdを含有する第1のAl−(Ni/Co)−Nd合金層2aとAlとO(酸素)を含有する第2のAl酸化物層2bと、を有している。上記Al酸化物層は透明画素電極3と直接接続しており、前記Al酸化物層中のO原子数とAl原子数との比である[O]/[Al]が、0.30以下であり、前記Al酸化物層の最も薄い部分の厚みが、10nm以下である。上記反射電極は、前記Al酸化物層と前記透明画素電極とが直接接続する領域において、前記透明画素電極と前記基板との間に形成されている。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3〜1.2原子%、Ni:0.1〜1.0原子%未満、Laおよび/またはNd:0.1原子%〜1.0 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を示し、且つ、表示装置の製造過程における現像液耐食性や剥離液耐食性も高められた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、グループAに属するNiおよび/またはCoの元素を0.5原子%以下(0原子%を含まない。)と、Geを0.2〜2.0原子%と、グループBに属するYおよび/またはZrの元素を3原子%以下(0原子%を含まない。)とを含有する。

(もっと読む)

ポロゲン、ポロゲン化された前駆体及び低誘電率をもつ多孔質有機シリカガラス膜を得るためにそれらを使用する方法

【課題】低い誘電率及び改良された機械的性質、熱的安定性及び化学的耐性を有する多孔質有機シリカガラス膜を提供する。

【解決手段】式SivOwCxHyFz(ここで、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、及びzは0〜15原子%)で表わされる多孔質有機シリカガラス膜を製造する。オルガノシラン及びオルガノシロキサンからなる群より選ばれる前駆体並びにポロゲンを含むガス状試薬を真空チャンバに導入し、ガス状試薬にエネルギーを加え、ガス状試薬の反応を生じさせて基体上に予備的な膜を堆積させる。その予備的な膜は細孔を持ち、誘電率が2.6未満である多孔質膜を得るために、実質的にすべてのポロゲンを除去される。

(もっと読む)

窒化銅膜の形成方法

【課題】最終的に得られる製造コストが高く且つ基板の大きさが制限される、従来のプラズマ処理による窒化銅膜の形成方法の課題を解消する。

【解決手段】窒素ガスとアンモニアガスとから成り、アンモニアガス濃度が0.8vol%以上の混合雰囲気内に設けられたヒータブロック18上に載置した基板10を、ヒータブロック18によって蟻酸銅の熱分解温度以上に加熱し、基板10の加熱温度で蒸発する溶媒中に蟻酸銅を溶解した原料供給槽22に貯留した蟻酸銅溶液を、基板10の所定面に向けて噴霧して、噴霧した蟻酸銅溶液中の溶媒を蒸発し且つ蟻酸銅を熱分解して、基板10の所定面に窒化銅膜を形成する。

(もっと読む)

ウェットエッチング方法

【課題】作業効率がよく、エッチングされる基板の材料の選択範囲も大きい、ウェットエッチング方法を提供する。

【解決手段】パターニングされたクロム層2及びレジスト層3を表面に有するガラス基板1をエッチング液4に浸しウェットエッチングする。その際、アルミニウム又は鉄からなる金属棒6がタンク5内のエッチング液4に浸され、所望のタイミングで、クロム層2の露出面2aと金属棒6の端部とが接触される。金属棒6と接触されたクロム層2は電気化学反応等により徐々にエッチングされ小さくなり、ガラス基板1のエッチング液4にさらされる部分が徐々に増え、その部分がウェットエッチングされる。これによりガラス基板1のアンダーカット形状が調節され、ガラス基板1にテーパ面7が形成される。ガラス基板1としては、例えば、石英、白板ガラス、青板ガラス、ホウケイ酸ガラス、無アルカリガラス、又は鉛ガラス等が適用可能である。

(もっと読む)

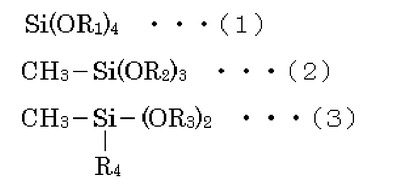

塗布型シリカ系被膜形成用組成物、この塗布型シリカ系被膜形成用組成物を用いたシリカ系被膜、及びそれを用いた半導体装置

【課題】 ゾル−ゲル法を用いて、硬化時の収縮率が小さく低誘電率である塗布型シリカ系被膜を得ることが可能な、塗布型シリカ系被膜形成用組成物を提供することを目的とする。

【解決手段】 下記一般式(1)、(2)及び(3)にて表される化合物を含む(A)成分を必須成分とし、200〜300℃での一段目硬化から、600℃の二段目硬化迄の膜収縮率が5%以下であり、二段目硬化温度が400℃の場合の、シリカ系被膜の比誘電率が2.5以下である、前記(A)成分の加水分解・重縮合反応を経て得られる塗布型シリカ系被膜形成用組成物。

[R1、R2、R3は炭素数1〜3の有機基を示し、同一でも異なっていてもよい。R4は炭素数6〜20の直鎖状アルキル基を示す。]

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】LDMOSFETを有する半導体装置では、ソース電極が裏面にあることから、表面のソース・コンタクト領域と裏面のソース電極間の電気抵抗を低減するため、上面からP型エピタキシャル層を貫通してP+型基板内に伸びるボロンを高濃度にドープしたポリ・シリコン埋め込みプラグが設けられている。このポリ・シリコン埋め込みプラグの周辺のシリコン単結晶領域に転位が発生しており、これにより、リーク不良が誘発されていることが明らかとなった。

【解決手段】本願発明は、相互に不純物濃度の異なる第1及び第2の半導体層の境界面を貫通するシリコン系プラグを有する半導体装置であって、このプラグの少なくとも内部は多結晶領域であり、この多結晶領域表面の内、先の境界面の両側近傍は、固相エピタキシャル領域で覆われている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線抵抗の増加を抑えつつ、配線のエレクトロマイグレーション寿命、およびストレスマイグレーション寿命を向上させる。

【解決手段】半導体装置100は、基板102上に形成された層間絶縁膜104に形成された凹部に、高融点金属を含むバリアメタル膜106と、配線金属膜114を構成する銅および銅とは異なる不純物金属を含むシード合金膜ならびに銅を主成分として含むめっき金属膜とを形成し、シード合金膜およびめっき金属膜を、200℃以上、10分以下で熱処理する第1の熱処理工程と、第1の熱処理工程の後、凹部外部に露出しためっき金属膜、シード合金膜、およびバリアメタル膜106を除去する工程と、シード合金膜およびめっき金属膜を熱処理する第2の熱処理工程と、を含む。

(もっと読む)

半導体デバイスおよびその構造体の製造方法

【課題】集積回路の配線間に空隙を形成することにより、容量成分が低減された半導体装置の製造方法を提供する。

【解決手段】基板202上に第1の絶縁材が堆積され、この上に、犠牲部分を有する第2の絶縁材232が堆積される。上記第1および第2の絶縁層内に、導電線210がダマシン法により形成される。犠牲部分となる第1の絶縁材を除去するために第2の絶縁材が処理され開口部238が形成される。そして第1の絶縁材が除去されて、導電線間に空隙242が形成される。第2の絶縁材は、堆積時には不透過性であるが、処理後により透過性とし、これを介して犠牲部分を除去する。第2の絶縁材の処理はエッチングによる開口、あるいは熱感受性成分のアニールによる除去である。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線絶縁膜としてSiOCH膜を用いる場合に、ビアホールの開口径に依らず、その加工制御性を十分に得て、下層Cu配線の表面の組成のバラツキを十分に抑制する。

【解決手段】下層Cu配線3上に形成されている積層構造20は、シリコンと炭素を含有するキャップ絶縁膜4と、キャップ絶縁膜4上に形成されている配線絶縁膜5としてのSiOCH膜を有する。積層構造20にビアホール8、9を形成する工程は、第1及び第2ドライエッチングを組み合わせて行う。第1ドライエッチングでは開口径が小さいビアホール9のエッチングレートが、開口径が大きいビアホール8のエッチングレートよりも大きくなるようにO2濃度が設定された第1混合ガスを用いる。第2ドライエッチングではビアホール8のエッチングレートがビアホール9のエッチングレートよりも大きくなるようにO2濃度が設定された第2混合ガスを用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】実効誘電率を低減させて、高速かつ消費電力の低い半導体装置を実現する。

【解決手段】本発明の半導体装置は、基板と、基板上に形成された層間絶縁膜51、52と、層間絶縁膜51、52に埋め込まれたCu配線1と、Cu配線1上に形成された第二のバリア絶縁膜4と、を有する。第二のバリア絶縁膜4は、炭素二重結合、アモルファスカーボン構造及び窒素を含む有機シリカ膜である。

(もっと読む)

141 - 160 / 735

[ Back to top ]