Fターム[5F033WW05]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 圧力 (290)

Fターム[5F033WW05]に分類される特許

41 - 60 / 290

ビシクロヘプタジエンの安定化

【課題】ビシクロ[2.2.1]ヘプタ−2,5−ジエンを安定化する方法を提供する。

【解決手段】安定化剤として、キノン類、およびニトロオキサイド類を添加した安定化されたビシクロ[2.2.1]ヘプタ−2,5−ジエン組成物、およびこれの使用。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

疎水性多孔質SOG膜の作製方法

【課題】疎水性機能を損なうことなく、かつ比誘電率への影響が小さく、機械的特性の向上を可能とする疎水性多孔質SOG膜の作製方法の提供。

【解決手段】SOG膜の熱処理を酸素含有ガスの存在下で行って疎水性多孔質SOG膜を作製する。この熱処理を、そのプロセスの所定の時期に導入した酸素分圧5E+3Pa以上の酸素含有ガス中で、300℃〜1000℃の温度で行う。

(もっと読む)

絶縁体インク、絶縁被覆層の作製方法及び半導体装置

【課題】印刷法により基板表面の任意部分に平坦な絶縁被覆層を形成可能な絶縁体インクを提供する。

【解決手段】回路加工した基板に印刷する絶縁体インクにおいて、熱硬化性樹脂及び高分子量成分を含む絶縁樹脂組成物と、25℃における蒸気圧が4.0×102Pa以上、1.34×103Pa未満の溶剤と、を含有する絶縁体インク。

(もっと読む)

自己組織化単分子膜形成方法、ならびに半導体素子の銅配線およびその形成方法

【課題】 ボイド(void)およびシーム(seam)の発生を防止することができる自己組織化単分子膜形成方法、ならびに半導体素子の銅配線およびその形成方法を提供する。

【解決手段】 半導体素子の銅配線形成方法は、半導体基板の上に配線形成領域を有する層間絶縁膜を形成する工程と、前記配線形成領域表面を含む層間絶縁膜上に自己組織化単分子膜(Self Assembled Monolayer)を形成する工程と、前記自己組織化単分子膜の表面に触媒粒子を吸着させる工程と、前記触媒粒子が吸着された自己組織化単分子膜上に無電解メッキ法で銅シード膜を形成する工程と、前記銅シード膜上に前記配線形成領域を埋め立てるように銅膜を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】プラズマ雰囲気の周囲に存在する銅による影響を抑制する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上方に絶縁膜18〜21を形成する工程と、絶縁膜18〜21上にレジスト膜24を形成する工程と、レジスト膜24の上方にマスク膜25を形成する工程と、マスク膜25の上方にレジストパターン27を形成する工程と、レジストパターン27をマスクにしてマスク膜25をエッチングする工程と、酸素ガスとハイドロフロロカーボンガスの混合ガスを導入し、30mTorr以上の圧力の雰囲気内で、マスク膜25から露出する領域のレジスト膜24をエッチングする工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】多孔質絶縁膜を疎水化する半導体装置の製造方法を提供する。

【解決手段】基板3に多孔質絶縁膜2を形成する工程(S101)と、多孔質絶縁膜2が形成された基板3をチャンバー1内に配置する工程(S102)と、基板3が配置されたチャンバー1内にシロキサンを投入するとともに基板3を第一の温度に昇温する工程(S103)と、投入されたシロキサンが付着した基板3を第一の温度よりも高い第二の温度に昇温する工程(S104)と、を含む。S103では、チャンバー1内の圧力を1kPa以下とする。また、第一の温度は、チャンバー1内の圧力がシロキサンの飽和蒸気圧となる温度以上であり、かつ、多孔質絶縁膜2とシロキサンとが重合反応を開始する温度以下である。

(もっと読む)

半導体装置及びその製造方法

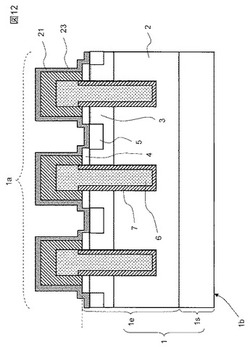

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

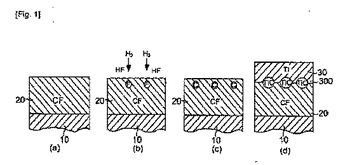

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

Cu膜の成膜方法および記憶媒体

【課題】平滑で高品質のCVD−Cu膜を下地に対して高い密着性をもって成膜することができるCu膜の成膜方法を提供すること。

【解決手段】チャンバー1内にCVD−Ru膜を有するウエハWを収容し、チャンバー1内に、成膜中に発生する副生成物であるCu(hfac)2の蒸気圧がその蒸気圧よりも低いCu錯体であるCu(hfac)TMVSからなる成膜原料を気相状態で導入して、ウエハWに形成されたCVD−Ru膜上にCVD−Cu膜を成膜するにあたり、チャンバー1内の圧力をCVD−Ru膜表面に吸着したCu(hfac)2の脱離および拡散が進行する圧力に制御する。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上とホール内に形成したカーボンナノチューブを絶縁膜に損傷を与えることなく絶縁膜上から除去すること。

【解決手段】配線15a上方に絶縁膜17、18を形成し、絶縁膜17、18をパターニングして配線15aに達するホール17aを形成し、ホール17a内と絶縁膜17、18上面にカーボンナノチューブ22を形成し、カーボンナノチューブ22の層の上に第2絶縁膜23を形成し、第2絶縁膜23をエッチングすることによりカーボンナノチューブ22を露出するとともに、カーボンナノチューブ22の層の凹部に第2絶縁膜23を残し、カーボンナノチューブ22をエッチングしてカーボンナノチューブ22の上端の位置を揃え、さらにカーボンナノチューブ22上の第2絶縁膜23をエッチングし、カーボンナノチューブ22をエッチングして絶縁膜17上面から除去するとともにホール17a内に残す工程を含む。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ステップカバレジを向上させることができ、これによりスループットも高く維持することが可能な成膜方法及びプラズマ成膜装置を提供する。

【解決手段】真空排気が可能になされた処理容器22内へ凹部6を有する絶縁層4が表面に形成された被処理体Wを収容すると共に前記処理容器内へ原料ガスを供給してプラズマCVD法により前記被処理体に対してチタンを含む薄膜を形成する成膜方法において、前記薄膜の形成時の前記処理容器内のプロセス圧力を230〜630Paの範囲内に設定する。これにより、ステップカバレジを向上させることができ、スループットも高く維持することが可能となる。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】全体としてのコンタクト抵抗を小さく維持しつつバリヤ性の高い薄膜の成膜方法及びプラズマ処理装置を提供する。

【解決手段】凹部6を有する絶縁層4が表面に形成された被処理体Wに対して薄膜を形成する成膜方法において、前記凹部内の表面を含む前記被処理体の表面にプラズマCVD法を用いて窒化チタン膜10の薄膜を形成する薄膜形成工程と、窒化ガスの存在下でプラズマを用いた窒化処理を行うことにより前記薄膜を窒化する窒化工程と、を有することを特徴とする成膜方法である。これにより、抵抗を小さく維持しつつバリヤ性の高い薄膜を形成する。

(もっと読む)

基板処理方法及び記憶媒体

【課題】ホールの上面形状を整えて線条痕をなくすと共に、ボトム形状に歪みがなく、しかもボーイング形状の発生を防止して良好な垂直加工形状のホールを処理対象層に形成することができる基板処理方法を提供する。

【解決手段】処理ガスとしてCF4ガス、CHF3ガス及びC4F8ガスを含有する混合ガスを用い、処理圧力100mTorr(1.33×10Pa)〜150mTorr(2.0×10Pa)で中間層としてのBARC膜53をエッチングし、次いで、処理ガスとしてCOSガス含有ガスを用いて下層レジスト層としてのACL52をエッチングし、その後、処理ガスとしてC6F6ガス含有ガスを用いて処理対象層としての酸化膜51をエッチングする。

(もっと読む)

半導体配線の製造方法

【課題】例えばULSI(超大規模集積回路)等に代表されるSi半導体デバイス等の半導体装置において、高性能(低電気抵抗率)かつ高信頼性(高EM耐性)を示すCu系配線を提供する。

【解決手段】半導体基板上の絶縁膜に設けられた凹部にCu−Ti合金が直接埋め込まれてなる半導体装置のCu系配線の製造方法であって、前記Cu−Ti合金が、Tiを0.5原子%以上3.0原子%以下含むものであり、かつ、前記Cu−Ti合金をスパッタリング法で形成し、該Cu−Ti合金を前記凹部に埋め込む時または埋め込み後に、該Cu−Ti合金を下記加熱条件で加熱する工程を含むことを特徴とする半導体装置のCu系配線の製造方法。

(加熱条件)

加熱温度:350〜600℃

加熱時間:10〜120min.

室温から上記加熱温度までの昇温速度:10℃/min.以上

加熱雰囲気における酸素分圧:1×10−7〜1×10−4atm

(もっと読む)

半導体装置及びその製造方法

【課題】幅の狭い溝状領域への層間絶縁膜の形成にポリシラザンを用いた場合のシリコン酸化膜への改質が良好に行われる半導体装置及びその製造方法を提供する。

【解決手段】上面及び側面をキャップ絶縁膜107及びサイドウォール絶縁膜108で覆われた複数のビット線106間に形成された溝状領域109と、N(窒素)よりもO(酸素)を多く含み溝状領域109の内表面を連続的に覆うSiON膜10と、SiON膜10を介して溝状領域109内に埋め込まれ、ポリシラザンを改質することによって形成されたシリコン酸化膜11とを備える。

(もっと読む)

フッ化炭素膜の表面処理

半導体デバイスの製造方法は、絶縁性層をアニーリングする工程と、金属元素を含んだ障壁層を前記絶縁性層上に形成する工程とを含んでいる。前記絶縁性層は、フッ化炭素(CFx)膜を含んでいる。前記障壁層は、前記アニーリング工程後に、高温スパッタリングプロセスによって形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

コバルト膜の形成方法

【課題】コバルト前駆体の使用効率の高い、化学気相成長方法によるコバルト膜の形成方法を提供すること。

【解決手段】上記コバルト膜の形成方法は、基体上にコバルト膜を形成する方法であって、少なくとも(A)一酸化炭素を含む気体の存在下でコバルトカルボニル錯体を昇華する工程と(B)基体上にコバルトカルボニル錯体の昇華物を供給してコバルトに変換する工程とを含むことを特徴とする方法である。

(もっと読む)

高圧ベベルエッチング処理

半導体基板が半導体基板支持部上に支持されたベベルエッチング装置内において、プラズマによる半導体基板のベベルエッジエッチングを行う際にアーク放電を防止する方法は、3〜100Torrの圧力までベベルエッチング装置を排気した状態で、ウェーハにおいて見られるRF電圧を、アーク放電が回避される十分に低い値に維持しつつ、ベベルエッチング装置においてプラズマによる半導体基板のベベルエッジエッチングを行うステップを備える。 (もっと読む)

41 - 60 / 290

[ Back to top ]