Fターム[5F044MM03]の内容

Fターム[5F044MM03]に分類される特許

161 - 180 / 350

半導体装置用テープキャリアの製造方法

【課題】 配線パターンのパターン間隔が広い部分と狭い部分とでの、サイドエッチングの進行の速さのばらつきを抑えつつ、オーバーエッチングを行って、配線パターンのさらなる微細化を、精度よく安定的に実現する。

【解決手段】 絶縁性材料からなるフィルム基板1上に形成された銅層2(金属材料層)の表面に、レジストパターン6を形成する工程と、レジストパターン6をマスクとして用いたエッチングプロセスにより銅層2を加工して疎密のパターン間隔19が混在する配線パターン7を形成する工程とを含む半導体装置用テープキャリアの製造方法であって、レジストパターン6における各位置ごとでのエッチング代(しろ)11の寸法を、配線パターン7のパターン間隔が広いほど、大きい寸法に設定する。

(もっと読む)

COF用配線基板とその製造方法、並びに半導体装置

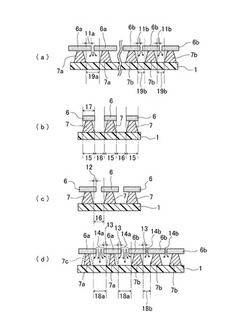

【課題】高い放熱性を有するCOF用配線基板を提供する。

【解決手段】絶縁フィルム1の片側の面に、搭載される半導体素子7の表面に設けられた電極パッドと接合するためのインナーリード11と、COFを搭載する外部基板の端子と接合するためのアウターリード12とを有する配線13が設けられたCOF用配線基板の、半導体チップ7が搭載される予定の領域14内で、インナーリード11が存在しない部分に、放熱板15が配置されている。

(もっと読む)

半導体装置用テープキャリアの製造方法および半導体装置用テープキャリアの製造装置

【課題】 ウィスカの発生や不純物付着に起因した電気的短絡の発生を抑止して、さらに高い信頼性を備えた半導体装置用テープキャリアを製造することができる半導体装置用テープキャリアの製造方法および半導体装置用テープキャリアの製造装置を提供する。

【解決手段】 ロールツーロール法により半導体装置用テープキャリアをインラインで製造する、半導体装置用テープキャリアの製造方法であって、テープキャリア1に、Snめっき層14を無電解Snめっきにより形成した後、炉内温度を150℃以上〜200℃以下の範囲内のうちの所定の温度に制御したインライン熱処理炉11内にて、10秒〜5分間の範囲内のうちの所定の時間に亘って、熱処理を行う工程を含んでいる。

(もっと読む)

半導体装置用テープキャリアの製造方法

【課題】 配線パターンで覆われておらず露出している部分のフィルム基材のポリイミド表面に、部分的な剥れやシワが散発的に発生することを防いで、配線パターン間の耐マイグレーション性を確保する。また、工程管理の煩雑化を解消する。

【解決手段】 ポリイミド樹脂からなるフィルム基材1上にシード層2を形成してなる基板の表面に配線パターン6を形成する工程と、前記配線パターン6の表面にめっき層7を形成する工程とを有する半導体装置用テープキャリアの製造方法であって、前記配線パターン6を形成した後、当該配線パターン6で覆われておらず露出している部分の前記ポリイミド樹脂からなるフィルム基材1のポリイミド表面にプラズマドライエッチング表面処理を施す工程を含んでいる。

(もっと読む)

半導体装置

【課題】異物の移動を抑え、高感度でプリント配線上の導電性異物を検出することができ、半導体装置出荷後の不良率の増大を抑えることが可能な半導体装置を提供する。

【解決手段】半導体チップと、この半導体チップが載置される基板12と、この基板12上に形成され、一端が半導体チップと接続され、他端が外部配線と接続されるための複数の配線13と、それぞれ基板12上に配線13と並列に配置され、隣接する複数の配線13と電気的に分離された複数の副配線15を備える。

(もっと読む)

TAB用テープキャリアの製造方法

【課題】工程数の増加および材料の無駄を抑制しつつソルダレジストのスクリーン印刷を高い精度で行うことが可能なTAB用テープキャリアの製造方法を提供することである。

【解決手段】TAB用テープキャリア1上の各印刷ブロック13の両側方に位置決めマークPM1,PM2が形成される。スクリーン印刷時に、ロール・トゥー・ロール方式により長尺状回路基板10が搬送される。光学センサが位置決めマークPM1を検出したときに、長尺状回路基板10の搬送を停止する。その後、スクリーン印刷装置100により長尺状回路基板10の印刷ブロック13にソルダレジストのスクリーン印刷が行われる。

(もっと読む)

テープキャリア及び半導体装置の製造方法、半導体装置

【課題】外観上の不具合及び曲げる際の不具合の両方を改善できるようにしたテープキャリア及び半導体装置の製造方法、半導体装置を提供する。

【解決手段】製品領域を画定するカットライン51に沿って切断されることによって個々の製品に分割されるテープキャリア100であって、絶縁性のベースフィルム1と、IC素子を取り付けるための取付領域53からその外側へ延びるようにベースフィルム1上に設けられたリード3と、リード3を覆うようにベースフィルム1上に設けられたソルダーレジスト5と、を備え、ソルダーレジスト5は製品領域の内側から外側へはみ出している。

(もっと読む)

テープ配線基板および半導体装置ならびにそれらの製造方法

【課題】半導体チップと外部基板との実装方向の制約がなく、かつ狭ピッチの半導体チップとの接合を可能にするテープ配線基板を提供する。

【解決手段】可撓性の絶縁性基材2aと、絶縁性基材2a上に形成された導体配線4aとを備える。導体配線4aの断面形状が三角形である部分5aと四角形である部分6aとを有し、導体配線4aの断面形状が三角形である部分5aには、導体配線4aの半導体チップが実装可能に形成された部分3に形成されたインナーリード部が含まれる。

(もっと読む)

半導体装置用テープキャリア及び半導体装置用テープキャリアの製造方法

【課題】吸湿や加熱による配線パターンの寸法変化を抑制し、ICなどの半導体装置の実装時の不具合を低減できる半導体装置用テープキャリアを提供する。

【解決手段】絶縁性フィルム(3)上に外部接続端子部(6a,6b)を有する配線パターン(6)が形成された半導体装置用テープキャリア(1)において、前記配線パターン(6)が形成された前記絶縁性フィルム(3)面上にあって、前記配線パターン(6)の外周部に、前記配線パターン(6)と同一金属からなる変形防止用パターン(8A)が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】実装時の位置ズレを無くし、30μmピッチ程度の微細接続が安定してできるような製造方法を提供する。これにより、ICの小型化に伴うコストダウンにより安価な装置を実現する。

【解決手段】フィルム1基板に金属薄膜を形成し、フィルム基板に含まれる水分の量を0.1Wt%以下にして絶乾させた後、金属薄膜をパターニングして配線を形成し、配線が形成されたフィルム基板を一定の温湿度の環境下に一定時間以上放置した後、ICチップ3に設けられたバンプを配線にフェイスダウンで接合する。又は、フィルム基板に金属薄膜を形成し、フィルムを一定の温湿度の環境下に一定時間以上放置して調湿した後、金属薄膜をパターニングして配線を形成し、配線が形成されたフィルム基板を一定の温湿度の環境下に一定時間以上放置した後、ICチップに設けられたバンプを前記配線にフェイスダウンで接合する。

(もっと読む)

電子部品搭載用基材の製造方法及び電子部品搭載用基材

【課題】金属箔からなる配線パターン上に形成しためっき層のウイスカ発生を防止する電子部品搭載用基材の製造方法を提供する。

【解決手段】樹脂フィルム1上に並設された配線パターン芯体2aの各表面にめっき層22aを形成する被膜形成ステップと、めっき層22aを形成直後から常温で保持した場合と比べて、めっき層22aにおける内部応力の増加が少なくなる温度域でめっき層22aを保持し、めっき層22aを改質する改質ステップと、改質が行われためっき層22aの一部を覆うようにソルダーレジスト3を形成するソルダーレジスト形成ステップとを有する。

(もっと読む)

フレキシブル配線基材並びに半導体装置及びその製造方法

【課題】現行の接合条件を変更せずに、信頼性あるファインピッチILBを確立できるフレキシブル配線基材並びに半導体装置及びその製造方法を提供する。

【解決手段】絶縁基材11と、絶縁基材11の一方面に形成された銅を含む導電体層をパターニングした配線パターンと、配線パターンの端子部を除く表面を被覆するソルダーレジスト層17とを具備し、配線パターンの端子部は、配線ベース層21上にスズめっき層26を施したものであり且つ各端子のピッチが20μmより大きく30μmより小さいフレキシブル配線基材において、端子部の配線ベース層21上のスズめっき層26は、スズめっき層26中に配線ベース層21の銅が拡散した拡散層26aと純スズ層26bとからなり、総厚が0.26μm〜0.5μmの範囲であり、純スズ層の厚さが0.08μm〜0.18μmであり且つ総厚をtとしたときの(0.53−0.846t)μmの値を超えない範囲にある。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】半導体パッケージ(例えば、COFパッケージ)において、ベースフィルムの歪みによる封止樹脂の未充填不良を防止する。

【解決手段】COFパッケージは、フレキシブルなベースフィルム20と、このベースフィルム20上における半導体チップ搭載予定箇所21の周縁に配置され、半導体チップ搭載予定箇所内へ突設された金属製の厚さd1の複数のインナリード22と、半導体チップ搭載予定箇所内の所定の位置に配設された金属製の厚さd2(<(d1+d3)、但し、d3;バンプ電極の厚さ)のダミーパターン26と、半導体チップ30と、封止樹脂32とを備えている。半導体チップ30は、主表面に突設された厚さd3の複数のバンプ電極31を有し、このバンプ電極31がインナリード22に接合されている。更に、封止樹脂32は、半導体チップ搭載予定箇所21と半導体チップ主表面との間に充填されている。

(もっと読む)

電子部品搭載用基材とその製造方法

【課題】リード部材が樹脂フィルムに接着されてなる電子部品搭載用基材において、リード部材における表面をスズなどの金属層で覆うときに、銅などの溶解が発生することを抑制するとともに、リード部材が樹脂フィルムから剥離することのない電子部品搭載用基材とその製造方法を提供する。

【解決手段】金属からなる本体部分21の表面領域の一部に、当該本体部分21を構成する金属元素と同種の金属元素を含む合金層22が存在するリード部材2が、前記合金層22が存在しない表面領域で樹脂フィルム1に接着されてなる電子部品搭載用基材100とする。

(もっと読む)

チップオンフィルム

【課題】高寸法安定性と共に適度な弾性率を有し、更に優れた易滑性と折り曲げ性を有する自動光学検査システム(AOI)に適応可能なチップオンフィルムを提供する。

【解決手段】ポリイミドフィルム1の少なくとも片面に、ICチップが搭載可能なように配線2を形成してなるチップオンフィルムであって、ポリイミドフィルム1が、ジアミン成分としてPPD及びODAを、酸二無水物成分としてピロメリット酸二無水物及びBPDAを用いて主として構成されてなるものであり、かつ、ポリイミドフィルム1中に、粒子径0.01〜1.5μmで平均粒子径0.05〜0.7μmであって、かつ、粒子径0.15〜0.60μmの粒子が全粒子中80体積%以上の割合を占める粒度分布を有する無機粒子が、フィルム樹脂重量当たり0.1〜0.9重量%の割合で分散・含有させたものである。

(もっと読む)

半導体装置用テープキャリアの製造方法

【課題】 超微細配線パターンを有するLCD用TABテープのような半導体装置用テープキャリアを、材料資源的および時間的な無駄を削減して、安定的に(確実かつ迅速に)製造することが可能な製造方法を提供する。

【解決手段】 この製造方法は、絶縁性フィルム基板1上に形成された銅層2上にドライフィルムレジストを貼着してレジスト膜6を形成する工程と、前記レジスト膜6を露光・現像して、配線パターン形成用の配線レジストパターン7を形成すると共に、前記ドライフィルムレジストの解像限界のパターン寸法を有する検査用レジストパターン8を形成する工程と、前記検査用レジストパターン8を用いて前記配線レジストパターン7の解像度検査を行う工程と、前記配線レジストパターン7をパターン形成用レジストとして用いて配線パターン13を形成する工程とを含んでいる。

(もっと読む)

COFキャリアテープ、COFキャリアテープの製造方法、およびCOF型半導体装置の製造方法

【課題】長尺な絶縁フィルムテープ上に配線パターンが、長さ方向に繰り返し形成されるCOFキャリアテープにあって、配線パターンの間隔をなくすか減少するかして、最終的に長尺な絶縁フィルムテープから配線パターンごとに打ち抜いて半導体装置が製造されるとき、絶縁フィルムテープの長さの有効率を高めて無駄をなくし、コストの低減を図る。

【解決手段】長尺な絶縁フィルムテープ1上に、配線パターン3が、長さ方向に繰り返し形成されており、半導体チップ搭載後に、搬送ローラなどを用いて長さ方向に所定搬送長さ搬送されて順次位置決めされ、配線パターンごとに打ち抜かれる。そのようなCOFキャリアテープ12において、打ち抜き時に同様に搬送ローラなどを用いて所定搬送長さ搬送されたとき、例えば光学式のパターン認識装置により認識される認識パターン4が、所定搬送長さごとに、打ち抜き領域外に形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線パターンにおけるエレクトロマイグレーションの発生を抑制できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】ポリイミド等からなるフィルム1上に形成され、その表面がメッキ層で覆われているインナーリード2の接合位置にICチップ20のバンプ22を重ね合わせて接合する際に、インナーリード2の表面を覆うメッキ層5を接合時の熱で溶融し、溶融したメッキをインナーリード2の(フィルム1から剥がれた)先端部2aの剥離面へ回り込ませる。これにより、先端部2aの剥離面にもメッキ層が形成される。

(もっと読む)

電子部品搭載用基材とその製造方法

【課題】銅の過剰溶解を効果的に回避しつつ、スズメッキ処理に係る製造コストの低減と製造効率の向上を図ることが可能な電子部品搭載用基材とその製造方法を提供する。

【解決手段】電子部品搭載用基材1において、リード本体20に複合メッキ層23を積層するとともに、これを部分的に覆うようにソルダーレジスト層30を形成する。複合メッキ層23を構成するスズ銅合金メッキ層21とスズメッキ層22を、一度のメッキ処理で形成された前駆スズメッキ層21Xを加熱処理することで形成する。これにより、ソルダーレジスト層30の形成後のメッキ処理を省略し、製造効率を向上させ、リード本体20の銅の過剰溶解を回避する。

(もっと読む)

半導体パッケージに用いられるテープ及びそのカット方法

【課題】半導体パッケージに用いられるテープ及びそのカット方法を提供する。

【解決手段】複数の分断領域を有する基材10と、基材10上の各分断領域に形成されたリード線1、及び相応のリード線1に連結する細線2と、を備える半導体パッケージに用いられるテープに関し、少なくとも1つの分断領域において、細線2がリード線1の中心線11から離れているオフセット細線配列構造を有する。

(もっと読む)

161 - 180 / 350

[ Back to top ]