Fターム[5F044RR18]の内容

ボンディング (23,044) | ワイヤレスボンディング関連事項 (2,154) | 容器・封止 (1,675) | 封止構造 (460)

Fターム[5F044RR18]に分類される特許

21 - 40 / 460

電子部品及び電子部品の製造方法

【課題】半導体装置及び配線基板の接続信頼性がより向上した電子部品等を提供する。

【解決手段】本発明に係る電子部品は、第1基板と、前記第1基板の第1の面に位置する電極と、前記第1基板の前記第1の面に形成される第1樹脂突起と、前記第1基板の前記第1の面に形成される第2樹脂突起と、前記電極と接続し、前記第1樹脂突起の少なくとも一部を覆う第1の部分と、前記第2樹脂突起の少なくとも一部を覆う第2の部分と、を有する第1配線と、第2基板と、前記第2基板の第2の面に位置する第2配線と、前記第2基板の前記第2配線と接する突起電極であって、前記第1の部分および前記第2の部分と接する前記突起電極と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】配線を設計通りの形状に形成することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板と、前記半導体基板の第1の面に位置する電極と、前記第1の面に設けられ、前記電極とオーバーラップする位置に開口部を有する絶縁膜と、を有する構造体を用意する工程と、前記絶縁膜の前記第1の面側の面とは反対側の第2の面に、樹脂突起を形成する工程と、前記電極および前記樹脂突起を覆う第1導電膜を前記第2の面に形成する工程と、前記第1導電膜の前記第2の面側の面とは反対側の第3の面に、前記第1導電膜の前記第3の面より反射率の低い第2導電膜を形成する工程と、前記第2導電膜の前記第3の面側の面とは反対側の第4の面に、フォトレジスト層を形成する工程と、前記フォトレジスト層の一部をマスク層で覆った状態で、前記フォトレジスト層を露光する工程と、前記フォトレジスト層を現像し、フォトレジストパターンを形成する工程と、前記フォトレジストパターンをマスクとして前記第1導電膜および前記第2導電膜をエッチングすることにより、前記第1導電膜から形成された配線であって、前記樹脂突起の少なくとも一部を覆い、かつ、前記電極と接続する前記配線を形成する工程と、を有する。

(もっと読む)

電子部品実装基板、及び、電子部品実装基板の製造方法

【課題】電子部品実装基板の小型化・薄型化に伴い発生しうる、部品同士がアンダーフィル樹脂を介して接着固定し、部品の取り外しに不具合が生じる問題を抑制すること。

【解決手段】メイン基板10と、メイン基板10上に搭載される電子部品30及び50と、メイン基板10と電子部品30との間に充填されるアンダーフィル樹脂40と、電子部品30の上面及び側面を、電子部品30との間に隙間を有した状態で覆う被覆部材20とを有し、被覆部材20の内面の少なくとも一部には、当該面よりもアンダーフィル樹脂40との密着力が弱い離型膜60が形成されている電子部品実装基板。

(もっと読む)

電子部品およびその製造方法

【課題】機械的強度および対候性に優れた電子部品およびその製造方法を提供する。

【解決手段】電子部品の製造方法は、複数の電気素子11を準備する工程と、複数の電気素子11をそれぞれ実装する複数の基板20の集合体である基体20Aを準備する工程と、基体20A上に樹脂21を形成する工程(図1(e))と、複数の電気素子11を樹脂21に押圧することにより、複数の電気素子11の側面の一部を樹脂21に接合する工程と、複数の電気素子11に研磨処理を施して複数の電気素子11を薄化する工程と、基体20Aを分割することにより、複数の基板20を個片化する工程とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、半導体チップがフリップチップ接続される配線基板と、半導体チップと配線基板との間を封止するアンダーフィル樹脂とを備えた半導体装置の製造方法に関し、ボイドの発生を防いで、半導体装置の歩留まりを向上させることのできる半導体装置の製造方法を提供することを課題とする。

【解決手段】基板本体21の上面21Aに、基板本体21の上面21A、パッド22、及びはんだ23との間に隙間が形成されないように半硬化状態とされたフィルム状アンダーフィル樹脂31を真空雰囲気下において、ダイアフラム式ラミネート装置を用いて貼り付け、その後、フィルム状アンダーフィル樹脂31に半導体チップ12を押圧して、パッド22に半導体チップ12をフリップチップ接続した。

(もっと読む)

電子部品、及びその製造方法

【課題】機能部を有する機能性素子が配線基板上に搭載されるとともに、少なくとも配線基板と機能素子との接合部を保護するための封止層が設けられている電子部品において、封止層の機能部への侵入を防止し、当該機能部が動作できるような空間を、電子部品のサイズを大型化させることなく形成する。

【解決方法】配線基板の主面上において、機能性素子の機能部と対向する領域に撥水層を形成し、封止層を形成する際のその構成樹脂が、配線基板の主面と機能性素子の機能部との間に流入するのを抑制して、これらの間に前記機能部が動作できるための空間を形成するようにして、電子部品を構成する。

(もっと読む)

接続構造体の製造方法及び塗布装置

【課題】第1,第2の接続対象部材の電極間の位置ずれを抑制できる接続構造体の製造方法を提供する。

【解決手段】接続構造体1の製造方法は、電極2bを上面2aに有する第1の接続対象部材2上に、ディスペンサー12を移動させながら、異方性導電ペーストをディスペンサーから塗布して、異方性導電ペースト層を形成する工程と、異方性導電ペースト層上に、電極4bを下面4aに有する第2の接続対象部材4を積層する工程と、異方性導電ペースト層を加熱して本硬化させて、硬化物層3を形成する工程とを備える。塗布方向と直交する方向における異方性導電ペースト層の中央部に対して、塗布方向と直交する方向における異方性導電ペースト層の中央部の外側の縁部が盛り上がった形状になるように、異方性導電ペーストを塗布する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体素子とテープ基材との間のすき間に対して、未充填や気泡等の不具合を生じさせることなく適切に充填剤を充填させることができる半導体装置およびその製造方法を提供すること。

【解決手段】半導体装置100は、テープ基材102と、配線パターン104と、配線パターン104と電気的に接続された半導体素子108と、テープ基材102の表面を覆い、且つ半導体素子108との対向領域に表面側開口部106aを有する表面側絶縁保護膜106と、テープ基材102の裏面を覆い、且つ表面側開口部106aの裏側となる部分に裏面側開口部112aを有する裏面側絶縁保護膜112とを備える。表面側絶縁保護膜106は、前記対向領域よりも外側に突出している突出開口部106bを有する。裏面側開口部112aは、テープ基材102の表面における半導体素子108との対向領域の1.00〜8.50倍の大きさを有する。

(もっと読む)

保護層形成用フィルム

【課題】 半導体装置の製造の際の工程数の増加を抑制しつつ、半導体ウエハが有する低誘電材料層のクラックを防止することを可能とする保護層形成用フィルムを提供すること。

【解決手段】 低誘電材料層が形成されているバンプ付きウエハに保護層を形成するための保護層形成用フィルムであって、支持基材と粘着剤層と熱硬化性樹脂層とがこの順で積層されており、熱硬化性樹脂層の溶融粘度が、1×102Pa・S以上2×104Pa・S未満となり、且つ、粘着剤層のせん断弾性率が、1×103Pa以上2×106Pa以下となる温度が50〜120℃の温度範囲内に存在する保護層形成用フィルム。

(もっと読む)

ICタグ

【課題】製造コストの高騰を招くことがなく、ICチップの破損を防止できるICタグを提供する。

【解決手段】回路基材11と、前記回路基材11の回路電極にフリップチップ方式により接合材を用いて実装されたICチップ13と、前記回路基材11の回路面に設けられた保護層311とを備えたICタグ1であって、前記ICチップ13の周縁には、前記接合材の硬化体からなるフィレットが形成され、前記フィレットは、前記ICチップ13を補強する補強部を備え、前記補強部は、前記ICチップ13の側面を被覆するとともに、前記側面に沿った高さ寸法と前記ICチップ13の高さ寸法とが略等しくされた状態が、前記ICチップ13の実装面に沿った方向に所定寸法延長された形状に形成され、前記保護層311は、ウレタン系オリゴマーと、エネルギー線硬化性モノマーとを含んで構成されている。

(もっと読む)

積層半導体チップ、半導体装置およびこれらの製造方法

【課題】積層半導体チップ、半導体装置およびこれらの製造方法を提供する。

【解決手段】積層半導体チップは、第1チップと、第1チップ上に積層された第2チップと、第1チップの上部面と第2チップの下部面との間に形成された導電性バンプと、第1チップと第2チップとの間に介在し、導電性バンプを封止し、第2チップの側壁に沿って形成され、第2チップの上部面に隣接して形成された上部面を有するアンダーフィル物質と、第1チップの上部面上のアンダーフィル物質の外側面上に配置され、第2チップとアンダーフィル物質を含む断面において、アンダーフィル物質によって第2チップの側壁から離隔され、第2チップの側壁と接しないモールディング材と、を含む。

(もっと読む)

電子部品の製造方法

【課題】電子部品同士を半田接合し、半田接合部の空隙を熱硬化性樹脂を含有する樹脂層で充填させ、半田接合部を補強する電子部品の製造方法において、空洞(エアギャップ)の発生を抑制することができ、さらに、ボイド(気泡)の発生をも抑制することができる、電子部品の製造方法および電子部品を提供する。

【解決手段】第1電子部品1または第2電子部品3の少なくとも一方に、熱硬化性樹脂を含有する樹脂層5を形成する第1の工程と、第1接続用金属電極2と第2接続用金属電極4を当接させる第2の工程と、両接続用金属電極を半田接合させる第3の工程と、を有する電子部品の製造方法において、第3の工程において、板状体を有する加圧装置で加圧を維持しながら前記半田接合に用いる半田の融点以上の温度に加熱し、さらに、前記半田接合に用いる半田の融点以上の温度で加圧を開放する。

(もっと読む)

接続構造体

【課題】第1,第2の接続対象部材の接続信頼性が高く、かつ電極間の導通信頼性が高い接続構造体を提供する。

【解決手段】本発明に係る接続構造体1は、電極2bを上面2aに有する第1の接続対象部材2と、電極4bを下面4aに有する第2の接続対象部材4と、第1の接続対象部材2の上面2aと第2の接続対象部材4の下面4bとの間に配置されており、かつ接着剤を硬化させることにより形成された硬化物層3とを備える。第2の接続対象部材4の外周側面よりも側方の少なくとも一部の領域に、硬化物層3によるフィレットが形成されている。硬化物層3は、第1の接続対象部2材側に第1の硬化物層部分3aと、第2の接続対象部材4側に第2の硬化物層部分3bとを有する。第1の硬化物層部分3aの25℃での弾性率は、第2の硬化物層部分3bの25℃での弾性率よりも高い。

(もっと読む)

半導体装置

【課題】半導体チップ周囲のアンダーフィルのフィレット形状をより均一な形状に近づけることで、半導体チップと基板との接続信頼性が高い半導体装置を得ること。

【解決手段】半導体チップ2が、アンダーフィル4を介在させて基板1にフリップチップ実装された半導体装置100であって、前記基板1の前記半導体チップ2が搭載されている領域の周囲に、前記アンダーフィル4のフィレット5形状を規制するフィレット形状規制部6が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体チップと外部基板を接合する接合樹脂による接合応力を均一化し、半導体チップのトランジスタ特性変動が生じない半導体装置を提供する。

【解決手段】フリップチップ組立において、半導体チップ1と外部基板13の間に接合樹脂17を注入して接合させる際、本接合樹脂を2種類にわけ、半導体チップ1の中心部分には低応力接合樹脂23、周辺部分には高応力接合樹脂21を注入したり、半導体チップ1の中心部分にはSiN等をはじめとした第1層表面保護膜とポリイミドやPBO等をはじめとした第2層表面保護膜の2層構造、周辺部分にはSiN等をはじめとした第1層表面保護膜の1層構造とすることにより、半導体チップ1内のトランジスタ特性変動を抑制する。

(もっと読む)

電子装置

【課題】 チップ部品および配線基板の接続不良を抑制することが可能な電子装置を提供すること。

【解決手段】 電子素子22および電子素子22が第1主面21Aに搭載された基板21を有するチップ部品2と、チップ部品2が第1主面21Aを対向させた状態で搭載される配線基板3と、チップ部品2の表面から配線基板3の表面にかけて設けられ、電子素子22を封止する封止空間Sを取り囲む樹脂層4とを備え、樹脂層4は、封止空間Sの側方に位置する部位に、外表面に開口する窪み部5を有している電子装置1である。封止空間Sの側方の樹脂層4は体積が減少するので、チップ部品および配線基板の接合部にかかる繰り返し応力が抑制され、この接合部の接続不良を抑制できる。

(もっと読む)

弾性波デバイス

【課題】信頼性の高い弾性波デバイスを提供すること。

【解決手段】本発明は、絶縁性基板11と、弾性波を励振する振動部22を有し、振動部22が絶縁性基板11と対向し、かつ振動部22が空隙51に露出するように、絶縁性基板11の上面に実装された弾性波デバイスチップ20と、振動部22を囲むように設けられ、絶縁性基板11と弾性波デバイスチップ20とを接合する接合部と、を具備し、接合部は、半田32と、半田32より高い融点を有しかつ絶縁性基板11の上面のコプラナリティより大きな厚さを有する金属層42と、を積層して形成されている弾性波デバイスである。

(もっと読む)

電子装置

【課題】 電気特性の変化を抑制することが可能な電子装置を提供すること。

【解決手段】 電子素子22および電子素子22が第1主面21Aに搭載され、第1主面21Aと対向しており、かつ第1主面21Aに比して平面視での面積が大きい第2主面21Bを有する基板を有するチップ部品2と、チップ部品2が第1主面21Aを第1空間S1を介して対向させた状態で搭載される配線基板31と、基板21の第2主面21Bから配線基板31の表面にかけて設けられる樹脂層4とを備え、基板31と基板31の側方に位置する樹脂層4との間に、第1空間S1に通じる第2空間S2が設けられている電子装置1である。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップ同士を積層する際に生じる曲げモーメントによる破損を防止する半導体装置の製造方法を提供する。

【解決手段】一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重なるように他面に形成された裏面バンプBBを含むコアチップCC1と、一面に形成された表面バンプFB及び積層方向から見て表面バンプFBと重ならないように他面に形成された裏面バンプBBを含むインターフェースチップIFとを準備し、コアチップCC1の裏面バンプBBとインターフェースチップIFの表面バンプFBが接続するように、インターフェースチップIFの裏面バンプBBに対応する位置に凹部GRを有するボンディングツールBTを用いて積層方向に重ね合わせる。これにより、積層時にチップに曲げモーメントが発生しないことからチップの破損を防止することが可能となる。

(もっと読む)

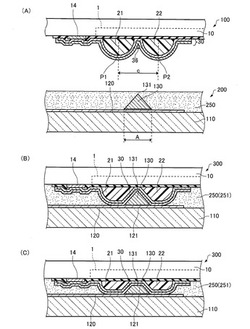

フリップチップ実装構造

【課題】フレキシブル基板に半導体素子をフェイスダウンで実装する半導体装置において、低コストな手段で、小型・薄型構造を妨げずに放熱性を高めるフリップチップ実装構造を提供する。

【解決手段】半導体素子1とフレキシブル基板10とがバンプ2を介して接合され、半導体素子とフレキシブル基板との間が封止樹脂9により封止されたフリップチップ実装構造において、フレキシブル基板には、半導体素子と対抗する面の一部にランド3が形成され、フレキシブル基板は、バンプと接合されることで画定される領域の内側で屈曲し、このときのランドと半導体素子との間隔が、バンプと接合後の半導体素子とランドとの間隔よりも狭小になっている。

(もっと読む)

21 - 40 / 460

[ Back to top ]