Fターム[5F045AB01]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 4族 (3,529)

Fターム[5F045AB01]の下位に属するFターム

Fターム[5F045AB01]に分類される特許

21 - 40 / 241

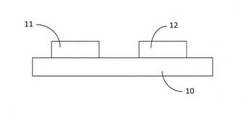

半導体材料の選択堆積方法

【課題】シリコンやゲルマニウムのようなIV族半導体材料を、半導体表面上に、絶縁表面上への堆積無しに選択的に堆積する方法を提供する。

【解決手段】半導体プロセスで半導体材料の選択成長を行う方法が、第1領域11と第2領域12とを含むパターニングされた基板10を提供する工程を含み、第1領域11は露出した第1半導体材料を含み、第2領域12は露出した絶縁材料を含む。この方法は、更に、第2半導体材料の前駆体、Cl化合物とは応性しないキャリアガス、および錫テトラクロライド(SnCl4)を供給することにより、第1領域の第1半導体材料の上に第2半導体材料の膜を選択的に形成する工程を含む。錫テトラクロライドは、第2領域の絶縁材料上への第2半導体材料の堆積を阻害する。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置する第二ステップと、前記基板の結晶面にエピタキシャル層を成長させる第三ステップと、を含む。

(もっと読む)

基板処理装置

【課題】 流体圧作動弁の動作遅延や動作不良を防ぎ、応答速度を均一化させ、基板処理の品質を向上させる。

【解決手段】 基板を処理する処理室内への処理ガスの供給を制御するガス供給ユニットを備える基板処理装置であって、ガス供給ユニットは、上流側が処理ガスの供給源に接続され、下流側が処理室内へ連通するガス導入配管に接続されるガス供給流路と、ガス供給流路上に設けられ、流体配管を介した流体の供給により開閉が制御される流体圧作動弁と、制御信号を受信する信号受信部及び流体配管内に流体を供給する流体出力部を有し、信号受信部が受信した制御信号に基づいて流体配管を介した流体圧作動弁への流体の供給を制御する電磁弁と、少なくともガス供給流路及び流体圧作動弁の外部を気密に囲う気密筐体と、を備え、電磁弁は気密筐体に直接固定されている。

(もっと読む)

UV線を用いたシリコン含有膜の低温エピタキシャル成長

【課題】シリコン含有及び/又はゲルマニウム含有膜の一括的又は選択的エピタキシャル堆積の清浄な基板表面を調製する方法を提供する。更に、シリコン含有及び/又はゲルマニウム含有膜を成長させる方法であって、基板洗浄方法と膜成長方法の双方が750℃未満、典型的には約700℃〜約500℃の温度で行われる前記方法を提供する。

【解決手段】洗浄方法と膜成長方法は、シリコン含有膜が成長している処理容積において波長が約310nm〜約120nmの範囲にある放射線の使用を用いる。反応性洗浄又は膜形成成分化学種の具体的な分圧範囲と組み合わせたこの放射線の使用は、業界で以前に知られている温度より低い温度で基板洗浄とエピタキシャル膜成長を可能にする。

(もっと読む)

窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法

【課題】 窒化物上へゲルマニウム・スペーサを選択的に堆積するための構造及び方法を提供すること。

【解決手段】 半導体製造プロセス中でゲルマニウム構造体を選択的に形成する方法は、化学的酸化物除去(COR)プロセスにおいて自然酸化物を除去し、次いで、加熱された窒化物及び酸化物表面を加熱されたゲルマニウム含有ガスに曝して、ゲルマニウムを選択的に窒化物表面上にだけ形成し、酸化物表面上には形成しない。

(もっと読む)

シリコン含有膜の選択的堆積

【課題】混合基板の選択された領域上に、Si含有膜を選択的に堆積するためのトリシランおよびハロゲン含有エッチャントソース(塩素など)を使用する化学気相成長方法を提供すること。

【解決手段】ドーパントソースは、ドープしたSi含有膜を選択的に堆積させるために、トリシランおよびエッチャントソースと混合することもできる。この選択的堆積方法は、半導体製造などの様々な用途に有用である。

(もっと読む)

半導体材料の選択堆積方法

【課題】第2半導体材料と絶縁材料とを含む基板上に、第1半導体材料を選択的に堆積する方法の提供。

【解決手段】第1半導体材料が第2半導体材料上に選択的に堆積され、この方法は、a)炭素および/またはハロゲン含有ガスから形成されたプラズマを用いて基板を前処理する工程と、b)化学気相堆積により、基板上に第1半導体材料を堆積する工程とを含む。

【効果】特に、半導体デバイス機構の製造のための改良された方法に関する。

(もっと読む)

シリコンゲルマニウムの、平坦化及び欠陥密度を減少させる方法

【課題】半導体デバイス製造の多層プロセスにおいて、劣悪な平坦性は、ホトリソグラフィー工程で問題を惹起し得る。特に初期の堆積ステップにおける劣悪な平坦性は、半導体デバイス製造のより高い層を通じて増幅される傾向がある。この点を改良した半導体デバイス製造工程初期のブランケット層の堆積方法を提供する。

【解決手段】ガス状の前駆体混合物を形成するためにシリコンソース、ゲルマニウムソース及びエッチャントを混合することを含み、SiGe膜30をブランケット堆積する方法。本方法はさらに、化学気相成長条件下において、ガス状の前駆体物質を基板10上に流し、パターンの有無に関わらず、基板10上にエピタキシャルSiGeを堆積させる方法に依り、平坦性の優れたブランケット層30を堆積する。

(もっと読む)

配列化ダイヤモンド膜およびその製造方法

【課題】粒界を避けた素子配置を容易に形成させることにより、実質的に単結晶基板上と同等に高性能の素子を効率的に製造でき、更に粒界に沿って分割することで容易に素子を製造できる、大型の多角形ダイヤモンド結晶粒が配列した高配向ダイヤモンド膜を提供する。

【解決手段】異種材料の結晶基板上に、その結晶方位の情報を引き継いで成長を開始した高配向ダイヤモンド膜であって、表面において、多角形ダイヤモンド結晶粒が、重心間距離が20μm以上の二次元繰り返しパターンで配列していることを特徴とする配列化ダイヤモンド膜。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】Siウエハなどの基板にSi、SiGeなどの半導体膜を選択成長にて成膜する際の、膜形状を平坦化させる。

【解決手段】絶縁体面間に半導体面が露出された第一基板の対向面に絶縁体面が露出された第二基板を配置した状態で反応室内へ搬送する第一工程と、前記反応室内を加熱するとともに前記反応室内へ少なくともシリコン含有ガスと該シリコン含有ガスとは異なる塩素含有ガスとを供給して、少なくとも前記第一基板の半導体面に選択的に平坦な表面を有するシリコン含有膜を形成する第二工程と、を有する。

(もっと読む)

半導体膜の改良された堆積方法

【課題】均一性の高いSi又はSiGeを基板表面上に堆積する方法を提供する。

【解決手段】化学気相成長プロセスにおいて、輸送量制限領域又はその近傍で、薄膜の堆積を行うことを可能にする化学前駆体を利用する。このプロセスによれば、堆積速度が大きく、さらに組成的にも厚み的にも、通常の化学前駆体を用いて調整した膜より均一な膜を生成することができる。好ましい実施の形態では、トリシランを使用して、トランジスタゲート電極などの様々な用途で半導体産業において有用なSi含有薄膜を堆積する。

(もっと読む)

高品質の緩和シリコンゲルマニウム層の製造方法

【課題】半導体材料上のSi1−xGex層の堆積中、パーティクル生成を最小限化する方法を提供する。

【解決手段】Si前駆体と、分解温度がゲルマンより高いGe前駆体とを含む雰囲気中に基板を設けるステップ、および最終Ge含有量が約0.15より大きくかつパーティクル密度が約0.3パーティクル/cm2より小さいSi1−xGex層を前記基板上に堆積するステップを含む。

(もっと読む)

電界効果トランジスタ(FET)およびそれを形成する方法

基板処理装置および半導体装置の製造方法

【課題】誘導加熱方式を使用した基板処理装置を構成する被誘導体の破損を抑制できる技術を提供する。

【解決手段】本発明では、サセプタ218Hの上段にさらに、少なくとも、ダミーサセプタDMY1が配置され、または、サセプタ218Lの下段に、さらに、少なくとも、ダミーサセプタDMY3が配置されている。これらのダミーサセプタDMY1、DMY3には、ウェハ200が搭載されておらず、サセプタ218Hもしくはサセプタ218Lに載置されたウェハ200を加熱する。

(もっと読む)

フィン型FETを有する半導体装置およびその製造方法

【課題】横方向延伸を減少し、素子サイズを小さくすることができる半導体装置を提供する。

【解決手段】半導体基板上に延伸し、STI領域を間に有する第1および第2のフィンを形成する。STI領域の上面と第1および第2のフィンの上面の間の寸法を第1の高さとし、STI領域の第1と第2のフィンとの間の間隙内に誘電材料を堆積し、STI領域の上面上に上面を有して、誘電材料の上面と第1および第2のフィンの上面との寸法を第2の高さとし、第2の高さは、第1の高さより低くなるように誘電材料を堆積した後、第1および第2のフィン上でそれぞれ誘電体の上方に、第1および第2のフィン延伸をエピタキシャル成長で形成する。

(もっと読む)

半導体膜の製造方法および半導体膜の製造装置

【課題】大面積の良質な半導体膜を安定して簡便に作製することが可能な半導体膜の製造方法を得ること。

【解決手段】前記カソード電極上に堆積した半導体膜を前記カソード電極を加熱することにより加熱する工程と、前記加熱された半導体膜中から離脱した脱離水素原子量を前記カソード電極の温度に応じて複数回測定する工程と、前記脱離水素原子量の測定結果を分析して前記半導体膜の膜質を反映させて製膜条件を調整するための指標となる膜質情報を取得する工程と、前記膜質情報に基づいて前記半導体膜の製膜条件を第2の製膜条件に再設定する工程とを含む。

(もっと読む)

基板処理装置

【課題】ガス配管同士を接続するフランジ部に於いて、該フランジ部を加熱するヒータの寿命の延長を図ると共に、前記フランジ部を効率よく加熱可能な基板処理装置を提供する。

【解決手段】基板を収納し処理する反応管と、該反応管内に処理ガスを供給するガス供給管、前記反応管内の雰囲気を排気するガス排気管等のガス配管を具備し、該ガス配管同士は端部に形成されたフランジ部44a,46aを介してクランパ3によって接続され、該フランジ部に連続する直管部44,46にヒータ94を設けると共に前記フランジ部にもヒータ93,95を設け、前記フランジ部及び前記直管部を覆う断熱材92を設けた。

(もっと読む)

半導体基板、電子デバイス及び半導体基板の製造方法

【課題】シリコン基板上の一部の領域に形成する3族窒化物半導体の結晶性を高める製造方法を提供する。

【解決手段】表面がシリコン結晶であるベース基板102と、シリコン結晶上の一部の領域に形成されたSixGe1−xC(0≦x<1)エピタキシャル結晶104と、SixGe1−xC(0≦x<1)エピタキシャル結晶104上に形成された3族窒化物半導体結晶106とを含む半導体基板100を提供する。一例として、当該半導体基板100は、シリコン結晶上に形成され、かつ、シリコン結晶を露出する開口110を有し、結晶の成長を阻害する阻害体108をさらに含み、SixGe1−xC(0≦x<1)エピタキシャル結晶104は、開口110の内部に形成されている。

(もっと読む)

エピタキシャル堆積層を有するシリコンから構成される半導体ウェハの製造方法

【課題】チャンバーエッチに付随する欠点を、付随する利点をなくさないで、且つ、新しい欠点を受け容れないで、緩和する。

【解決手段】エピタキシャル堆積層を有するシリコンから構成される半導体ウェハの製造方法であって、エピタキシー反応器のサセプタ上にダミーウェハを設置すること; 該エピタキシー反応器を通してエッチングガスを導き、エッチングガスの作用によって該エピタキシー反応器内表面上の残留物を除去すること; 該エピタキシー反応器を通して第一の堆積ガスを導き、該エピタキシー反応器内表面上にシリコンを堆積させること; ダミーウェハをシリコンから構成される基板ウェハと交換すること; および該エピタキシー反応器を通して第二の堆積ガスを導き、該基板ウェハ上にエピタキシャル層を堆積させることを含む方法によって解決される。

(もっと読む)

CMOSデバイス用シリコンウェハの製造方法

【課題】 同じ特性のn−MOSトランジスタとp−MOSトランジスタとを有し、n−MOSトランジスタに最適な応力による歪特性をもたらすSiGe膜と、p−MOSトランジスタに最適な応力による歪特性をもたらすSiC膜とを同一シリコン基材上に備えた、小さいサイズのトランジスタに対しても、最適な特性を持つCMOSデバイス用のシリコンウェハの製造方法の提供。

【解決手段】 CMOSデバイス用シリコンウェハの製造方法において、同一シリコン基材の表面に、選択エピタキシャル法又はイオン注入法を用い、SiGe膜及びSiC膜を分離して形成し、CMOSデバイスを構成するために必要なn−MOSデバイス、及びp−MOSデバイスを同一シリコン基材上に島状に分離して製造する。

(もっと読む)

21 - 40 / 241

[ Back to top ]