Fターム[5F048BB05]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 多結晶Si (4,558)

Fターム[5F048BB05]の下位に属するFターム

N型ドープ多結晶Si (1,205)

P型ドープ多結晶Si (956)

Fターム[5F048BB05]に分類される特許

201 - 220 / 2,397

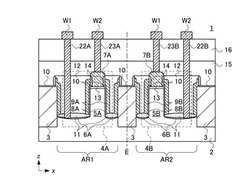

半導体装置

【課題】バイアス切替の前後でドレイン電流の大きさが変化しない縦型トランジスタを実現する。

【解決手段】半導体装置1は、第1の下部拡散層6A、第1の上部拡散層7A、及び第1のゲート電極9Aを有する第1の縦型トランジスタ4Aと、第2の下部拡散層6B、第2の上部拡散層7B、及び第2のゲート電極9Bを有する第2の縦型トランジスタ4Bと、第1及び第2のゲート電極9A,9Bに接続されるゲート配線と、第1の下部拡散層6A及び第2の上部拡散層7Bに接続される第1の配線W1と、第1の上部拡散層7A及び第2の下部拡散層6Bに接続される第2の配線W2とを備える。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1,第2のゲート電極の実効ゲート長が短くなることを防止する。

【解決手段】第1のMISトランジスタnTr1は、第1のゲート電極18aにおけるゲート幅方向の側面上に形成された第1のオフセットサイドウォール22aと、第1のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第1のオフセットサイドウォールを介して形成された第2のオフセットサイドウォール24aと、第1のエクステンション領域26aとを備えている。第2のMISトランジスタnTr2は、第2のゲート電極18bにおけるゲート長方向の側面及びゲート幅方向の側面上に形成された第3のオフセットサイドウォール22bと、第2のゲート電極におけるゲート長方向の側面及びゲート幅方向の側面上に第3のオフセットサイドウォールを介して形成された第4のオフセットサイドウォール24bと、第2のエクステンション領域23bとを備えている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】 ダイオードとトランジスタとを直列接続した半導体メモリにおいて、ダイオードからトランジスタにキャリアが入ることで、トランジスタの特性が劣化する課題がある。

【解決手段】 半導体記憶装置において、ダイオード(PD)中のキャリアを生成するダイオード半導体層(40p)と、トランジスタのチャネル層(8p)との間に、当該キャリアを対消滅させる構造(61pと62p等)を有する。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】平坦なNiPtシリサイド層を形成する。

【解決手段】CVD法を用いて、シリコン層26(ゲート),29(ソース・ドレイン)上にPt層を形成する。次いで、CVD法を用いて、Pt層上にNi層を、Pt層より厚く形成する。次いで、シリコン層26,29、Pt層、及びNi層を熱処理することにより、NiPtシリサイド33を形成する。Pt層の平均膜厚が0.5nm以上2nm以下であるのが好ましい。またシリコン層は、例えばMISFETのソース・ドレインである。

(もっと読む)

半導体集積回路装置の製造方法

【課題】素子特性の安定性を向上できる半導体集積回路装置の製造方法を提供する。

【解決手段】半導体集積回路装置の製造方法は、シリコン基板101の表面に第1の酸化膜103を形成する工程と、周辺回路領域A2内にあるシリコン基板101の所定箇所に不純物を注入し、この所定箇所上の第1の酸化膜103を除去し、この所定箇所上に第2の酸化膜112を形成する工程と、メモリセル領域A1内の第1の酸化膜103にトンネルウィンドウを形成し、このトンネルウィンドウ内で露出したシリコン基板101上にトンネル酸化膜116を形成し、トンネル酸化膜116を覆うメモリセル用ポリシリコン膜118を形成する工程と、第2の酸化膜112を形成する前記工程の後にメモリセル用ポリシリコン膜118上にONO膜119を形成する工程とを有する。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

SOI基板の作製方法

【課題】貼り合わせ不良を十分に低減できるSOI基板を提供する。

【解決手段】半導体基板に絶縁層を形成し、絶縁層が形成された半導体基板にイオンを照射することにより脆化領域を形成し、ベース基板を加熱することで、ベース基板表面に付着した水分量を低減し、加熱されたベース基板と、脆化領域が形成された半導体基板と、を対向して接触させることにより貼り合わせ、貼り合わされたベース基板と半導体基板とを加熱して、脆化領域において分離させることにより、ベース基板上に半導体層を形成するSOI基板の作製方法。これにより、貼り合わせ不良を十分に低減できるSOI基板を提供することができる。

(もっと読む)

半導体素子

【課題】ゲート閾値の変動を抑制または防止できる半導体素子を提供する。

【解決手段】半導体素子1は、n型エピタキシャル層8と、n型エピタキシャル層8の表層部に形成されたボディ領域12と、ボディ領域12の表層部に形成されたn型ソース領域16と、n型エピタキシャル層8上に形成されたゲート絶縁膜19と、ゲート絶縁膜19上に形成されたゲート電極20およびゲート保護ダイオード30とを含む。ゲート保護ダイオード30は、第1のp型領域31とn型領域32と第2のp型領域33とを含む。第1のp型領域31とn型領域32によって第1のダイオード30Aが構成されている。n型領域32と第2のp型領域33によって第2のダイオード30Bが構成されている。第1のp型領域31はゲート電極20に接続されている。第2のp型領域33はソース電極27を介してソース電極27に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】超高速アニールプロセスにおける加熱応力によるウェハ破壊の頻度を抑圧することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法であって、補助加熱されている半導体基板の補助加熱されている裏面とは反対側の表面に0.1m秒以上100m秒以下のパルス幅を有するフラッシュランプ光を照射し、その照射エネルギーによって熱処理する工程を、前記半導体基板の補助加熱されている裏面の面積をWS、該面と接触するサセプタと該面との接触面積をCSとすると、気圧値Pが

0.01−0.005(CS/WS)≦P≦0.4−0.2(CS/WS)(kgf/cm2)

の関係を満たす減圧状態下で実行する。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート絶縁膜にhigh−k膜を使用したMIS構造の半導体装置において、互いに異なる仕事関数を有する複数の同一導電型トランジスタを設けることを可能にする。

【解決手段】同じ導電型の第1のMISトランジスタ及び第2のMISトランジスタが同じ半導体基板50上に設けられている。第1のMISトランジスタにおけるゲート絶縁膜52aの界面層2Aの厚さは、第2のMISトランジスタにおけるゲート絶縁膜52bの界面層2bの厚さよりも厚い。

(もっと読む)

半導体装置の製造方法

【課題】500keV〜3000keVのエネルギーイオン注入を行っても、目的とする領域に精度良く、不純物拡散領域を形成することができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の表面に、イオン注入を行うための開口部42Aを持つレジストパターン42を形成する工程であって、開口部42Aの縁部42Bがイオン注入予定領域50の外縁部50Aよりも内側に位置するようにして、レジストパターン42を形成する工程と、レジストパターン42から露出した半導体基板10の表面の少なくとも一部に対して、ウエットエッチングを施す工程と、レジストパターン42をマスクとし、500keV〜3000keVのエネルギーイオン注入により、半導体基板10の深部に不純物拡散領域(例えばN−型不純物拡散領域12)を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成されたFETのソース側のエクステンション領域の抵抗値を低減し、半導体装置の動作速度を向上することができる技術を提供する。

【解決手段】ゲート電極4dの側壁に、ゲート電極4dのゲート長方向の幅が異なる第1サイドウォール6wおよび第2サイドウォール6nをそれぞれ形成する。これにより、第1サイドウォール6wおよび第2サイドウォール6nの形状によって第1サイドウォール6wおよび第2サイドウォール6nの下部に自己整合的に形成されるエクステンション領域37、38の半導体基板SBの上面の幅をそれぞれ異なる長さで形成する。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極上のキャップ膜が厚く、隣接するトランジスタ間の空間のアスペクト比が大きいトランジスタに、適切な濃度プロファイルを有するハロー領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】一実施の形態による半導体装置の製造方法は、基板上に第1および第2のゲート電極を形成する工程と、前記第1および第2のゲート電極下に第1および第2のハロー領域をそれぞれ形成する工程と、前記第1および第2の絶縁膜に底面および側面をそれぞれ覆われた第1および第2のキャップ膜を形成する工程と、を含む。前記第1のハロー領域は、第1の不純物を、前記第2の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。前記第2のハロー領域は、第2の不純物を、前記第1の絶縁膜を貫通させて前記基板に打ち込むことにより形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜にハフニウムを含む絶縁膜を使用したMISFETを有する半導体装置において、MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】本発明では、nチャネル型コア用トランジスタQ1のゲート絶縁膜と、pチャネル型コア用トランジスタQ2のゲート絶縁膜の構成を相違させている。具体的に、nチャネル型コア用トランジスタQ1では、ゲート絶縁膜に酸化シリコン膜SO1とHfZrSiON膜HK1の積層膜を使用している。一方、pチャネル型コア用トランジスタQ2では、ゲート絶縁膜に酸化シリコン膜SO1とHfSiON膜HK2の積層膜を使用している。

(もっと読む)

半導体装置の製造方法

【課題】 チャネル領域に応力を印加するよう作用する階段状のソース/ドレイン・エピタキシャル領域を、製造プロセスを有意に複雑あるいは冗長とすることなく形成する。

【解決手段】 ゲート電極をマスクとしてドーパントを注入し、半導体基板内にドーパント注入領域を形成する(S2)。サイドウォールの形成(S3)後、ゲート電極及びサイドウォールをマスクとして半導体基板内に第1のリセスを形成する(S4)。このとき、第1のリセスの内壁の一部からドーパント注入領域が露出される。その後、上記ドーパント注入領域を選択エッチングにより除去し、第1のリセスに連通し且つ第1のリセスより浅い第2のリセスを形成する(S5)。それにより、階段状のリセスが形成される。そして、第1のリセス及び第2のリセス内に、チャネル領域へのストレッサとして作用する半導体材料を成長させてソース/ドレイン領域を形成する(S6)。

(もっと読む)

半導体装置の製造方法

【課題】工程数を増加させることなく、高耐圧トランジスタへのイオン注入を的確に実行することを可能にする。

【解決手段】

第1素子形成領域(AA1)のうち、第1トランジスタ(Tr1)のゲート電極が形成されるべき第1領域(R1’)の直上に位置するマスク材(M1)の第1部分(H1’)を除去する一方、第1部分(H1’)以外の第1素子形成領域(AA1)にはマスク材(M1)を残存させる。一方、第2素子形成領域(AA2)のうち、第2トランジスタ(Tr2)のゲート電極が形成されるべき第2領域(R1)の直上に位置するマスク材の少なくとも第2部分(H1)と、第2トランジスタ(Tr1)のソース/ドレイン拡散領域が形成されるべき第3領域(R2、R3)の直上に位置するマスク材の少なくとも第3部分(H2,H3)とを除去してマスク材の開口を形成する。

(もっと読む)

201 - 220 / 2,397

[ Back to top ]