Fターム[5F048BB09]の内容

MOSIC、バイポーラ・MOSIC (97,815) | ゲート (19,021) | 材料 (10,904) | 金属、合金、金属化合物(シリサイドを除く) (1,529)

Fターム[5F048BB09]に分類される特許

21 - 40 / 1,529

半導体装置の製造方法

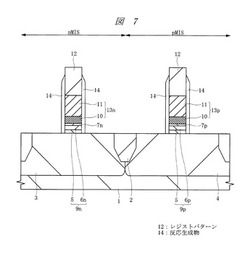

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置

【課題】半導体素子が有する寄生容量や寄生インダクタンスによる電力の損失を抑えるこ

とが出来る、整流回路の提供を課題とする。

【解決手段】入力された交流電圧の振幅に従い、前段の回路と該整流回路の間におけるイ

ンピーダンスを整合または不整合にする。入力される交流電圧が規定の振幅以下である場

合は、インピーダンスを整合にし、該交流電圧をそのまま整流回路に印加する。逆に入力

される交流電圧が規定の振幅よりも大きい場合は、インピーダンスを不整合にし、反射に

より該交流電圧の振幅を小さくしてから整流回路に印加する。

(もっと読む)

半導体装置の製造方法

【課題】第1の領域において、第2の絶縁膜からゲート絶縁膜への酸化剤の侵入を防止する。第2の領域において、複数の第1の配線間に設けられた第2の絶縁膜を第1の絶縁膜に対して選択的に除去する。

【解決手段】半導体装置の製造方法では、基板の第1の領域には第1の積層体を形成し第2の領域には複数の第1の配線を形成する。第1の絶縁膜をマスクとして、第1の領域の主面に第1の不純物のイオン注入を施す。第1の積層体の側壁を覆いかつ複数の第1の配線間を埋設するように第2の絶縁膜を形成する。第2の絶縁膜をマスクとして、第1の領域の主面に第2の不純物のイオン注入を施す。第1のエッチングにより、第2の絶縁膜を第1の絶縁膜に対して選択的に除去した後、基板に熱処理を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

トンネルトランジスタ、トランジスタを含む論理ゲート、論理ゲートを使用するスタティックランダムアクセスメモリ、およびトンネルトランジスタの製造方法

【課題】第1、第2ゲートを有するトンネルトランジスタで、第1、第2のゲート間の電圧の差がより小さい場合にしようできるトンネルトランジスタを提供する。

【解決手段】ドレイン2、ソース4およびドレイン2とソース4との間で電流を制御するための少なくとも第1ゲート6とを含み、第1および第2のゲート誘電体材料7、11の第1側9、13が、それぞれ第1および第2の半導体部分14、15に実質的に沿って、実質的に接続して配置されたトンネルトランジスタ1。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板等にダメージを与えることなくゲート絶縁膜を形成する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に誘電体膜を形成する成膜工程と、前記誘電体膜を熱処理する熱処理工程と、前記誘電体膜上の一部に電極を形成する電極形成工程と、前記電極の形成されていない前記誘電体膜にイオン化したガスクラスターを照射する照射工程と、前記照射工程の後、ウェットエッチングにより、前記イオン化したガスクラスターの照射された領域における前記誘電体膜を除去するエッチング工程と、を有することを特徴とする半導体装置の製造方法を提供することにより上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】金属シリサイド層の異常成長を防止する。

【解決手段】半導体基板1にゲート絶縁膜5、ゲート電極6a,6b、ソース・ドレイン用のn+型半導体領域7bおよびp+型半導体領域8bを形成する。それから、サリサイド技術によりゲート電極6a,6bおよびソース・ドレイン領域上に金属シリサイド層13を形成する。そして、金属シリサイド層13の表面を還元性ガスのプラズマで処理してから、半導体基板1を大気中にさらすことなく、金属シリサイド層13上を含む半導体基板1上に窒化シリコンからなる絶縁膜21をプラズマCVD法で堆積させる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

保護回路、及び半導体装置

【課題】ESDの影響を効果的に抑制する保護回路を提供すること。またESDの影響が効果的に抑制された半導体装置を提供すること。

【解決手段】保護回路は、少なくとも2つの保護ダイオードを有し、当該保護ダイオードを、チャネルを形成する半導体層を挟んで対向する2つのゲートを有するトランジスタで構成する。さらに当該トランジスタのゲートの一方に、固定電位が入力される構成とすればよい。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

CMOS半導体装置の製造方法及びCMOS半導体装置

【課題】マイクロコンタクト印刷の版を凹版として使用し、微細な電気回路と高生産性のCMOS半導体装置の製造方法を提供するものである。

【解決手段】Pチャネル型電界効果トランジスタのPチャネル領域101とNチャネル型電界効果トランジスタのNチャネル領域102とを、凹版601を用いた印刷によって形成するようにし、凹版601が、第1凹部602と第2凹部603とを備え、インクジェット法によって、第1凹部602にP型半導体インク111を供給し、第2凹部603にN型半導体インク112を供給する工程と、インク供給後に、凹版601を被印刷基板001に押しつけて、第1凹部602に供給したP型半導体インク111と第2凹部603に供給したN型半導体インク112とを一括して被印刷基板001に転写する工程と、を含むCMOS半導体装置の製造方法を提供する事により、上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置の形成プロセスを簡略化できるようにする。

【解決手段】半導体基板に形成されたプレーナ型トランジスタと3次元トランジスタを含む半導体装置であり、前記プレーナ型トランジスタ、前記3次元トランジスタはともに高誘電率材料によるゲート絶縁膜を有し、前記プレーナ型トランジスタは、前記ゲート絶縁膜上に、下側が第1のメタル材料(A)、上側が第2のメタル材料(B)からなるゲート電極を有し、前記3次元トランジスタは埋め込みゲート電極を有し、該埋め込みゲート電極の下側のほうに前記第1のメタル材料(A)と同一の材料が、該埋め込みゲート電極の上側のほうに前記第2のメタル材料(B)と同一の材料がそれぞれ使用されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】特性の低下を抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、が含まれている。p型半導体層8に含まれるp型不純物として、少なくとも電子走行層3及び電子供給層5のいずれかを構成する元素と同種の元素が用いられている。

(もっと読む)

窒化物半導体装置

【課題】内蔵する環流ダイオードの順方向電圧が低く、高耐圧で、低オン抵抗の、ノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置は、基板1、第1の窒化物半導体層3、第2の窒化物半導体層4、及び第2の窒化物半導体層上4に設けられた、ソース電極5、ドレイン電極6、第1のゲート電極9、ショットキー電極10、第2のゲート電極12、を備える。第2の窒化物半導体層4と第1の窒化物半導体層3との界面には、2次元電子ガスが形成される。第1のゲート電極9はノーマリオフ型FET20のゲート電極であり、ソース電極5とドレイン電極6との間に設けられる。ショットキー電極10は、第1のゲート電極9とドレイン電極6との間に設けられる。第2のゲート電極12はノーマリオン型FET21のゲート電極であり、ショットキー電極10とドレイン電極6との間に設けられる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

21 - 40 / 1,529

[ Back to top ]