Fターム[5F058BF11]の内容

Fターム[5F058BF11]の下位に属するFターム

スパッタ (401)

蒸着(電子ビーム加熱等を含む) (72)

イオンプレーティング (10)

イオンビーム蒸着 (17)

MBE (19)

Fターム[5F058BF11]に分類される特許

21 - 40 / 44

半導体装置の製造方法及び熱処理装置

【課題】 酸素濃度及びアルゴン濃度が制御され、且つ密閉された雰囲気下で、強誘電体膜の熱処理工程を実施することができる半導体装置の製造方法及び熱処理装置を提供する。

【解決手段】 部材が挿入でき、且つ減圧可能である熱処理室と、熱処理室に設けられた、熱処理室内への気体導入及び気体排気が可能である開口と、熱処理室内における気体の圧力を検出し、圧力に関する検出情報を出力する検出部と、熱処置室内の部材を加熱する加熱部と、開口による熱処理室内の気体排気を可能にする制御と、熱処理室内の密閉、開口による熱処理室内の気体導入、及び加熱部による部材の加熱を検出情報に基づいて行う制御と、を行う制御部と、を有する。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

圧電体材料用としての酸化物、並びに、それを用いた圧電体素子及び半導体装置

【課題】経時変化と共に圧電体特性の劣化、即ち疲労を抑制することが可能な鉛、ジルコニウム、及びチタンを含む酸化物圧電体材料と、それを用いた圧電体素子及び半導体装置を提供する。

【解決手段】圧電体材料PZTにおいて、鉛の一部がランタンにより置換され、且つジルコニウムまたはチタンの一部がリチウム、ベリリウム、マグネシウム及びホウ素のうち少なくとも一種類以上の元素により置換されている元素組成を有する。この圧電体材料は、酸素欠損が発生しても、疲労特性を大幅に改善することが可能である。圧電体素子は、2つの電極13,15間に圧電体14を配置した圧電体素子において、圧電体14が、上記の圧電体材料を含む。キャパシタを有する半導体装置においては、キャパシタの有する誘電体膜及びゲート絶縁膜のうち少なくとも一方が、上記の圧電体材料を含む。

(もっと読む)

酸化膜形成方法、MOSデバイス製造方法、MOSトランジスタ製造方法、SiOx粉末、及びSiOx粉末製造方法

【課題】ゲート絶縁膜としての使用に耐え得るような高品位の酸化膜を窒化物半導体の上に作成する。

【解決手段】本発明による酸化膜形成方法は、SiOx粉末を原料として用いる真空蒸発により、窒化物半導体部材の上にSiOx膜を堆積する工程と、堆積された前記SiOx膜を、酸化雰囲気で紫外線を照射しながら加熱することによって酸化する工程と備えている。原料のSiOx粉末は、下記特性を有している:(1)フーリエ変換赤外分光分析(FTIR:Fourier Transform Infrared Spectroscopy)によって得られた赤外吸収スペクトルにおいて、880cm−1にピークが現れる。(2)ラマン分光分析によって得られたラマンスペクトルにおいて、450〜550cm−1にピークが現れない。(3)X線光電子分光分析(XPS:X-ray photoelectron spectroscopy)によって得られたXPSスペクトルにおいて、SiO2のSi−O結合に対応するピーク(約103eV)とSiの2p軌道のSi−Si結合のピーク(約99eV)とが現れ、且つ、Si−Si結合のピークの高さが、Si−O結合のピークの高さの0.6倍以上である。

(もっと読む)

半導体装置及びコンデンサ

【課題】La2O3の強い吸湿性を改善し、高い耐湿性及び安定性を有する半導体装置及びコンデンサを提供する。

【解決手段】高誘電率絶縁膜12が(La1−xMx)2O3(0<x≦0.3、MはSc、Y、Hf、Ti、Ta、Al、Nbの群から選ばれる1又は2以上の金属)で表記される組成からなることにより、吸湿性が改善し、安定性が向上する。

(もっと読む)

複数のゲート誘電体組成およびゲート誘電体厚を有する集積半導体チップならびにその製造方法

【課題】本発明の目的は、集積回路向けの高品質な高K誘電体を得ることである。

【解決手段】方法は、基板の上に材料を形成するステップと、この材料にパターンを形成して、材料の部分を除去し、その下の基板の部分を露出させるステップとを含む。この方法はさらに、酸化プロセスを実行して、基板の露出した部分の上および材料と基板の間の界面に酸化層を形成するステップを含む。回路は、非クリティカル・デバイスと、この非クリティカル・デバイスの部分として形成された酸化物とを含む。この回路内のクリティカル・デバイスの部分として、基板の上に高K誘電材料が形成される。この高K誘電材料とその下の基板の間に酸化物ベースの界面が提供される。第2の方法は、最初の材料として窒化物または酸窒化物を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁層と、ゲート電極界面において、低誘電率界面層が生成し、絶縁層全体の誘電率を低下させる。さらにシリサイド反応により、しきい値がシフトするという問題を解決する。

【解決手段】

高誘電率ゲート絶縁層103の上の界面において、シリコンの拡散、シリコンとのシリサイド生成反応および低誘電率界面層の生成を起こすことのない、かつSiO2と比して十分高い誘電率をもつLaとAlを含む金属酸化物層である絶縁層1012をバリア層として具備した構造を提供する。

(もっと読む)

デバイスへの酸素および水分の浸透を防ぐ方法、およびその方法により製造されたデバイス

【課題】発光素子(OLED素子)、薄膜センサ、およびエバネッセント導波路センサなどのデバイスの寿命を延ばすために、デバイス中への酸素および水分の浸透を防ぐ。

【解決手段】リン酸スズ低液相線温度無機材料を、デバイスの少なくとも一部分の上に堆積させて、堆積低液相線温度無機材料を形成する(130)。この堆積低液相線温度無機材料を、実質的に酸素と水分を含まない環境中で熱処理して、気密シールを形成する(140)。低液相線温度無機材料を堆積させる工程は、タングステンを含む抵抗加熱素子の使用を含む。

(もっと読む)

選択的周波数UVによる膜の加熱

【課題】酸化又は誘電性薄膜の作成方法を提供する。

【解決手段】基板(例えばシリコン基板)上に形成された層(例えば誘電性層)を、特定の周波数又はエネルギの光子で加熱する。前記特定の周波数又はエネルギは、光子が前記材料を容易に通過して前記材料に吸収され、その後、前記層と前記基板との界面で反射されるように、前記層の材料に応じて選択される。

(もっと読む)

レーザーアブレーションによる機能膜の製造法およびそれに用いるレーザーアブレーション加工用組成物

【課題】低エネルギーで金属を含む機能膜をレーザーアブレーション法により製造する方法と、それに用いる組成物の提供。

【解決手段】基板上101に、金属元素を含んでなる微粒子103と有機分散媒104とを含んでなるレーザーアブレーション加工用組成物を塗布して前記組成物の層102を形成させ、レーザー光を像様に照射して、照射された部分の前記組成物を除去し、基板上に残留する前記組成物の層を焼成することを含んでなることを特徴とする、レーザーアブレーションによる機能膜の製造法と、それに用いるレーザーアブレーション加工用組成物。

(もっと読む)

BSZT誘電体、キャパシタ及び不揮発性メモリ並びにそれらの製造方法

【課題】鉛やビスマスを含まず有害性が少ない新規材料としてBa,SrZr,TiO3BSZTを用い、パルスレーザ照射によるPLA 法によりBSZT をSrTiO3STO及びPt 上にペロブスカイト単相膜として成膜させて、BSZTを用いたMIM型素子を作製する。

【解決手段】薄膜試料は、パルスレーザ照射によるPLA 法によりSTO 基板上1にPt3とBSZT2 を堆積したBSZT/Pt/STO を形成する。下部電極Pt3上には<100>、<110>、<111>の多軸配向したBSZT2 を形成する。さらに真空蒸着により上部電極としてAu4を蒸着し、Au/BSZT/Pt/STO としたMIM 型素子を作製する。

(もっと読む)

半導体デバイスの製造方法

【課題】ゲート絶縁層を常圧、低温プロセス、短時間で形成し、ゲート絶縁層を有する半導体デバイスのより簡易な製造方法を提供することにある。

【解決手段】ゲート電極、ゲート絶縁層、半導体層、ソース電極及びドレイン電極を有する半導体デバイスの製造方法において、前記ゲート絶縁層をマイクロ波を照射して形成することを特徴とする半導体デバイスの製造方法。

(もっと読む)

金属酸化物薄膜の形成方法

【課題】半導体基板の表面を酸化膜で保護しつつ、金属酸化物薄膜形成時に酸化膜の酸素を還元して成膜を行うことで、高品質な金属酸化物薄膜を得る。

【解決手段】半導体基板2を化学溶液に浸し、半導体基板2上に酸化膜4を形成する。その後、半導体基板2を成膜装置に導入し、単結晶金属酸化物薄膜6を成膜させる。半導体基板2を加熱した状態で、成膜装置内で、金属原子および酸化ガスを半導体基板2の酸化膜4に供給する。酸化膜4は金属原子に還元され、半導体基板2の表面に単結晶金属酸化物薄膜6が成膜される。

(もっと読む)

半導体装置及びその製造方法

【課題】 格子間のシリコンによるキャリア移動度の劣化を抑制し、トランジスタ性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 Si基板5上にゲート絶縁膜3を形成する前の工程でSi基板5の酸化を行わず、酸化膜が必要な場合はCVD法又はPVD法により成膜する。

(もっと読む)

低誘電率絶縁膜および半導体装置の製造方法

【課題】 半導体装置を構成する絶縁膜の比誘電率を低下させることができる方法を提供する。

【解決手段】 半導体装置を構成する絶縁膜2に不活性ガス、窒素および水素の内の少なくとも一種のイオン6を注入して絶縁膜2中に多数の空隙8を形成し、絶縁膜2の比誘電率をイオン注入前よりも低下させ、これによって低誘電率絶縁膜10を得る。

(もっと読む)

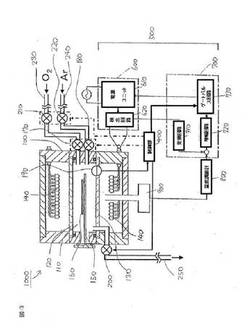

半導体ウエハの処理方法及びシステム並びに半導体デバイスの製造方法

【課題】皮膜の品質を向上させた薄いゲート酸化皮膜のような絶縁皮膜或いは酸化皮膜が形成可能な半導体ウエハの処理方法を提供する。

【解決手段】酸化皮膜をプロセスチャンバ204内にて形成するために、ウエハ210を加熱するための熱源214に加えて、光源216により紫外線光等のような光のエネルギをウエハ210に照射することにより、皮膜の品質を向上させる。

(もっと読む)

絶縁膜形成方法

【課題】導電性基板若しくは半導電性基板に設けられた非常に微細な貫通孔の内側表面であっても、均一な絶縁膜を形成することができるとともに、貫通孔の開口部においても内部においても確実に信頼性の高い絶縁膜を形成することができる絶縁膜形成方法を提供すること。

【解決手段】導電性基板若しくは半導電性基板に設けられた貫通孔の内表面に絶縁膜を形成する絶縁膜形成方法として、前記貫通孔の開口部に第1の絶縁膜を形成する工程と、該貫通孔の内表面に第2の絶縁膜を形成する工程と、該第2の絶縁膜を硬化させる工程とを有することを特徴とする。ここで、第1の絶縁膜は、物理的蒸着方法又は化学的蒸着方法によって形成された絶縁膜であり、第2の絶縁膜は、電着塗装によって形成された絶縁膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】 成膜中に低誘電率界面層を生成させず、かつ熱処理後も低誘電率界面層の生成を抑制でき、ゲート絶縁膜としての High-k膜を有効利用する。

【解決手段】 Si基板10上にゲート絶縁膜12を形成した後にゲート電極13を形成する工程を含む半導体装置の製造方法であって、ゲート絶縁膜12として、Zr,Hf,Ti,及びランタノイド金属のうち少なくとも一つを含む酸化膜を、500℃以上800℃以下の温度領域で、且つ酸素分圧が1×10-4Pa以下の雰囲気下で成膜する。

(もっと読む)

半導体装置およびその製造方法

【課題】 高速動作が可能で信頼性に優れた半導体装置を提供する。また、High−k膜を用いてヒステリシスの増加を抑制するとともに、移動度の小さい半導体装置の製造方法を提供する。

【解決手段】 シリコン基板の上に形成されたシリコン酸窒化膜と、このシリコン酸窒化膜の上に形成された高誘電率絶縁膜とを有する半導体装置において、シリコン酸窒化膜中の窒素濃度が膜厚方向に分布を持ち、このシリコン酸窒化膜中の窒素濃度の平均値に対してシリコン基板との界面付近で低く、高誘電率絶縁膜との界面付近で高くなることを特徴とする。これにより、熱処理によるヒステリシスの増加および移動度の低下の小さい半導体装置とすることができる。

(もっと読む)

多孔質膜の堆積方法

【課題】基板上に多孔質膜を堆積させる処理方法を提供する。

【解決手段】多孔質シリカ膜及びドープシリカ膜を堆積させる処理方法。本方法は、循環方式を用い、各サイクルは、最初にシリカをシリコンと共に共堆積させる段階と、次に選択的にシリコンを除去して多孔質構造体を形成する段階とを含む。好ましい実施形態では、共堆積は、プラズマ強化化学気相蒸着によって行われる。反応剤給送流れは、共堆積反応剤と選択的シリコン除去反応剤との混合物を含む。RF電力変調を使用して、共堆積段階及び選択的シリコン除去段階を制御し、後者は、RF電力が切られるか又は低レベルに低減される度に進行する。本発明を用いて、高度に均一な小さな孔隙及び望ましい空隙率プロフィールを有する多孔質膜を取得することができる。本方法は、半導体集積回路製造のための広範囲の低−k誘電体を形成するのに有利である。本方法はまた、他の用途のための他の多孔質膜を形成するのにも有利である。

(もっと読む)

21 - 40 / 44

[ Back to top ]