Fターム[5F058BH03]の内容

絶縁膜の形成 (41,121) | 無機絶縁膜形成後の処理 (2,470) | 熱処理(後処理) (1,507) | 雰囲気 (896) | 酸化雰囲気 (425)

Fターム[5F058BH03]に分類される特許

81 - 100 / 425

半導体装置の製造方法及び製造装置

【課題】高いアスペクト比で狭い幅の溝に、シリコン酸化膜を埋め込むことの可能な、スループットの高い半導体製造方法を提供する。

【解決手段】半導体装置の製造方法において、基板を処理室内へ搬入する工程と、炭素及び水素を含むシリコン化合物ガスを処理室内へ供給して、処理室内を第1の圧力の状態にする工程と、処理室内を前記第1の圧力にした状態において、処理室内へ供給されたシリコン化合物ガスに紫外光を照射して、基板上にシリコン酸化膜を形成する工程と、処理室内を前記第1の圧力よりも低い第2の圧力の状態にする減圧処理工程とを行う。これにより、高アスペクト比で狭い幅の溝内に、緻密なシリコン酸化膜を形成することができる。

(もっと読む)

ポリシラザンを含むコーティング組成物

【課題】埋設性と塗布性とに優れ、すぐれた膜物性を有するシリカ質膜を形成することができるコーティング組成物とそれを用いたシリカ質膜の形成方法の提供。

【解決手段】ペルヒドロポリシラザンと溶媒とを含んでなるコーティング組成物であって、前記ペルヒドロポリシラザンの分子量分布曲線が、分子量800〜2,500の範囲と、分子量3,000〜8,000の範囲とにそれぞれ極大を有し、重量平均分子量Mwと数平均分子量Mnの比Mw/Mnが6〜12である、コーティング組成物。このコーティング組成物ギャップを有する基板上に塗布し、1000℃以下で加熱することにより、ギャップ深部まで埋設されたシリカ質膜を形成させることができる。

(もっと読む)

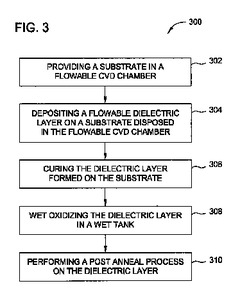

流動性CVD処理から形成された誘電体材料上で実行される湿式酸化処理

基板内に画定されたトレンチまたはビアを充填するケイ素含有誘電体材料上で湿式酸化処理を実行する方法が提供される。一実施形態では、誘電体材料を基板上に形成する方法は、流動性CVD処理によって誘電体材料を基板上に形成するステップと、基板上に配置された誘電体材料を硬化させるステップと、基板上に配置された誘電体材料上で湿式酸化処理を実行するステップと、酸化させた誘電体材料を基板上に形成するステップとを含む。  (もっと読む)

(もっと読む)

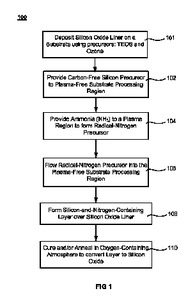

酸化物ライナを使用する流動可能な誘電体

酸化ケイ素層を形成する方法が記載される。方法は、無炭素シリコン含有前駆体をラジカル−窒素前駆体と混合すること、シリコン−窒素含有層を基板上に堆積することを含む。ラジカル−窒素前駆体は、プラズマ内に水素−窒素含有前駆体を流すことによって、プラズマ中で形成される。シリコン−窒素含有層を堆積する前に、酸化ケイ素ライナ層が形成され、シリコン−窒素含有層の接着、平滑性、流動性を改善する。シリコン−窒素含有層は、膜を硬化およびアニーリングすることにより、シリコン−酸素含有層に変換することができる。方法は、酸化ケイ素ライナ層を形成し、その後スピンオンシリコン含有材料を塗布することも含む。  (もっと読む)

(もっと読む)

ラジカル成分CVD用のインサイチュオゾン硬化

誘電体層を形成する方法を説明する。この方法は、ケイ素を含有する前駆体をプラズマ廃水と混合するステップと、ケイ素と窒素を含有する層を基板上に堆積するステップとを含む。ケイ素と窒素を含有する層は、ケイ素と窒素を含有する層を堆積するために使用したのと同じ基板処理領域内においてオゾン含有雰囲気中で硬化することによって、ケイ素と酸素を含有する層に転換される。さらなるケイ素と窒素を含有する層を、ケイ素と酸素を含有する層の上に堆積することができ、ここでも基板を基板処理領域から取り出すことなく、層のスタックをオゾン中で硬化させることができる。複数回の堆積−硬化サイクル後、ケイ素と酸素を含有する層のスタックの転換は、より高い温度で酸素含有環境中においてアニールすることができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】 本発明の目的は、高温での酸化膜形成におけるリスクを回避しつつ酸化膜の膜質を向上させ、電気特性を改善することにある。また、本発明の他の目的は、酸化膜形成の際に、下地となる材料の消費を最小限に抑え、微細な構造への適正な酸化膜形成を実現することにある。

【解決手段】 基板を収容した処理容器内に所定元素を含む原料ガスを供給し排気して、基板上に所定元素含有層を形成する工程と、加熱された大気圧未満の圧力雰囲気下にある処理容器内に酸素含有ガスと水素含有ガスとを供給し排気して、所定元素含有層を酸化層に変化させる工程と、を交互に繰り返して、基板上に所定膜厚の酸化膜を形成する工程と、加熱された大気圧未満の圧力雰囲気下にある処理容器内に酸素含有ガスと水素含有ガスとを供給し排気して、基板上に形成された酸化膜を改質する工程と、を有する。

(もっと読む)

結晶化膜の製造方法及び結晶化装置

【課題】基板上に形成されたアモルファス膜の結晶化を、基板表面に対して垂直方向(即ち下から上方向)ではなく略平行方向(即ち横方向)に進行させる結晶化膜の製造方法を提供する。

【解決手段】本発明の一態様は、基板上にアモルファス膜1を形成し、前記アモルファス膜1にレーザ光を照射してレーザ光照射領域1aを結晶化し、前記アモルファス膜1に熱処理を施すことにより、前記レーザ光照射領域以外のアモルファス膜1を結晶化することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】PZTの配向性を向上できる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上方に、絶縁膜を形成する工程と、絶縁膜上方に、Ptで下部電極用導電膜を形成する工程と、下部電極用導電膜を、酸素を含む雰囲気に曝し、Ptの酸化膜を形成する工程と、下部電極用導電膜上に、PZTで強誘電体膜を形成する工程と、強誘電体膜上に、上部電極用導電膜を形成する工程とを有する。

(もっと読む)

素子分離材料用塗布液の作製方法、素子分離材料用塗布液、素子分離層用薄膜、素子分離層用薄膜の形成方法、基板、及び、基板の形成方法

【課題】基板と素子分離層との剥離やクラックが発生し難く、凹状の溝を有する基板上に平坦な素子分離層を形成することができる素子分離材料用塗布液の作製方法等を提供する。

【解決手段】素子分離材料用塗布液の作製方法では、Si(OR1)4(R1は炭素数2〜6個の有機基)で表される第1のアルコキシシラン化合物と、R2nSi(OR3)4−n(R2はメチル基、エチル基、プロピル基、ビニル基、または、フェニル基、R3は炭素数2〜6個の有機基、nは1〜3の整数)で表される第2のアルコキシシラン化合物と、第1の溶媒との混合液を作製する。第1のアルコキシシラン化合物と第2のアルコキシシラン化合物とは、全アルコキシシラン化合物に対する第2のアルコキシシラン化合物のモル比が0.09〜0.9となるように混合する。この混合液を加水分解、縮合して絶縁膜形成前駆体を作製し、これに第2の溶媒を加え、塗布液を作製する。

(もっと読む)

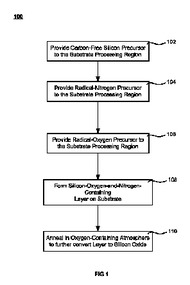

非炭素ラジカル成分CVD膜向けの酸素ドーピング

酸化ケイ素層を形成する方法が開示される。これらの方法は、ラジカル前駆体とラジカル酸素前駆体の両方を炭素のないケイ素含有前駆体と同時に組み合わせるステップを含む。ラジカル前駆体およびケイ素含有前駆体の1つは窒素を含有する。このような方法の結果、ケイ素、酸素、および窒素含有層が基板上に堆積される。次いで、ケイ素、酸素、および窒素含有層の酸素含有量を増大させて、窒素をほとんど含有しない酸化ケイ素層を形成する。ラジカル酸素前駆体およびラジカル前駆体は、別個のプラズマまたは同じプラズマ内で作り出すことができる。酸素含有量の増大は、酸素含有雰囲気の存在下でこの層をアニールすることによって引き起こすことができ、膜の密度は、不活性環境中の温度をさらに高くすることによって、さらに増大させることができる。  (もっと読む)

(もっと読む)

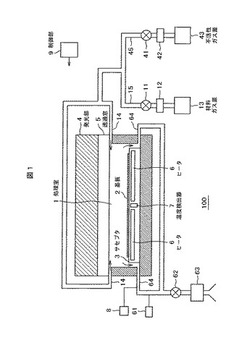

膜の少なくとも一部を酸化シリコンに変換し、および/または、蒸気内紫外線硬化を利用して膜の品質を改善し、および、アンモニア内紫外線硬化を利用して膜を高密度化するシステムおよび方法

【課題】膜の少なくとも一部を酸化シリコンに変換し、および/または、蒸気内UV硬化を利用して膜の品質を改善し、および、アンモニア内UV硬化を利用して膜を高密度化するシステムおよび方法を提供する。

【解決手段】チャンバ14内に蒸気を供給する段階と、チャンバ14内に、シリコンを含む堆積層が設けられている基板22を配置する段階と、所定の変換期間にわたって、蒸気の存在下で、堆積層にUV光を当てて、堆積層を少なくとも部分的に変換する段階とを備えるシステム10および方法を提供する。また、チャンバ14内にアンモニアを供給する段階と、チャンバ14内に、堆積層を有する基板22を配置する段階と、アンモニアの存在下で所定の変換期間にわたって堆積層にUV光を当てて、少なくとも部分的に堆積層を高密度化する段階とを備える。

(もっと読む)

無炭素流動性化学気相堆積膜の硬化

酸化ケイ素層を形成する方法を説明する。この方法は、無炭素ケイ素含有前駆体を活性窒素および/または水素前駆体と混合するステップと、ケイ素窒素水素含有層を基板上に堆積するステップを含みうる。次に、ケイ素窒素水素含有層をケイ素酸素含有層に変換することが、オゾン含有雰囲気中で低温アニール(「硬化」)によって開始される。このオゾン含有雰囲気中でのケイ素窒素含有膜の酸化ケイ素への変換は不完全でもよく、酸素含有環境中でより高温のアニールによって増大させることができる。  (もっと読む)

(もっと読む)

引張膜のための応力管理

クラッキングする傾向を減少させた、間隙充填酸化ケイ素層の形成が記載される。堆積は、トレンチの充填を容易にする、流動可能なシリコン含有層の形成を含む。高い基板温度における後続の処理が、従来技術の方法に従って形成された流動可能な膜よりも、誘電体膜中のクラッキングを少なくする。間隙充填酸化ケイ素層の形成に先立って堆積された圧縮性ライナ層が記載され、後続して堆積される膜がクラックする傾向を減少する。流動可能なシリコン含有層の後に堆積される圧縮性キャッピング層も、クラッキングを減少させるように決定された。圧縮性ライナ層および圧縮性キャッピング層は、単独でまたは組み合わせて使用され、クラッキングを減少させ、多くの場合クラッキングをなくすことができる。開示した実施形態の圧縮性キャッピング層は、下にある窒化ケイ素の層を酸化ケイ素層に変換できることが、さらに確定されている。 (もっと読む)

金属酸化膜の成膜方法、酸化マンガン膜の成膜方法及びコンピュータ読み取り可能な記憶媒体

【課題】 Cuとの密着性を良好とすることが可能な金属酸化膜の成膜方法を提供すること。

【解決手段】 下地上に有機金属化合物を含むガスを供給し、下地上に金属酸化膜を成膜する金属酸化膜の成膜方法であって、下地上に有機金属化合物を供給して下地上に金属酸化膜を成膜し(工程2)、かつ、金属酸化膜の成膜プロセスの最後に、金属酸化膜を酸素含有ガス又は酸素含有プラズマに曝す(工程4)。

(もっと読む)

半導体装置の製造方法

【課題】SiCを酸化する際に生成された炭素が不純物として酸化膜(SiO2)中に残留してしまうことを抑制し、チャネル移動度を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、炭化シリコンを含む基板11上に酸化シリコン膜12を形成する工程と、酸化シリコン膜12上に金属酸化膜13を形成する工程と、酸素を含む雰囲気中で熱処理を行い、酸素を金属酸化膜13に透過させて酸化シリコン膜12に拡散させることにより、酸化シリコン膜12に残留する炭素を酸化させる残留炭素酸化工程と、を有することを特徴とする。

(もっと読む)

シリカ質膜製造方法およびそれに用いるポリシラザン塗膜処理液

【課題】ポリシラザン化合物を用いて、低温で表面が親水性のシリカ質膜を得る方法の提供。

【解決手段】基板の表面上に、ポリシラザン化合物およびシリカ転化反応促進化合物を含んでなる組成物を塗布し、得られた塗膜に、ポリシラザン塗膜処理液を塗布し、300℃以下でポリシラザン化合物をシリカ質膜に転化させるシリカ質膜製造方法。このポリシラザン塗膜処理液は、過酸化水素とアルコールと溶媒とを含むものである。

(もっと読む)

酸化膜形成方法

【課題】酸化膜とCVD膜との密着性を高めて界面特性の優れた膜の作製を実現する。

【解決手段】処理チャンバ205内において、処理基板に対してオゾン含有ガスのみを供給して処理基板上に酸化膜を形成する酸化工程と、この酸化工程を経た処理基板に対してCVD原料ガスとオゾン含有ガスとを供給して当該処理基板上に前記原料ガスの成分の酸化物からなる酸化膜を形成させるCVD工程とが実行される。前記CVD工程の初期段階の製膜速度は前記酸化工程の製膜速度よりも小さく制御される。また、前記CVD工程を経た処理基板をオゾン含有ガスの雰囲気または紫外光領域の波長を有する光が照射されたオゾン含有ガスの雰囲気に曝すアニール工程と、このアニール工程を経た処理基板を前記CVD工程に供する工程とを有するとよい。前記アニール工程を経た処理基板を前記CVD工程に供する工程を複数繰り返すとなおよい。

(もっと読む)

半導体装置の製造方法

【課題】浮遊ゲート電極を有するメモリセルの高集積化を実現する半導体装置の製造方法を提供する。

【解決手段】半導体層11の表面にトンネル絶縁膜12を介してシリコンを含む第1の導電体層を形成する工程と、第1の導電体層の表面から半導体層11に至る分離溝9を形成し、第1の導電体層が所定幅で分離された、浮遊ゲート電極となる複数の導電板13bを形成する工程と、導電板13b側面の中間部まで、分離溝9を素子間絶縁膜15で埋め込む工程と、複数の導電板13bの間隔を所定幅と同等以上の幅に維持しながら、導電板13bの露出面にシリコン窒化膜16aを形成する工程と、制御ゲート電極19aとなる第2の導電体層を形成して分離溝9の上部を埋め込む工程と、を備え、シリコン窒化膜16aは、窒素元素を含む原料ガスを励起させて生成する窒素ラジカルによって、導電板13bに含まれるシリコンを窒化して形成される。

(もっと読む)

半導体装置の製造方法

【課題】金属ゲート電極/高誘電体ゲート絶縁膜構造のMISトランジスタを有する半導体装置を高性能化する。

【解決手段】シリコン基板1上に、順に、ハフニウムおよび酸素を主体とする高誘電体膜hk1と、第1金属および酸素を主体とし、化学量論的組成よりも多くの第1金属を含むpMIS用キャップ膜Cp1を形成する。その後、シリコン基板1に、第1熱処理と第2熱処理とを順に施す。続いて、pMIS用キャップ膜Cp1上にゲート電極用金属膜EM1を形成し、これらを加工することでpMIS用金属ゲート電極pG1とpMIS用高誘電率ゲート絶縁膜pI1とを形成する。特に、第1熱処理では高誘電体膜hk1中の余剰酸素を除去し、第2熱処理では高誘電体膜hk1中にpMIS用キャップ膜Cp1中の第1金属を拡散させる。第1熱処理は、第2熱処理よりも低い温度で施す。

(もっと読む)

81 - 100 / 425

[ Back to top ]