Fターム[5F083ER02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236)

Fターム[5F083ER02]の下位に属するFターム

トンネル注入 (539)

アバランシェ注入 (30)

ドレイン側から注入 (159)

ソース側から注入 (122)

CGから注入 (32)

CG以外のゲートから注入 (3)

チャネルから注入 (368)

ソース/ドレインを除く拡散領域から注入 (4)

Fターム[5F083ER02]に分類される特許

101 - 120 / 979

不揮発性半導体記憶装置

【課題】ゲート電極間絶縁膜のリーク電流を抑制し、電気的信頼性を向上した不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板上に行列状に形成された複数のメモリ素子と、同一列方向のメモリ素子に選択的に接続される複数のビット線と、同一行方向のメモリ素子に接続される複数のワード線とを具備し、各メモリ素子は、半導体基板上に順次形成された第1のゲート絶縁膜、電荷蓄積層、第2のゲート絶縁膜、制御電極と、電荷蓄積層の対向する側面に沿って、前記シリコン基板上面に形成された1対の不純物注入層とを具備し、ビット線に垂直な方向に沿った断面における電荷蓄積層の上部コーナー部が曲面を有し、上部コーナー部が前記第1のゲート絶縁膜の上方にある。

(もっと読む)

半導体記憶装置の動作方法

【課題】メモリセルの有効活用を図りつつ、特性ばらつきが使用時に影響しないようにした半導体記憶装置の動作方法を提供する。

【解決手段】実施形態によれば、半導体記憶装置の動作方法は、基板上に積層された複数の電極層と交差して前記基板の上方に延びるチャネルボディを通じて直列に接続された複数のメモリセルのうち、最上層のメモリセル及び最下層のメモリセルの少なくともいずれかに、読み出し専用データを格納し、前記読み出し専用データが格納された読み出し専用メモリセルのデータ消去動作は禁止する。

(もっと読む)

フラッシュメモリアレイのワード線構造を保護するためのワード線保護装置およびフラッシュメモリアレイのためのワード線構造

【課題】製造中に、プロセスに関連する帯電からフラッシュメモリのワード線およびメモリセルを保護するための方法と構造とを与える。

【解決手段】ドープされたポリシリコンのワード線110aの端部にドープされていないポリシリコン110bが形成され、抵抗110bが生成される。これを通じて、プロセスにより生じる電荷が、基板に結合された、ドープされたポリシリコン放電構造110cへ放電される。ワード線抵抗110b、および、放電構造110cは、単一のパターニングされたポリシリコン構造として形成される。ワード線110aおよび放電部分110cは導電性になるように選択的にドープされ、また、抵抗部分110bは、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】選択ゲート電極の側壁にメモリゲート電極を有する不揮発性記憶装置を微細化することができる技術を提供する。

【解決手段】選択ゲート電極CGをダミーパターンの側壁にサイドウォール形状で形成することで、メモリゲート電極MGが選択ゲート電極CGの両壁に形成されなくなり、フォトマスクの位置ずれを考慮する必要がなくなる。また、選択ゲート電極CGをサイドウォール状に形成することで、選択ゲート電極CGのゲート長が縮小しても、選択ゲート電極CGを構成する導電膜の膜厚により精度よく制御することを可能とする。

(もっと読む)

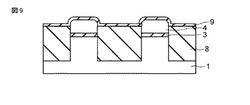

半導体記憶装置及びその製造方法

【課題】ビット線に拡散層を用いる半導体記憶装置のチャネル領域に発生する2次電子を抑制して信頼性を向上できるようにする。

【解決手段】半導体記憶装置100は、P型の半導体基板101の上部にそれぞれが互いに並行に延びるように形成された複数のビット線拡散層108と、半導体基板101の上で、且つそれぞれが各ビット線拡散層108と交差する方向に互いに並行に延びるように形成された複数のワード線電極110とを有している。さらに、半導体基板101における各ワード線電極110の下方の領域には、周囲よりも濃度が低いP型の複数の第3の不純物層111Aがそれぞれ自己整合的に形成されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】書込・消去特性が高く、動作の信頼性が高い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板上に設けられたトンネル絶縁膜と、前記トンネル絶縁膜上に設けられた第1電極と、前記第1電極上に設けられた電極間絶縁膜と、前記電極間絶縁膜上に設けられた第2電極と、を備える。前記電極間絶縁膜は、積層絶縁層と、前記積層絶縁層上に設けられ、前記積層絶縁層よりもバリアハイトが低い電荷蓄積層と、前記電荷蓄積層上に設けられ、前記電荷蓄積層よりもバリアハイトが高いブロック絶縁層と、を有する。前記積層絶縁層は、第1絶縁層と、前記第1絶縁層上に設けられ、前記第1絶縁層よりもバリアハイトが低い量子効果層と、前記量子効果層上に設けられ、前記量子効果層よりもバリアハイトが高い第2絶縁層と、を有する。

(もっと読む)

半導体素子の製造方法、半導体メモリの製造方法、及び半導体素子

【課題】 中電圧トランジスタを形成するための工程数の増加を抑制することが可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板の上に、下部絶縁膜、下部絶縁膜とは異なる材料からなる中間絶縁膜、及び中間絶縁膜とは異なる材料からなる上部絶縁膜を順番に形成する。半導体基板の表面の第1の領域の上部絶縁膜を除去し、第2の領域には、上部絶縁膜を残す。第1の領域の下部絶縁膜と中間絶縁膜とをゲート絶縁膜として含む第1のトランジスタと、第2の領域の下部絶縁膜、中間絶縁膜、及び上部絶縁膜をゲート絶縁膜として含む第2のトランジスタとを形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルに書き込み用のトランジスタ、読み出し用のトランジスタおよび選択用のトランジスタを備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】不揮発性メモリと容量素子を有し、性能を向上させる半導体装置を提供する。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MG6nとp型ウエルPW1との間および制御ゲート電極CG4nとメモリゲート電極MG6nとの間には、内部に電荷蓄積層5bを有する絶縁膜5が形成されている。この絶縁膜5は、酸化シリコン膜5aと、その上に形成された窒化シリコン膜5bと、その上に形成された酸化シリコン膜5cと、その上に形成されかつ酸化シリコン膜5cよりも薄い絶縁膜5dとの積層膜からなる。この絶縁膜5dは、ポリシリコンからなるメモリゲート電極MG6nに接している。絶縁膜5dは、Hf,Zr,Al,Ta,Laのうちの少なくとも1種を含む金属化合物により形成されているため、フェルミピニングを生じることができ、誘電率が高い。

(もっと読む)

半導体装置およびその製造方法

【課題】スプリットゲート構造の不揮発性メモリセルを有する半導体装置において、製造歩留まりを向上できる技術を提供する。

【解決手段】給電領域に位置するCGシャント部の選択ゲート電極CGの半導体基板1の主面からの第2高さd2が、メモリセル形成領域の選択ゲート電極CGの半導体基板1の主面からの第1高さd1よりも低くなるように、CGシャント部の選択ゲート電極CGを形成する。

(もっと読む)

半導体装置

【課題】メモリ回路を含む半導体装置の低消費電力化を図ることを課題とする。

【解決手段】メモリ回路を含む半導体装置において、メモリ回路はワード線とビット線で規定される領域に設けられた半導体素子を有するメモリセルと半導体素子を有さないメモリセルを含み、該半導体素子には、酸化物半導体を用いて形成したオフ電流が極めて低いトランジスタを用いるため、読み出し精度が高まり、低電圧動作が可能となる。また、メモリセルは、ハイまたはローのいずれか一方のデータを記憶し、半導体素子を有するメモリセルは、前記データを構成するハイおよびローのうち、少ない方を記憶し、半導体素子を有さないメモリセルは、多い方を記憶する。

(もっと読む)

不揮発性半導体メモリ、及び不揮発性半導体メモリへの書込み方法

【課題】不揮発性半導体メモリの周辺回路を小さくし、集積回路の縮小化に寄与する。

【解決手段】p型基板10に形成され、ソース線430と接続するn型拡散層50と、p型基板10上に設けられ、ワード線400と接続するワード電極200と、p型基板10とワード電極200の間に設けられたワード絶縁層と、n型拡散層50上、及びワード電極200の側壁に設けられたトンネル絶縁層と、トンネル絶縁層上に設けられた電荷蓄積層と、電荷蓄積層上に設けられたコントロール絶縁層と、コントロール絶縁層上に設けられ、コントロール線420と接続するコントロール電極300と、を備え、制御部は、メモリ素子600に書込みを行うときに、ソース線430に正電圧を印加し、ワード線400に負電圧を印加し、かつコントロール線420に正電圧を印加する不揮発性半導体メモリ。

(もっと読む)

不揮発性半導体記憶装置、不揮発性半導体記憶装置の動作方法

【課題】チップ面積の増大を抑制しつつ、安定的に動作するスプリットゲート型不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体メモリのベリファイステップを以下の手順で実行する。(a)通常読み出し動作のワードゲート電圧よりも低いベリファイ電圧を、ワードゲートに供給する。(b)通常読み出し動作のコントロールゲート電圧を、コントロールゲートに供給する。(c)そのベリファイ電圧とそのコントロールゲート電圧とに応じて流れる電流が、通常読み出し動作のときの参照電流に一致するか否かを判定する。TwinMONOSセルの消去ベリファイ時に、ワードゲートの電圧を低くすることで、コントロールゲートの負電圧を利用せずに消去ベリファイを可能にする。

(もっと読む)

半導体装置およびその製造方法

【課題】電荷を蓄積可能な電荷蓄積膜を有する不揮発性メモリセルを含む半導体装置において、データ保持特性劣化を改善し、その信頼性を向上させることにある。

【解決手段】半導体基板の主面に不揮発性メモリセルを含む半導体装置であって、不揮発性メモリセルは、半導体基板上に第1絶縁膜と、導電膜と、第2絶縁膜と、電荷を蓄積可能な電荷蓄積膜とを有する。また、電荷蓄積膜上に第3絶縁膜と、第1ゲート電極と、第1絶縁膜から前記第1ゲート電極までの一連の積層膜と接するように第4絶縁膜と、第1絶縁膜と並ぶように前記半導体基板上に第5絶縁膜とを有する。さらに、第5絶縁膜上に形成され、第4絶縁膜の側面に前記第1ゲート電極と隣り合うように第2ゲート電極と、第1ゲート電極と第2ゲート電極を挟むように半導体基板にソース領域およびドレイン領域とを有する。半導体装置は、導電膜と電荷蓄積膜が平面的に重なり合うように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリを有する半導体装置の性能を向上させる。

【解決手段】不揮発性メモリのメモリセルは、p型ウエルPWの上部に絶縁膜3を介して形成された制御ゲート電極CGと、p型ウエルPWの上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGとp型ウエルPWとの間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されかつ内部に電荷蓄積部を有する絶縁膜5とを有している。メモリゲート電極MGは、ノンドープのシリコン膜6aと不純物を導入したシリコン膜6bとの積層膜により形成されている。シリコン膜6bの不純物濃度を高くすることでメモリゲート電極MGの抵抗を低くして不揮発性メモリの動作速度を向上させ、シリコン膜6aの不純物濃度を低くすることで、不揮発性メモリのデータ保持特性を向上させることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】絶縁層と、絶縁層中に埋め込まれたソース電極、およびドレイン電極と、絶縁層表面、ソース電極表面、およびドレイン電極表面、の一部と接する酸化物半導体層と、酸化物半導体層を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根(RMS)粗さが1nm以下であり、絶縁層表面の一部とソース電極表面との高低差、および絶縁層表面の一部とドレイン電極表面との高低差は、5nm以上の半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】電荷蓄積層をもち、電荷のトラップを利用する記憶素子の保持特性を向上させる技術を提供する。

【解決手段】電荷蓄積層(24)の上のメモリゲート(21)と、第1サイドゲート(22)と、第2サイドゲート(23)と、第1サイドゲート(22)側の第1不純物注入領域(31)と、第2サイドゲート(23)側の第2不純物注入領域(32)と、チャネル領域(33、34、35)とを具備する不揮発性半導体記憶装置を構成する。チャネル領域(33、34、35)は、電荷蓄積層(24)の下の第1領域(33)と、第1領域(33)と第1不純物注入領域(31)との間のセレクト側領域(34)と、第1領域(33)と第2不純物注入領域(32)との間のアシスト側領域(35)とを含むことが好ましい。そして、ゲート長方向におけるセレクト側領域(34)の長さ(L1)は、アシスト側領域(35)の長さ(L2)よりも長いものとする。

(もっと読む)

不揮発性半導体記憶装置

【課題】ホットキャリア注入によって書き換えを行うスプリットゲート型MONOSメモリにおいて、リテンション特性を向上させる。

【解決手段】メモリセルM00の選択ゲート電極は選択ゲート線SG0に接続され、メモリゲート電極はメモリゲート線MG0に接続される。また、ドレイン領域はビット線BL0に接続され、ソース領域はソース線SL0に接続される。さらに、メモリセルM00が形成されたp型ウエル領域にはウエル線WL0が接続される。メモリセルM00に書き込みを行うときは、ウエル線WL0を通じてp型ウエル領域に負電圧を印加しながら、ソースサイド注入方式による書込みを行う。

(もっと読む)

半導体装置及びそれを用いた論理回路

【課題】面積を縮小させることが出来、また歩留まりを向上させる半導体装置及びそれを用いた論理回路を提供すること。

【解決手段】第1トランジスタTr1と第2トランジスタTr2とが形成され、前記第1トランジスタTr1はソース及びドレインとして機能する第1拡散層群103と、第1ゲート電極102と、第2ゲート電極104とを備え、前記第2トランジスタTr2はソース及びドレインとして機能する第2拡散層群201と、電荷を蓄積可能な浮遊ゲート202と、第3ゲート電極200とを備え第2ゲート電極200は、前記第1トランジスタTr1の閾値Vthを制御可能とし、この第2ゲート電極104の電位は、前記浮遊ゲート202が蓄積する電荷量に応じた値である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

101 - 120 / 979

[ Back to top ]