Fターム[5F083ER02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236)

Fターム[5F083ER02]の下位に属するFターム

トンネル注入 (539)

アバランシェ注入 (30)

ドレイン側から注入 (159)

ソース側から注入 (122)

CGから注入 (32)

CG以外のゲートから注入 (3)

チャネルから注入 (368)

ソース/ドレインを除く拡散領域から注入 (4)

Fターム[5F083ER02]に分類される特許

41 - 60 / 979

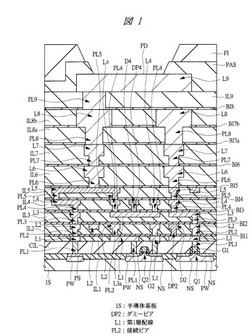

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置

【課題】緻密で高耐圧な絶縁膜を提供することを目的とする。

【解決手段】基板上に半導体膜を有し、半導体膜上に第1の絶縁膜を有し、第1の絶縁膜上に導電膜を有し、導電膜上に第2の絶縁膜を有し、第1の絶縁膜は、第2の絶縁膜よりも緻密であり、第1の絶縁膜は、珪素と、酸素と、窒素とを有する。第1の絶縁膜は、希ガスを有し、その膜厚は、1nm以上100nm以下である。このような第1の絶縁膜はゲート絶縁膜として機能させる。

(もっと読む)

デュアル機能を有する不揮発性半導体メモリセル

【課題】デュアル機能を有する不揮発性半導体メモリセルは、基板、第1ゲート、第2ゲート、第3ゲート、電荷蓄積層、第1拡散領域、第2拡散領域及び第3拡散領域を有する。

【解決手段】第2ゲート及び第3ゲートは、デュアル機能のワンタイムプログラミング機能に対応する第1電圧及びデュアル機能のマルチタイムプログラミング機能に対応する第2電圧を受けるために用いられる。第1拡散領域は、ワンタイムプログラミング機能に対応する第3電圧及びマルチタイムプログラミング機能に対応する第4電圧を受けるために用いられる。第2拡散領域は、マルチタイムプログラミング機能に対応する第5電圧を受けるために用いられる。

(もっと読む)

半導体メモリの製造方法及び製造装置

【課題】自動的に処理レシピを変更することにより製造歩留を向上させることができる半導体メモリの製造方法及び製造装置を提供する。

【解決手段】計算部が、第2酸化膜厚、第1酸化膜厚、ゲート電極幅、アクティブ領域幅とを含む測定値を受け取り、半導体メモリのセル部の予測電流値を算出する工程(S3)と、プロセス処理実行部が、予測電流値が基準電流値以下であると判断されたときに第1処理レシピを選択し、予測電流値が基準電流値より大きいと判断されたときに第2処理レシピを選択し、第1及び第2処理レシピのうちの選択された処理レシピに従って浮遊ゲート電極の側壁を覆うSWを形成する工程(S4,S5,S6)とを有し、第2処理レシピに従って形成されたSWの第1方向の膜厚である第2のSW膜厚が、第1処理レシピに従って形成されたSDの第1方向の膜厚である第1のSW膜厚よりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性半導体装置の高集積化を図ることのできる技術を提供する。

【解決手段】スイッチ用nMIS(Qs)のスイッチゲート電極SGと、スイッチ用nMIS(Qs)にワード線に対して交差する方向に沿って隣接するメモリ用nMIS(Qm)のメモリゲート電極MGとの間に、スイッチ用nMIS(Qs)のソース/ドレイン領域SDHとして機能し、同時にメモリ用nMIS(Qm)のドレイン領域Dとして機能する半導体領域を形成し、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)側のソース/ドレイン領域SDHを構成する半導体領域の形状と、スイッチ用nMIS(Qs)のメモリ用nMIS(Qm)と反対側(ビット線側)のソース/ドレイン領域SDLを構成する半導体領域の形状とを非対称とする。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体記憶装置

【課題】電荷蓄積層及び制御ゲートを有する半導体記憶装置のバックバイアス効果による影響を低減させることにより集積度を向上させ、占有面積を増加させずに浮遊ゲートと制御ゲートとの容量の比をより一層増大させるとともに、製造プロセスに起因するセル特性のばらつきが抑制された半導体記憶装置を提供する。

【解決手段】半導体基板と、少なくとも1つの島状半導体層110、該島状半導体層110の側壁の周囲の全部又は一部に形成された電荷蓄積層513及び制御ゲート523から構成される少なくとも1つのメモリセルとを有する半導体記憶装置であって、前記メモリセルの島状半導体層110が不純物拡散層により前記半導体基板から電気的に絶縁されてなる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の電気的性能および信頼性を向上させる。

【解決手段】スプリットゲート型の不揮発性メモリのメモリゲート電極MGは、金属膜6aと金属膜6a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極であり、金属膜6aの上端部には、金属膜6aの一部が酸化することで金属酸化物部分17が形成されている。スプリットゲート型の不揮発性メモリの制御ゲート電極は、金属膜4aと金属膜4a上のシリコン膜6bとの積層膜で形成されたメタルゲート電極である。

(もっと読む)

半導体装置およびその製造方法

【課題】不揮発性メモリおよび容量素子を有する半導体装置の性能を向上させる。

【解決手段】同一の半導体基板1上に、不揮発性メモリのメモリセルMCと容量素子とが形成されている。メモリセルMCは、半導体基板の上部に絶縁膜3を介して形成された制御ゲート電極CGと、半導体基板1の上部に形成されて制御ゲート電極CGと隣合うメモリゲート電極MGと、メモリゲート電極MGと半導体基板1との間および制御ゲート電極CGとメモリゲート電極MGとの間に形成されて内部に電荷蓄積部を有する絶縁膜5とを有している。容量素子は、制御ゲート電極CGと同層のシリコン膜で形成された下部電極と、絶縁膜5と同層の絶縁膜で形成された容量絶縁膜と、メモリゲート電極MGと同層のシリコン膜で形成された上部電極とを有している。そして、上部電極の不純物濃度は、メモリゲート電極MGの不純物濃度よりも高くなっている。

(もっと読む)

不揮発性半導体記憶装置

【課題】 BiCSメモリのような積層型メモリの書き込み動作を高速化することが可能な不揮発性半導体記憶装置を提供する。

【解決手段】 積層型のメモリセル構造を有する不揮発性半導体記憶装置であって、半導体基板上に、複数のメモリセルを積層してなるストリングを複数個配置したメモリセルアレイ11と、メモリセルアレイ11の任意のストリングをサンプルストリングとして選択し、該選択したサンプルストリングに対してデータの書き込みを行う回路12,14,16,30と、サンプルストリングの各メモリセルに対する書き込み回数をレイヤー毎に保持する書き込み回数記憶部31と、記憶部31に記憶されたレイヤー毎の書き込みパルス数を同一レイヤーの他のストリングのメモリセルの書き込み電圧の初期値に反映させる回路33とを備えている。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

半導体装置およびその製造方法

【課題】ワードライン間の素子分離を行い、メモリセルの微細化が可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10内に形成されたビットライン14と、ビットライン14上にビットライン14の長手方向に連続して設けられた絶縁膜ライン18と、ビットライン14間の半導体基板10上に設けられたゲート電極16と、ゲート電極16上に接して設けられ、ビットライン14の幅方向に延在したワードライン20と、ビットライン14間でありワードライン20間の半導体基板に形成されたトレンチ部22と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】埋め込みビットライン型不揮発メモリの微細化に適した製造方法を提供し、かつコンタクトの位置ずれに起因するビットライン間ショートを生じ難い構造を提供する。

【解決手段】導電体膜が埋め込まれたシャロートレンチ溝内にビットライン拡散層を設けてSONOS構造セルとする。これにより、ビットライン拡散層の半導体基板主面上での面積を大きくせずにビットライン拡散層の抵抗を低くすることができ、セル面積を増大させることなく安定した電気的特性の半導体記憶装置が得られる。また、Si3N4のサイドウォールを設けてイオン注入することでビットラインを形成する。これにより、メモリセルの微細化が可能となる。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

41 - 60 / 979

[ Back to top ]