Fターム[5F083ER02]の内容

半導体メモリ (164,393) | EPROM、EEPROMの書込、消去方法 (6,790) | キャリア制御 (6,786) | 電子注入 (2,236)

Fターム[5F083ER02]の下位に属するFターム

トンネル注入 (539)

アバランシェ注入 (30)

ドレイン側から注入 (159)

ソース側から注入 (122)

CGから注入 (32)

CG以外のゲートから注入 (3)

チャネルから注入 (368)

ソース/ドレインを除く拡散領域から注入 (4)

Fターム[5F083ER02]に分類される特許

961 - 979 / 979

スプリットゲート型のフラッシュメモリ素子及びその製造方法

【課題】 スプリットゲート型のフラッシュメモリ素子及びその製造方法を提供する。

【解決手段】 フローティングゲート及びコントロールゲートを形成する前に半導体基板上にマスクパターンを形成した後、マスクパターンの側壁によって自己整列されるようにフローティングゲート及びコントロールゲートを順次形成するスプリットゲート型のフラッシュメモリ素子。メモリセルを構成するフローティングゲートは、基板の主面に平行な第1面と、基板の主面に垂直である第2面と、第1面と第2面との間に延びているカーブ面を有する。コントロールゲートは、フローティングゲートの第1面の延長線とフローティングゲートの第2面の延長線との間で90゜より小さな角度範囲に限定される領域内で、前記フローティングゲートのカーブ面上に形成されている。

(もっと読む)

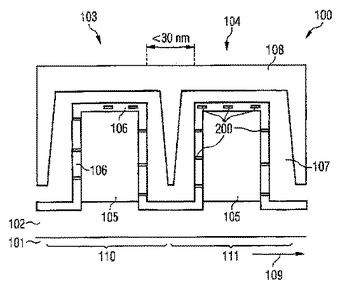

フラッシュメモリ装置のワード線を保護するための方法および装置

製造中に、プロセスに関連する帯電からフラッシュメモリのワード線(WL)およびメモリセル(101)を保護するための方法と構造とが与えられる。ドープされたポリシリコンのワード線(110a)の端部にドープされていないポリシリコン(110b)が形成され、抵抗(110b)が生成される。これを通じて、プロセスにより生じる電荷が、基板(102)に結合された、ドープされたポリシリコン放電構造(110c)へ放電される。ワード線抵抗(110b)、および、放電構造(110c)は、単一のパターニングされたポリシリコン構造として形成される。ワード線(110a)および放電部分(110c)は導電性になるように選択的にドープされ、また、抵抗部分(110b)は、製造後に通常のセル動作が可能なほどに十分高い抵抗が与えられる一方で、製造中にプロセスに関連する電荷に対しては放電路を供給するように、実質的にドープされない。  (もっと読む)

(もっと読む)

NROMデバイス

【課題】1セルに対して複数のビットが記憶可能な高性能のフラッシュメモリトランジスタを提供する。

【解決手段】NROMフラッシュメモリセルのアレイは、4F2あたり少なくとも2ビットを記憶するように構成される。スプリット縦型チャネルは、隣接する柱状部の各側面に沿って形成される。単一の制御ゲートが柱状部及び柱状部間のトレンチ内にわたって形成される。スプリットチャネルは、トレンチ底部のn+領域、又はトレンチ底部を覆うように形成されるチャネルによって接続され得る。各ゲート絶縁層は、チャネル長の増大により、他の電荷記憶領域から十分に分離した状態で電荷を記憶することができる。

(もっと読む)

縦型EEPROMNROMメモリデバイス

【課題】電荷捕獲領域の重なりがなく、過消去特性が改善された、より狭い素子間隔の高密度なNROMメモリアレイを製造する方法及び構造体を提供する。

【解決手段】NOR又はNAND型高密度メモリ構成において縦型NROMメモリセル及び縦型選択ゲートを有効に利用するNROM EEPROMメモリデバイス及びアレイが開示される。本発明に係るメモリの実施形態では、縦型選択ゲート及び縦型NROMメモリセルを用いて、NOR及びNAND型NROM構成のメモリセル列、メモリセグメント及びメモリアレイを形成する。これらNROMメモリセル構成によって、構成要素として選択ゲートを有するメモリデバイス又はメモリアレイをより高密度にすることが可能となる。これらメモリデバイス又はメモリアレイにおいては、半導体製造プロセスによって作製可能な加工寸法を利用することができ、かつ、典型的なマルチビットNROMセルにおいて存在する電荷分離に関する問題を被ることがない。さらに、上述のメモリセル構造体は、NROMメモリセルからそれらに関連したビット/データ線及び/又はソース線とを絶縁する選択ゲートの後ろに、NROMメモリセルを配置することによって、擾乱及び過消去問題を軽減することが可能となる。

(もっと読む)

単一ポリ・2−トランジスタベースのヒューズ素子

ポリシリコンの単一層内に配置されたダブルゲート構造を有した、電気的にプログラム可能なトランジスタヒューズ(200)。このトランジスタヒューズ(200)では、第1のゲート(216)は、ソース領域(210)の一部と重なり合うように配置されていて、第2のゲート(215)は、第1のゲート(216)からは絶縁されていると共に、ドレイン領域(211)の一部と重なり合うように配置されている。第1のゲート(216)は、外部から供給されたコントロール信号を入力するための端子を有しており、第2のゲート(215)は、ドレイン領域(211)に容量結合されている。第2のゲート(215)は、第2のゲート(215)の容量結合を大きくするための結合装置(220)と、ヒューズプログラミング電圧を低くするためのドレイン領域(211)とを含んでいる。  (もっと読む)

(もっと読む)

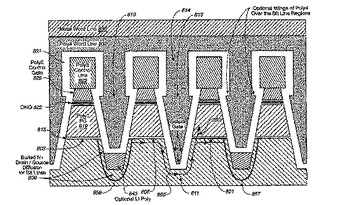

ピラー構造セルのフラッシュメモリ技術

ピラー形不揮発性メモリセル803は各々がトレンチ810によって隣接するメモリセルから絶縁されるメモリセルを各々有している。各メモリセルは基板上に処理層を積層することによって形成される。すなわち、トンネル酸化物層815、ポリシリコンフローティングゲート層819、ONOまたは酸化物層822、ポリシリコンコントロールゲート層825である。ステップの多くの態様が自己整合される。これらのメモリセルのアレイにはより少ない分割しか必要ない。さらに、このメモリセルは、電子がフローティングゲート819に対して直角またはほぼ垂直843に向けられるので、プログラミング特性が増強される。  (もっと読む)

(もっと読む)

ブリッジ電界効果トランジスタメモリセル、上記セルを備えるデバイス、および、ブリッジ電界効果トランジスタメモリセルの製造方法

本発明は、第1および第2の各ソース/ドレイン領域、第1および第2の各ソース/ドレイン領域の間に配置されたチャネル領域とを備え、これらの各ソース/ドレイン領域とチャネル領域とが半導体ブリッジに形成されている、ブリッジ電界効果トランジスタメモリセルに関するものである。

本発明のメモリセルは、さらに、半導体ブリッジの少なくとも部分上に堆積されている電荷記憶層と、電荷記憶層の少なくとも一部上の金属性で導電性のゲート領域とを備え、電荷記憶層は、ブリッジ電界効果トランジスタメモリセルに所定の電気的電圧を印加することにより、選択的に、電気的な電荷キャリアが、電荷記憶層に対し導入されるように、または、電荷記憶層から除去されるように配置されている。  (もっと読む)

(もっと読む)

非対称のポケットドープ領域を有するメモリトランジスタおよびメモリユニット

本発明は、特に、ソース領域(S)近傍において、ポケットドープ領域(114)を1つ有しているフラッシュメモリトランジスタ(T11)に関する。上記メモリトランジスタ(T11)は、読み出し処理中において、ロードメモリ状態を妨害することなく機能する。 (もっと読む)

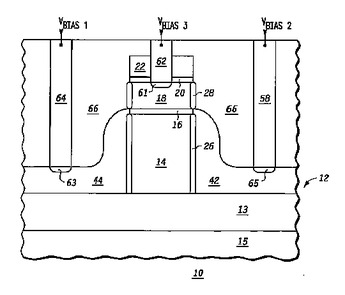

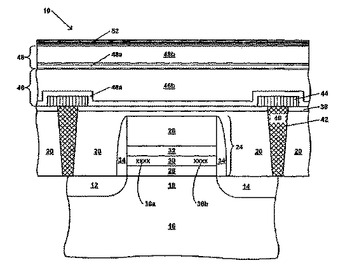

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

自己整合型電荷分離構造NROMフラッシュメモリ

【課題】電荷捕獲領域が重ならずにセルを小さくすることが可能なトランジスタを提供する。

【解決手段】窒化物リードオンリーメモリ(NROM)セルは、窒化物層を有し、前記窒化物層は、トランジスタの中心部の下方に配置されない。前記窒化物層を有するゲート絶縁層は、2つの部分を有する。各部分は、構造分離された(structurally defined and separated)電荷捕獲領域を有する。電荷は、トランジスタの動作方向に応じて、ある特定の捕獲領域に蓄積される。前記ゲート絶縁層の前記2つの部分は、ポリシリコンゲート構造体の中間部分から外側部分を分離する。

(もっと読む)

過剰消去されたセルを復旧させるために、正のゲートストレスを使用したメモリデバイスおよびそのための方法

複数のメモリセルから構成されたフラッシュ電気的消去可能読出し専用メモリ(EEPROM)デバイス(10)の消去方法は、複数のメモリセル(10)をプリプログラミングするステップ(100)と、複数のメモリセル(10)に消去パルスを印加するステップ(110)と、を有し、これに消去検証(120)が続く。この消去検証(120)の後に、スレッショルド電圧が所定の最小レベル(VTMIN)を下回るメモリセルのソフトプログラミング(135)と、複数のメモリセル(10)への正のゲートストレスの印加(130)が続く。この消去方法は、過剰消去を防止し、スレッショルド電圧分布を低減する。  (もっと読む)

(もっと読む)

ビットライン間の結合補償のある不揮発性メモリおよび方法

メモリ蓄積ユニットの1つの連続するページをプログラムするとき、メモリ蓄積ユニットは、その目標の状態に達してプログラミングが禁止されるか、或いはそれ以上のプログラミングからロックアウトされる度に、なおプログラムされつつある隣接するメモリ蓄積ユニットに動揺を生じさせる。本発明は、プログラミングの一部として、動揺に対するオフセットがなおプログラムされつつある隣接するメモリ蓄積ユニットに加えられるようになっている回路および方法を提供する。このオフセットは、プログラミングが禁止されているメモリ蓄積ユニットとなおプログラムされつつあるメモリ蓄積ユニットとの隣接するビットライン間の制御された結合によって加えられる。このようにして、高密度メモリ蓄積ユニットを並列にプログラムする動作に固有のエラーが除去されるか、或いは最小にされる。  (もっと読む)

(もっと読む)

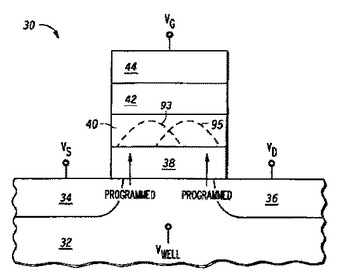

個別電荷蓄積素子を有するメモリのプログラミング

不揮発性メモリ(100)は、個別電荷蓄積素子(40)を有するトランジスタ群(30)から成るアレイを含む。トランジスタに対しては、2ステップ書き込み方法(60)を使用して書き込みを行ない、この方法では、第1ステップ(68)が低ゲート電圧によるホットキャリア注入(hot carrier injection:HCI)書き込みである。第2ステップ(78)を幾つかのメモリセルに対して選択的に利用して注入電荷分布を変え、トランジスタメモリセル内部の各メモリビットの間の電荷分布間隔を大きくする。書き込みを行なう第2ステップは、書き込み操作に長い余分な時間が加わることなく行われる。一の例では、第1ステップにおいて電子を注入し、そして第2ステップにおいてホールを注入する。2つのステップを実行して分布が形成される結果、蓄積媒体の中心部分の電子電荷が取り除かれる。  (もっと読む)

(もっと読む)

不揮発性メモリのソース制御操作

フラッシュEEPROMなどの不揮発性メモリが、自己限定プログラミング技術を用いて並列にプログラムされ得るメモリセルを有する。個々のセルは、自己限定的に熱い電子で荷電され得る電荷記憶装置を有する。電荷記憶装置が必要なレベルの電荷に達すると、熱い電子はそれ以上生成されないか、或いは少数しか生成されない。熱い電子の生成が停止する電荷レベルは、セルに印加される電圧によって決まる。このように、複数のセルが並列にプログラムされ、印加電圧に対応する電荷レベルで各々のセルが自己限定される。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

BEOLプロセスにおいて、UVによって誘発されたSONOSデュアルビットのフラッシュメモリデバイスの電荷を低減するUVブロック層

SONOSフラッシュメモリセル(24)をUVにより誘発される電荷から保護する方法であって、SONOSフラッシュメモリセル(24)を半導体デバイス(10、50)に製造するステップと、SONOSフラッシュメモリセル(24)上に、少なくとも1つのUV保護層(38、46、48、又は52)を蒸着させるステップとを含み、UV保護層には実質的にUV不透過性の材料が含まれる。SONOSフラッシュメモリセル(24)と、少なくとも1つのUV保護層(38、46、48又は52)(UV保護層には実質的にUV不透過性の材料が含まれる)を含むSONOSフラッシュメモリデバイス(10、50)が提供される。  (もっと読む)

(もっと読む)

フラッシュメモリデバイスの特性を改善する方法

半導体デバイスを製造する方法において、シリコン基板(62)上にゲート酸化膜(60)を提供する。このゲート酸化膜(60)上に第1ポリシリコン層(64)を提供し、第1ポリシリコン層(64)上に絶縁層(66)を提供し、またこの絶縁層(66)上に第2ポリシリコン層(68)を提供する。適切なマスキングを実行した後にエッチングステップが実行されると、シリコン基板を露出させ、かつこのシリコン基板上にスタックゲート構造を形成すべく、第2ポリシリコン層、絶縁層、第1ポリシリコン層、およびゲート酸化膜の一部を除去するようにこれらの層がエッチングされる。スタックゲート構造(72)上に薄い酸化膜(80)を成長させるべく、短時間(例えば10秒から20秒)の急速熱アニールを実行する。それから、急速熱アニールによって形成された酸化膜(80)上に第2酸化膜(82)をたい積する。

(もっと読む)

(もっと読む)

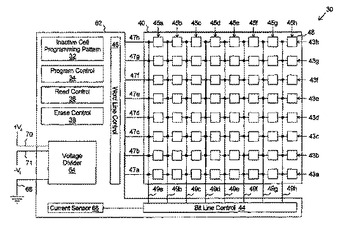

非揮発性メモリセルアレイの非活性領域に隣接する非揮発性メモリセルを読み出すための改善された方法

メモリセル48のアレイ30にデータパターンをストアし、再生するための方法であり、活性コラム45b及び45gと、不活性コラム45c及び45fとを含み、活性コラム45b及び45gにデータパターンをストアする。不活性メモリセルプログラミングパターン32が識別される。バルク消去中、過消去及び活性メモリセル48への電流リークを回避するために定期的に電荷をストアする目的で電荷がストアされる、不活性コラム45c及び45fのメモリセル48の全てあるいは選択された複数のメモリセルを、前述の不活性メモリセルプログラミングパターン32が識別する。  (もっと読む)

(もっと読む)

半導体記憶装置

【課題】 ゲート絶縁膜の劣化を防止すると共に、浮遊ゲート内のキャリアの電荷量を正確に制御できるようにする。さらに、書き込み時の消費電力を不要にする。

【解決手段】 開示されている半導体記憶装置は、浮遊ゲート6に一部分が接すると共に他部分がP型シリコン基板1に接するようにモット絶縁体7を設け、このモット絶縁体7に金属−絶縁相転移を生じさせる。そして、浮遊ゲート6に対してキャリアである電子の注入又は放出を行う場合、ゲート酸化膜5を通じてではなく、モット絶縁体7の金属相を通じてキャリアの注入又は放出を行う。

(もっと読む)

961 - 979 / 979

[ Back to top ]