Fターム[5F083FR01]の内容

Fターム[5F083FR01]の下位に属するFターム

Fターム[5F083FR01]に分類される特許

21 - 40 / 352

薄膜キャパシタ

【課題】MIM構造の薄膜キャパシタにおいて、Ptに代わる上部電極を用いた場合であっても、IV特性や信頼性を維持する。

【解決手段】薄膜キャパシタ10は、基板12上に、下部電極14,誘電体層16,上部電極18を順次形成したMIM構造であり、上下の電極のうち、少なくとも上部電極18が、窒化物と金属を積層した積層電極となっている。窒化物としては、Ta,Tiなどの高融点金属を含むことが好ましく、また、窒化物と積層される金属が、前記窒化物に含まれる金属と同じであることが好ましい。更に、窒化物がSiを含んでいてもよい。少なくとも上部電極18に窒化物を含む積層電極を用いることで、Pt電極を用いる場合に必要だった特性回復のアニール処理の必要なく、同等のIV特性を得られるとともに信頼性も向上する。また、誘電体層16と上部電極18の密着性が改善され、剥離が生じない。

(もっと読む)

強誘電性電界効果トランジスタデバイス

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットは、Alを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、ターゲットのCu含有量を10ppm以下およびAg含有量を1ppm以下とする。

(もっと読む)

スパッタリングターゲットとそれを用いたTi−Al−N膜および電子部品の製造方法

【課題】FeRAMやDRAMなどに使用されるTi−Al−N膜などの成膜用のTi−Al合金ターゲットにおいて、不純物量の低減を図った上で、ターゲットの製造歩留りを高めると共に、膜品質の向上などを図る。

【解決手段】スパッタリングターゲットはAlを5〜50原子%の範囲で含有するTi−Al合金からなる。このようなTi−Al合金ターゲットにおいて、Zr含有量およびHf含有量をそれぞれ100ppb以下とする。

(もっと読む)

半導体装置

【課題】強誘電体キャパシタの高集積化を図り、且つ、強誘電体キャパシタの特性を向上させることができる、強誘電体キャパシタ構造を提供するものである。

【解決手段】強誘電体キャパシタは、強誘電体膜を優先配向に成長させるための下地膜と、下地膜の上に形成された強誘電体膜と、強誘電体膜の上面に第1の方向に沿って所定間隔で形成された、強誘電体膜に電圧を印加するための、一対の電極と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の強誘電体キャパシタによる凹凸形状の影響を受けてキャパシタを被覆する水素バリア膜の水素拡散阻止能力が劣化すること、および強誘電体キャパシタの分極特性がばらつくことを防止する半導体記憶装置とその製造方法を提供する。

【解決手段】半導体基板1上に形成された強誘電体キャパシタ19を被覆する層間絶縁膜20として、ペロブスカイト型金属酸化物絶縁体、ビスマス層状ペロブスカイト型酸化物強誘電体などのような金属酸化物を含む絶縁体からなる膜を用いる。このような膜はスピンコート法で形成できるので容易にその表面が平坦な膜が得られ、従ってその上に形成される水素バリア膜22の膜厚も一様となって水素拡散阻止能力が維持できる。また膜20は酸素が透過しやすい性質を有するので、酸素熱処理により強誘電体キャパシタ19における分極特性のばらつきも十分防止できる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】電極に挟み込まれる強誘電体膜を特性のばらつきなく形成することのできる半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、半導体基板Sと、半導体基板S上に形成された一対のソース/ドレイン拡散層11を有するセルトランジスタTと、セルトランジスタTに接続された強誘電体キャパシタCとを備える。セルトランジスタT及び強誘電体キャパシタCにより1つのメモリセルが構成される。強誘電体キャパシタCは、半導体基板Sの表面に垂直な方向を長手方向として延びる電極31と、電極31の側面に接するように設けられた強誘電体膜32と、半導体基板Sの表面に垂直な方向を長手方向として延び且つ電極31との間に強誘電体膜32を挟み込むように設けられた電極31とを備える。強誘電体膜32は、有機材料により構成されている。

(もっと読む)

半導体装置の製造方法

【課題】強誘電体キャパシタのキャパシタ誘電体膜がダメージを受けるのを抑制する半導体装置の製造方法を提供する。

【解決手段】シリコン基板1の上方に第1の絶縁膜を形成する工程と、第1の絶縁膜の上に、第1の導電膜20、強誘電体膜21、及び第2の導電膜を形成する工程と、第2の導電膜の上にハードマスク23aを形成する工程と、ハードマス23aをマスクにし、第2の導電膜をエッチングして上部電極22aにする工程と、強誘電体膜21をパターニングしてキャパシタ誘電体膜にする工程と、第1の導電膜20をエッチングして下部電極にする工程とを有し、第2の導電膜をエッチングする工程において、上部電極22aの横に強誘電体膜21が露出したときに、エッチング雰囲気が、酸素ガスを含み且つハロゲンを含まない雰囲気となっている。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体又は高誘電体を用いた容量絶縁膜を有する半導体装置において、容量絶縁膜の結晶化時に酸素バリアが還元されることを確実に防止する。

【解決手段】半導体装置は、複数の酸素バリア膜16と、複数の酸素バリア膜16の各々の上に、下部電極17、容量絶縁膜19及び上部電極20からなるキャパシタ21と、複数のキャパシタ21を覆うように形成された層間絶縁膜22とを備えている。層間絶縁膜22における隣り合うキャパシタ21間に位置する部分の上面が、層間絶縁膜22におけるキャパシタ21の直上に位置する部分の上面よりも低い。

(もっと読む)

アモルファス膜を備える半導体装置、及び半導体装置の製造方法

【課題】Ti及びAlを含有するほかに、Nを任意成分として含むことがあるアモルファス膜を導電性バリア層として用いる。

【解決手段】基板22の第1主面22aの上側に、導電性バリア層14と、導電性バリア層の上側に形成された下部電極16と、下部電極の上側に形成された強誘電性の金属酸化物からなるキャパシタ絶縁膜18とを備え、及び導電性バリア層が、Ti及びAlを含むほかに、任意成分としてNを含むことがあるアモルファス膜である。

(もっと読む)

半導体記憶装置

【課題】強誘電体膜の膜質を均一化するチェインFeRAM型半導体記憶装置を提供する。

【解決手段】半導体記憶装置80は、同一素子形成領域に隣接配置される、一対のソース/ドレイン層5を有するメモリトランジスタTR1及びTR2と、メモリトランジスタのソース/ドレイン層5の他方とメモリトランジスタTR2のソース/ドレイン層5の一方に、ビア及びバリアメタル膜13を介して接続される強誘電体キャパシタCAP1及びCAP2とを有する。強誘電体キャパシタCAP1及びCAP2は、バリアメタル膜13上に設けられ、四角錐台形状の下部電極14と、下部電極14を覆うように設けられる強誘電体膜15とを共有し、強誘電体キャパシタCAP1は、強誘電体膜15上に設けられる第1の上部電極16aを有し、強誘電体キャパシタCAP2は、強誘電体膜15上に設けられ、第1の上部電極16aと離間して配置される第2の上部電極16bを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】強誘電体キャパシタの下部電極材料の選択自由度が高く、ビア工程の少ない半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板101上に形成されたスイッチングトランジスタ301A,301Bと、拡散層121と、トランジスタ301上に形成された層間絶縁膜131と、下部電極211、強誘電体膜212、及び上部電極213を含む強誘電体キャパシタ201A,201Bと、上部電極213の上方に形成された配線層141と、上部電極213と配線層141とを電気的に導通させる第1のプラグTWと、拡散層121と配線層141とを電気的に導通させる第2のプラグV1A,V1Bと、下部電極211の側方に配置されており、下部電極211と拡散層121とを電気的に導通させる第3のプラグCSFとを備える。

(もっと読む)

半導体記憶装置

【課題】

本発明は、より微細化可能な半導体記憶装置を提供する。

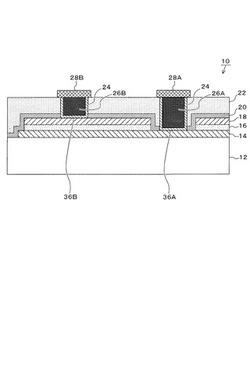

【解決手段】 半導体基板10と、前記半導体基板10上に設けられた複数のトランジスタ14a,14bと、前記トランジスタ14a,14b上に設けられ、下部電極20a,20bと上部電極22a,22bとの間に設けられた強誘電体膜21a,21bを含む複数の強誘電体キャパシタ23a,23bと、前記半導体基板10と前記下部電極20a,20bを接続する下層コンタクトプラグ17a,17bと、前記上部電極22a,22b上に設けられた上層コンタクトプラグ26a,26bと、隣接する前記上層コンタクトプラグ間に設けられ、前記上層コンタクトプラグと前記半導体基板とを接続する共有コンタクトプラグ27とを備え、前記共有コンタクトプラグ27が、前記上層コンタクトプラグ26a,26bと直接接触し、接続されることを特徴とする半導体記憶装置。

(もっと読む)

半導体集積回路装置

【課題】MISFETのソース/ドレイン間の寄生容量を減少させる電極および配線を有したメモリや、メモリ混載のロジック等の半導体集積回路を提供する。

【解決手段】ゲート電極5より上方に少なくともキャパシタ電極14,16または情報記憶部の一部を有する半導体集積回路装置において、MISFETは、ソース・ドレイン拡散層7に接続する少なくとも1つずつの第1のプラグ9を有する。ソース・ドレイン拡散層7のどちらか一方に、第1のプラグ9を介して接続し、キャパシタまたは情報記憶部の一部の下部電極14と同一工程またはそれより前工程の配線層から成る第1の配線21を設け、一方のソース・ドレイン拡散層7の上方に第1の配線21と他の配線22を接続するプラグを設けず、また、ソース・ドレイン拡散層7の他方の領域の上方に第1の配線21と同一工程の配線を設けないようにする。

(もっと読む)

強誘電体記憶装置

【課題】強誘電体キャパシタの上部電極上にコンタクトプラグを容易に形成することができ、かつ、強誘電体キャパシタ上方の水素バリア膜の破損を抑制した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板10上に設けられた複数のトランジスタと、複数のトランジスタ上に設けられた第1の層間絶縁膜ILD1と、第1の層間絶縁膜ILD1上に設けられた複数の強誘電体キャパシタCと、複数の強誘電体キャパシタCの上面および側面を被覆する第1の水素バリア膜HB1と、強誘電体キャパシタCの上方に設けられ、並びに、隣接する2つの強誘電体キャパシタC間に間隙または空孔Hを有する状態で埋め込まれた第2の層間絶縁膜ILD2と、間隙または空孔Hの開口部を閉じるように第2の層間絶縁膜ILD2上を被覆するカバー絶縁膜CIと、カバー絶縁膜CI上を被覆する第2の水素バリア膜HB2とを備える。

(もっと読む)

半導体記憶装置

【課題】データ伝送速度を高めつつ、メモリ面積も縮小する。

【解決手段】メモリ領域1のビット線BLは、Y方向に延びて第1センスアンプ領域2に形成された第1センスアンプ回路SA1に接続される。ローカルデータ線LDQ、BLDSが、第1センスアンプ領域2、配線領域5を介して第2センスアンプ領域3まで配設される。第2センスアンプ領域3の第2センスアンプ回路SA2からは、メインデータ線MDQ、BMDQが、X方向に延びてメモリ領域1上に最上層のM4配線として配設される。

(もっと読む)

集積回路装置の製造方法

【課題】

エッチングフェンスを発生させずに集積回路装置を製造すること。

【解決手段】 第1のマスクと、前記第1のマスクより異方性エッチングに対する耐性が高く且つ所定の形状を有する第2のマスクとを積層したエッチングマスクを、被エッチング層の上に形成する第1の工程と、前記エッチングマスク及び前記被エッチング層に前記異方性エッチングを施して、前記被エッチング層を、前記第2のマスクに対応した形状にエッチングする第2の工程とを有し、前記第2の工程において、前記異方性エッチングにより前記第2のマスクを、垂直方向及び水平方向にエッチングしながら、前記被エッチング層をエッチングすること。

(もっと読む)

不揮発性半導体記憶装置

【課題】強誘電体キャパシタを積層した構造を有し、読み出し速度を向上させつつ微細化を可能とする不揮発性半導体記憶装置を提供する。

【解決手段】強誘電体キャパシタC1、C2を互いに直列に接続し、強誘電体キャパシタC1、C2の接続点に対する導通状態をセルトランジスタM1にて制御し、プレート線PL0Aを強誘電体キャパシタの他端C1に接続し、プレート線PL0Bを強誘電体キャパシタの他端C2に接続し、ビット線BL0、BL1を共有する複数のメモリセルMC00〜MC03にてプレート線PL0A、PL0Bを共有させる。

(もっと読む)

強誘電体メモリ素子の製造方法

【課題】分極方向の均一性が高められた強誘電体層を有し、書き込み及び読み出しに際しての精度を高め得る強誘電体メモリ素子の製造方法。

【解決手段】基板2上に電極3が形成されており、電極3上に強誘電体層4が積層されている積層体を用意し、水分を23g/m3以上含むガス雰囲気下で積層体を熱処理する、強誘電体メモリ素子1の製造方法。

(もっと読む)

強誘電体メモリ

【課題】強誘電体メモリの信頼性を向上する。

【解決手段】本発明の例に関わる強誘電体メモリは、半導体基板50内に設けられる拡散層23,24と、拡散層23,24間のチャネル領域上にゲート絶縁膜を介して設けられるゲート電極21と、を有する電界効果トランジスタ2と、層間絶縁膜51内に埋め込まれ、拡散層23,24上に設けられるコンタクトプラグ30,31と、層間絶縁膜51上及びコンタクトプラグ30,31上に設けられる酸化防止膜40と、酸化防止膜40上に設けられる強誘電体膜10と、強誘電体膜10及び酸化防止膜40を貫通して、コンタクトプラグ30,31上に設けられる電極11,12と、を有するキャパシタ1と、電極11,12間の酸化防止膜40上に設けられ、強誘電体膜10に対して種結晶として機能するシード層41と、を具備する。

(もっと読む)

21 - 40 / 352

[ Back to top ]