Fターム[5F083GA27]の内容

Fターム[5F083GA27]の下位に属するFターム

Fターム[5F083GA27]に分類される特許

161 - 180 / 3,320

OTPメモリ

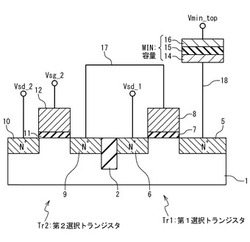

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

エッチング方法、これに用いられるシリコンエッチング液、及び半導体基板製品の製造方法

【課題】多結晶シリコン及び/又はアモルファスシリコンについて、シリコン等を的確かつ高速に除去し、一方で残される電極部材等を損傷させずに維持することができるシリコンエッチング液及びこれを用いたエッチング方法、これを用いた半導体基板製品を提供する。

【解決手段】アニオン性基を有する炭素数3以上の化合物と硝酸とフッ化水素酸とを水性媒体中に含有するシリコンエッチング液を準備し、該シリコンエッチング液を多結晶シリコン及び/又はアモルファスシリコンからなるシリコン膜に適用して、キャパシタとなる凹凸形状を形成するエッチング方法。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】相変化膜の組成が変わることを抑えつつ、基板の凹部に対する相変化膜の埋め込み性を高めることのできる相変化メモリの形成方法、及び相変化メモリの形成装置を提供する。

【解決手段】相変化メモリの形成に際し、金属カルコゲナイドターゲットをスパッタして絶縁膜23の上面23s及びホール23h内に相変化膜24を形成する。次いで、相変化膜24を覆うキャップ膜25を形成する。更に、相変化膜24を加熱して、相変化膜24によってホール23hを埋め込むリフローを行う。キャップ膜25は、絶縁膜23よりも相変化膜24に対する濡れ性が低い材料で形成される。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造のフラッシュメモリーの提供

【解決手段】

半導体基板1上にシリコン窒化膜2及びシリコン酸化膜3が選択的に設けられ、シリコン酸化膜3上には、選択的に横(水平)方向エピタキシャルSi層5が設けられ、Si層5の両側面には、それぞれ側面を接して横(水平)方向エピタキシャルSi層6が設けられた構造からなる半導体層が素子分離領域のシリコン窒化膜4により絶縁分離されている。Si層6の残りの周囲には第1のゲート酸化膜10を介して包囲型フローティングゲート電極11が設けられ、包囲型フローティングゲート電極11の周囲には第2のゲート酸化膜12を介して包囲型コントロールゲート電極13(ワード線)が設けられ、Si層5には概略ソースドレイン領域9が設けられている2重包囲型ゲート電極を有するMIS電界効果トランジスタより構成したフラッシュメモリー。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】 所望の深さを有し幅の狭い凹部を半導体基板に安定して形成することが可能な製造方法を提供すること。

【解決手段】 本発明は、半導体基板10の一部に酸素イオン注入を行うことで第1酸素含有領域24を形成する工程と、半導体基板10に熱処理を行い、第1酸素含有領域24に含まれる酸素を用いて第1酸素含有領域24を酸化させることで、第1酸素含有領域24を第1酸化領域26とする工程と、第1酸化領域26を除去することで半導体基板10に凹部16を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体素子及びその製造方法

【課題】フラッシュメモリ素子の安全性及び信頼性を改善することができる半導体素子及びその製造方法を提供する。

【解決手段】第1方向に沿って延長された活性領域を含む半導体基板と、半導体基板の上部に第1方向に交差する第2方向に沿って形成されたセレクトラインと、セレクトラインの間の前記活性領域それぞれに形成されて第1不純物を含む接合領域と、セレクトラインの間の空間を埋め込む多層の酸化膜と、接合領域の下部に繋がれて半導体基板の活性領域に形成されて第2不純物を含む接合領域延長部と、多層の酸化膜のうち少なくともいずれか一層を貫通して接合領域及び接合領域延長部に接触されたコンタクトプラグと、を含む。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】TSV構造を採用し複数のチップをスタックした半導体装置を、改良された入出力形式で提供できるようにする。

【解決手段】複数のチップをスタックしてなり、隣り合うチップ間の接続を、貫通電極を介して行なうTSV構造を持つ半導体装置に適用される。各チップは複数のチャンネルに対応した複数のTSVアレイ部を備え、該複数のTSVアレイ部は、スタックするチップの数に応じて入出力に寄与するTSVアレイ部と入出力回路に接続されないパススルーのTSVアレイ部とに分けられている。スタックするチップの数に応じて2段目以降のチップを面方向に回転させてスタックし、前記パススルーのTSVアレイ部を経由してデータの入出力を行なう構成とすることにより、前記データの入出力に寄与するTSVアレイ部にのみ共有の入出力回路を備える構成とし、入出力回路の数を低減させた。

(もっと読む)

可変抵抗絶縁層を用いたメモリ素子及びそれを有するプロセッサシステム

【課題】可変抵抗材料を用いて形成されるランダムアクセスメモリ装置を提供する。

【解決手段】可変抵抗メモリ装置301において、望ましい円錐状に形造された下部電極308は、下部電極308の頂点のところにおける絶縁材料312の厚さが最も薄く、下部電極308の頂点のところにおける電界が最大であることを確保する。電極308、310の配置およびメモリ素子の構造はメモリ装置内に安定で確実に導電路を作り出し、かつ、スイッチングとメモリ特性を再生可能にする。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生するのを抑制する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の最短距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下する。キャパシタ上のエッチング開口端形状として鋸刃型などの形状、開口端側面を傾斜形状とする、又はスリットを形成する。

(もっと読む)

デバイス製造方法

【課題】 ノズルから吐出された液滴に変質等が生じないように吐出空間の雰囲気を置換することが可能なデバイス製造方法を提供する。

【解決手段】 デバイスの製造方法は、基板をチャンバ内に搬入して載置台に載置する工程と、待機位置において封止部材により液滴吐出ノズルを隔離した状態で、チャンバの内部を減圧する減圧工程と、ガス供給機構からチャンバ内にパージガスを導入してチャンバ内部の雰囲気を置換するとともに大気圧状態に戻す雰囲気置換工程と、封止部材による液滴吐出ノズルの隔離を解除し、液滴吐出ノズルを吐出位置に移動させて被処理体へ向けて前記液滴を吐出する吐出工程とを含む。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下とする。通常、Hdはキャパシタの形成されていない領域上の絶縁膜表面高さまでとし、Lrはキャパシタ高さの少なくとも4倍とする。

(もっと読む)

情報記憶素子

【課題】多値記録が可能で、アモルファスと結晶との相混合比を制御する方式に比較して、パルス電流条件のマージンが広い情報記憶素子を提供する。

【解決手段】相変化材料にそれぞれ形状の異なるパルス電流を流すことによって、アモルファス状態、微細な結晶粒からなる固相結晶、粒径の大きな結晶状態からなる溶融結晶の3状態を形成し、従来に比較してパルス電流条件のマージンが広く、信頼性の高い多値記録が可能な情報記憶素子を実現する。3状態を形成するには、相変化材料の組成を変更したり、他の元素を添加したりすることによって、溶融後の再結晶化速度および抵抗を制御する。

(もっと読む)

161 - 180 / 3,320

[ Back to top ]