Fターム[5F092AA11]の内容

Fターム[5F092AA11]に分類される特許

21 - 40 / 299

半導体装置の製造方法

【課題】FinFETの特性が均一な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板の上層部分に凹部を形成する工程と、前記凹部内に犠牲材を配置する工程と、前記半導体基板及び前記犠牲材を選択的に除去することにより、一方向に延び、周期的に配列された複数本のフィンを形成する工程と、前記フィン間の空間の下部に素子分離絶縁膜を形成する工程と、前記犠牲材を除去する工程と、前記フィンの露出面上にゲート絶縁膜を形成する工程と、前記素子分離絶縁膜上に、前記フィンを跨ぐように、前記一方向に対して交差した方向に延びるゲート電極を形成する工程と、を備える。

(もっと読む)

プラズマエッチング方法

【課題】CO含有プラズマの条件によらず、安定してクリーニングプラズマを生成する方法を提供する。

【解決手段】被エッチングウェハ802上に形成された磁性膜を、真空容器801内に導入されたCとOの元素を含むCO含有ガスにソース電力を印加することでCO含有ガスをプラズマ化し、生成したCO含有プラズマを用い加工する際に、該CO含有プラズマにて被エッチングウェハ802上に形成された磁性膜に所定の加工を施した後、ソース電力806を印加したまま、クリーニングガスを導入し、その後CO含有ガスの導入を停止することで、所定のクリーニングガスを用いたクリーニングプラズマを生成する。

(もっと読む)

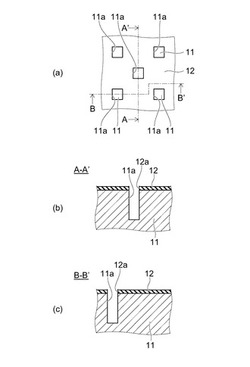

半導体素子の検査処理方法

【課題】磁気センサ等の半導体素子の特性検査から梱包までの一連の作業をトレイを使用することなく効率的に行う。

【解決手段】各半導体素子10をダイシングテープ31上でマトリクス状に並べられた状態に分離する工程と、各半導体素子10をダイシングテープ31毎載置して水平方向及び垂直方向に移動しながらプローブに接触させて検査するプローブ検査工程と、プローブ検査工程を経た後の各半導体素子10をダイシングテープ31上から少なくとも1個ずつピックアップして搬送テーブル32上に搭載し、搬送テーブル32により順次搬送される半導体素子10の第1の主面10aを外観検査する第1の主面検査工程と、第1の主面検査工程を経た後の半導体素子10を把持して反転し、半導体素子10の第2の主面10bを外観検査する第2の主面検査工程と、第2の主面検査工程を経た後の半導体素子10を順次ピックアップして梱包する梱包工程とを備える。

(もっと読む)

エッチング装置及び半導体装置の製造方法

【課題】難エッチング材料を、高速、高精度及び低ダメージでエッチングする。

【解決手段】実施形態に係わるエッチング装置は、上面側に披処理基板19が搭載されるステージ11と、ステージ11の上面側を覆うチャンバー12と、ステージ11の下面側に付加され、開口部を有する下部電極13aと、チャンバー12内にエッチングガスを供給するガス供給部14と、下部電極13aに高周波を印加することにより、チャンバー12内のエッチングガスをプラズマ化する高周波電源部17と、下部電極13aの開口部を介して被処理基板19にマイクロ波を印加することにより、披処理基板19の温度を最適範囲内に設定するマイクロ波発生部15と、ガス供給部14、高周波電源部17及びマイクロ波発生部15を制御する制御部18とを備える。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板の反射率に依存せず、アライメントマークの識別性を確保することができる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、シリコン基板24と、シリコン基板24上に少なくともNiCoパターン31とアルミ電極30とを含んで形成される回路部3と、シリコン基板24上に回路部3のNiCoパターン31と同工程において形成される低反射パターンとしてのNiCoパターン22と、NiCoパターン22上に形成され、回路部3のアルミ電極30と同工程において形成される高反射パターンとしてのアルミパターン20とを有する。

(もっと読む)

不揮発性記憶装置の製造方法

【課題】磁気抵抗効果素子のスピン注入磁化反転特性の劣化が抑制され、製造歩留まりが高い不揮発性記憶装置の製造方法を提供する。

【解決手段】実施形態によれば、複数のメモリセルを有する不揮発性記憶装置の製造方法であって、前記メモリセルのそれぞれは、第1電極を含む下地層と、前記下地層の上に設けられた磁気抵抗効果素子と、前記磁気抵抗効果素子の上に設けられた第2電極と、を有する。前記磁気抵抗効果素子は、記憶層である第1磁性層と、前記第1磁性層の上に設けられたトンネルバリア層と、前記トンネルバリア層の上に設けられ、参照層である第2磁性層と、を含む。前記第2磁性層の表面の一部もしくは前記第1磁性層の表面の一部にイオン化されたガスクラスタを照射して、前記第2磁性層の一部および前記第1磁性層の一部をエッチングする。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】安定して動作可能な磁気抵抗効果素子およびその製造方法を提供する。

【解決手段】実施形態の磁気抵抗効果素子は、下部電極と、第1の磁性層と、第1の界面磁性層と、第2の界面磁性層と、第2の磁性層と、上部電極とを持つ。前記第1の磁性層は前記下部電極上に設けられる。前記第1の界面磁性層は、前記第1の磁性層上に設けられる。前記非磁性層は、前記第1の界面磁性層上に設けられる。前記第2の磁性層は前記第2の界面磁性層上に設けられる。前記上部電極は、前記第2の磁性層上に設けられる。前記第1および第2の磁性層は、それぞれ磁化記憶層および磁化参照層の一方および他方である。前記上部電極は、貴金属と遷移元素もしくは希土類元素の合金層もしくは混合物層、または導電性酸化物層を含む。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法

【課題】単純な方式で集積度が向上し電気的特性が改善された3次元ダブルクロスポイントアレイを有する半導体メモリ素子及びその製造方法を提供する。

【解決手段】本発明の半導体メモリ素子は、互いに異なるレベルに配置され、2つの交差点を定義する第1、第2、及び第3導線と、2つの交差点の各々に配置される2つのメモリセルを備え、第1及び第2導線は互いに平行に延長され、第3導線は延長されて第1及び第2導線と交差し、第1及び第2導線は垂直断面で見た時に第3導線の長さに沿って交互に配列され、第3導線は第1及び第2導線から垂直に離隔される。

(もっと読む)

磁気センサおよびその製造方法

【課題】コンパクトな構成でありながら磁場の検出性能に優れ、かつ容易に製造可能な磁気センサを提供する。

【解決手段】磁化固着層63と介在層62と磁化自由層61とを順にそれぞれ含むと共に、信号磁場によって互いに反対向きの抵抗変化を示す第1および第2のMR素子を備える。ここで、第1のMR素子における磁化固着層63は、介在層62の側から順にピンド層631と、結合層632と、ピンド層631と反強磁性結合するピンド層633とを含むシンセティック構造を有する。このシンセティック構造は、ピンド層633の総磁気モーメントがピンド層631の総磁気モーメントよりも大きなものである。一方、第2のMR素子における磁化固着層63は、単一もしくは複数の強磁性材料層からなる。

(もっと読む)

3軸センサ・チップパッケージに関するシステムと方法

【課題】3軸センサ・チップパッケージためのシステムと方法を提供する。

【解決手段】センサパッケージは、ベース105と、第1のセンサダイ110が、第1のアクティブセンサ回路112および、第1のアクティブセンサ回路に電気的に結合された複数の金属パッド114とを備え、ベースに取り付けられた第2のセンサダイ120が、第1の表面128の上に配置された第2のアクティブセンサ回路122と、第2の表面の上に配置された第2のアクティブセンサ回路に電気的に結合された第2の複数の金属パッド122とを備え、第2のアクティブセンサ回路は、第1のアクティブセンサ回路に対して直交に方位付けされ、ベースに垂直であるように、第2のセンサダイが配置される。第2の表面は、第1の表面に隣接し、第1の表面の面に対して角度がつけられている。

(もっと読む)

磁気抵抗素子の製造方法及び製造装置

【課題】エッチングに用いられるハロゲン系成分による素子の腐食を防止することが可能な磁気抵抗素子の製造装置及び製造方法を提供すること

【解決手段】本発明の磁気抵抗素子10の製造方法は、基板上に強磁性材料からなる第1の強磁性層13を形成する。酸化マグネシウムからなる絶縁層14は、第1の強磁性層13上に形成される。Fe及びCoの少なくとも一方を含有する第2の強磁性層15は、絶縁層14上に形成される。ハロゲン系元素を含むプラズマによるエッチングは、基板11上に第1の強磁性層13、絶縁層14及び第2の強磁性層15が積層された積層体に対して施される。積層体は、H2Oを含むプラズマであるH2Oプラズマに曝露される。

(もっと読む)

スピネルフェライト薄膜の製造方法

【課題】積層構造の中にスピネルフェライト薄膜を配置したスピンフィルタ効果素子において、スピネルフェライト薄膜下部の金属電極層の酸化および下部界面の熱拡散を抑制し、上部界面の大気成分による汚染を排除しつつ、(100)優先配向したスピネルフェライト薄膜を製造する方法を提供する。

【解決手段】基板上に(100)優先配向のスピネルフェライト薄膜を製造する方法であって、前記製造方法は、スパッタリング法でスピネルフェライト薄膜もしくはその前駆体となる薄膜を基板上に形成するスパッタ成膜ステップと、その基板を真空中で加熱する真空加熱ステップとを有することを特徴とするスピネルフェライト薄膜の製造方法。

(もっと読む)

膜形成方法および不揮発性記憶装置

【課題】より良質な膜を形成する。

【解決手段】実施形態の膜形成方法は、下地の上に設けられた酸素及び窒素の少なくともいずれかを含む膜の表面に、酸素及び窒素の少なくともいずれかを含むイオン化されたガスクラスタを照射して、前記ガスクラスタを照射した後の前記膜の密度を前記ガスクラスタを照射する前の前記膜の密度よりも高くする。

(もっと読む)

半導体装置の製造方法

【課題】 信号量の低減を抑制できる磁気抵抗効果によるメモリ素子を具備する半導体装置の製造方法を提供すること。

【解決手段】 コバルト、鉄およびニッケルの少なくとも一つを含む磁性材料を用いた磁気抵抗効果素子を形成する工程を含む半導体装置の製造方法であって、前記磁気抵抗効果素子を形成する工程は、半導体基板1上に、前記磁性材料を含む複数の層4,5,8を具備する積層体3−10を形成する工程と、真空雰囲気中で、塩素を含むガスを用いたプラズマエッチングにより、前記積層体3−10を加工する工程と、前記積層体3−10を加工した後、前記積層体3−10を真空雰囲気中に保持したまま、前記積層体3−10に対してアミノ基を含むガスを用いガス処理を施す工程とを含む。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 界面磁性層が十分に結晶化された磁気ランダムアクセスメモリ及びその製造方法を提供する。

【解決手段】 実施形態に係る磁気ランダムアクセスメモリは、第1の磁性層、第1の界面磁性層、非磁性層、第2の界面磁性層、及び第2の磁性層が順に積層された磁気抵抗効果素子を有する。前記第1の磁性層の下層、前記第1の磁性層と前記第1の界面磁性層との間、前記第2の界面磁性層と前記第2の磁性層との間、及び前記第2の磁性層上のいずれかに第1の金属原子、第2の金属原子、及びB原子を含む金属層が設けられる。

(もっと読む)

磁気メモリの製造方法

【課題】磁化反転に必要とされる電流密度のマージンを広げる。

【解決手段】実施形態に係わる磁気メモリの製造方法は、磁化方向が可変である第1の磁性層16を形成する工程と、第1の磁性層16上にトンネルバリア層17を形成する工程と、トンネルバリア層17上に、磁化方向が不変である第2の磁性層19を形成する工程と、第2の磁性層19上にハードマスク層20を形成する工程と、ハードマスク層20をマスクにして第2の磁性層19のパターニングを行なう工程と、第2の磁性層19のパターニング後に、ハードマスク層20をマスクにしてGCIB照射を行うことにより、少なくとも第1の磁性層16内に磁気的及び電気的に不活性な領域Nonを形成する工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

21 - 40 / 299

[ Back to top ]